在PCB上正确放置去耦电容

描述

我们不时听到客户提出一个很好的问题。将去耦电容器放置在目标IC附近是否重要?一般的经验法则是这样说的,每个PCB设计者都知道这一点,甚至经验不足。

但是,在现实生活中的布线实践中,通常很难在机械限制和电气需求之间找到可接受的折衷方案。特别是如果我们不讲几个简单的片状电容器或一个低功率轨。如果是带有50-100个去耦电容器的BGA封装的FPGA或PHY怎么办?

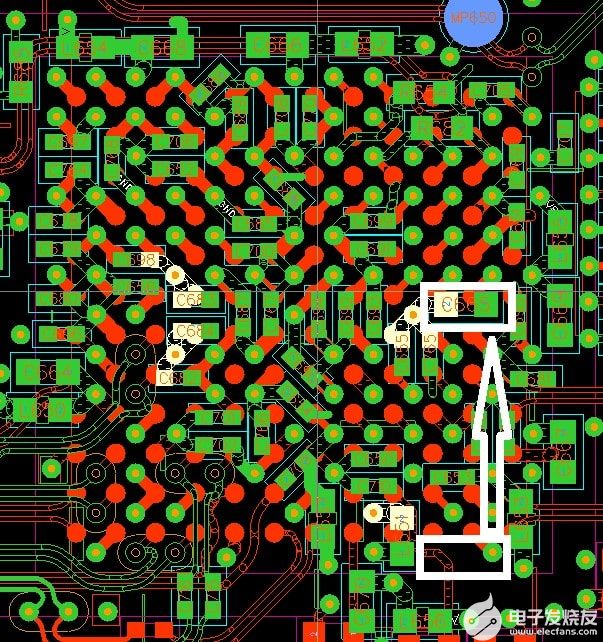

不久前,我们的工程师正在处理一个复杂的PCB项目,其中除其他外,还提出了这样一个意想不到的挑战。板上有一个带有60个去耦电容器的10G以太网PHY。布局设计师试图实现最高质量的设计,他设法将几乎所有电容器都非常靠近板背面IC的相应引脚。但不是所有人。在这种情况下,通常将较小封装和电容的电容器直接放置在引脚附近,而稍大一些的电容器则要稍远一些,但要尽可能接近电路板上的情况。因此,这是在给定项目中解决问题的方式:

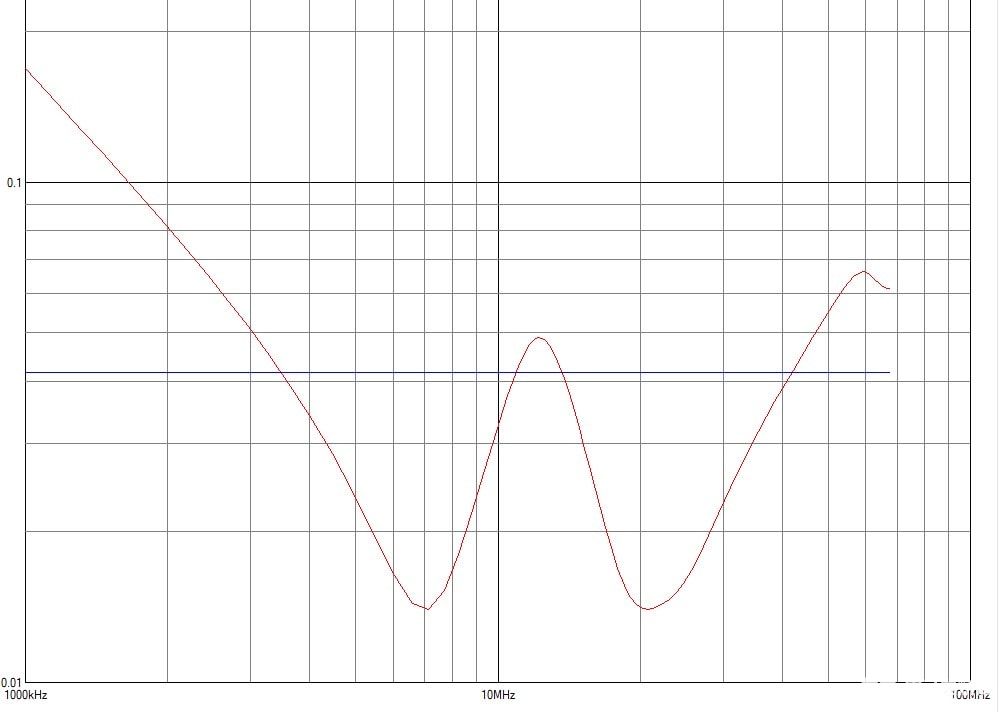

到目前为止,布局看起来还不错。但是,在进行电源完整性分析时在其中一个电源子网中,很明显该电路的阻抗曲线在低频时明显高于目标阻抗。这表明缺少“大”高电容去耦电容器。曲线如下所示:

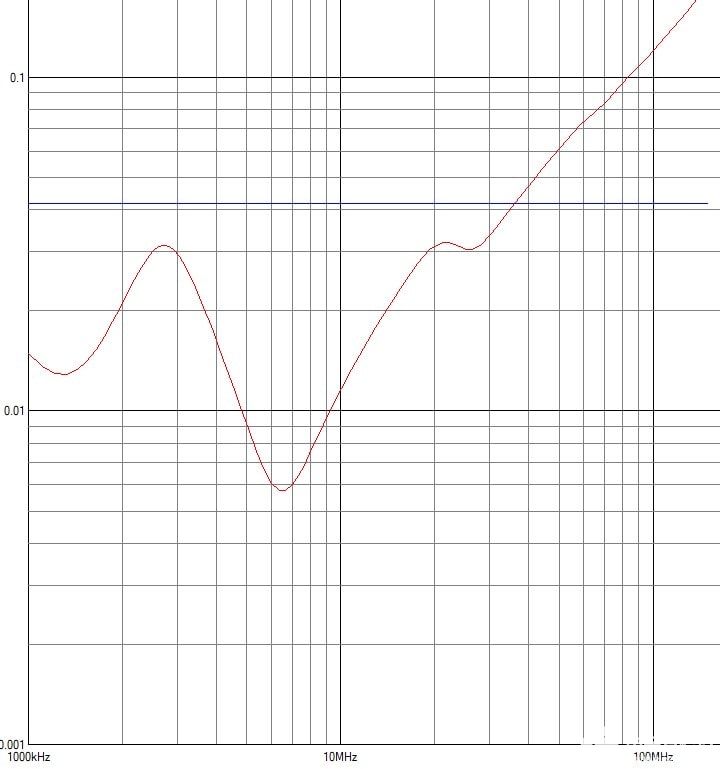

这种情况可能导致以太网PHY电源设备出现问题。分析此问题后,决定稍微重新进行PCB布置,然后将唯一的大电容器移至该子网的三个引脚之一。

加上几个小电容器的电容的微小变化以抑制第二个峰值,此措施可显着改善结果,请参见下图:

即使在此板中,也发现了如上所述的其他一些问题。本文中考虑的示例只是一个特例,清楚地表明了无条件地需要对具有高端IC(例如FPGA或PHY)的电路板以及具有大电流的电路板进行功率完整性分析,从而避免出现实际问题。样品。

另外,我们要强调的是,在实际设计中,即使严格按照制造商的建议执行,也可能存在各种偏差,如果没有适当的SI / PI仿真,这些偏差是无法预测的。

-

详解去耦电容:去耦电容的PCB布局布线2024-03-27 7816

-

PCB去耦电容怎么放置?怎么选择去耦电容?2023-11-29 2600

-

PCB设计时处理去耦电容和旁路电容的注意事项2023-11-21 2771

-

PCB设计的去耦电容器放置指南2023-09-28 3727

-

去耦电容PCB设计和布局详解2023-07-05 2457

-

PCB板去耦电容的大小选择与布置2023-06-15 4611

-

去耦电容分为哪几种?如何去放置去耦电容呢2021-11-03 3856

-

去耦电容器的作用及放置问题2020-12-23 4947

-

去耦电容器应该如何正确放置2020-11-14 5271

-

电容解耦如何放置2020-09-30 4909

-

最有效的去耦电容器放置指南2020-09-29 4986

-

PCB布局时去耦电容摆放经验分享2017-02-09 9506

-

PCB布线技巧之去耦电容的摆放2016-10-26 1438

-

去耦电容在PCB板设计中的应用2009-12-09 44906

全部0条评论

快来发表一下你的评论吧 !