GPIO的内部上下拉电阻_GPIO的驱动能力

电子说

1.4w人已加入

描述

GPIO的电平

大部分CPU/FPGA/CPLD芯片的GPIO都会有独立的电源供电一般会命名为(VCCIO),这样可以灵活接不同的电平标准的芯片。所以在使用GPIO之前先确定两边的电平是否一致或兼容。

GPIO的内部上下拉电阻

内部上下拉电阻,可以提供确定的电平,使得GPIO在使用之前有个确定值以防误操作。正好最近遇到这样的问题。如下示意图。在两边都有内部上下拉电阻的时候,事情就变得有趣了。这条信号上的电平不高不低,当然取决于各自芯片的预留的电阻值。我比较幸运,碰到两边的电阻值大小相等。量到的是1.66V,3.3V的电平。不要小看这个不高不低的电平,可以让这个WIFI有时可识别有时不可。这种概率性的问题是会让人相当地头疼。所以设计时,要看清楚规格书,最好在原理图上标识以免忘记。

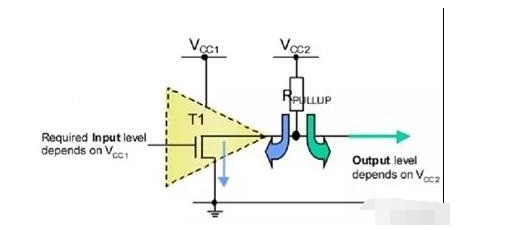

GPIO的OD或OCOD/OC就是说输出的MOSFET/BJT的D极/C极上再芯片内部里不接任何元件。如下图示意示意。

OD/OC的好处:

可以输出同电平,取决于外部电路的电源,如上图的Vcc2。

可以实现线与。

由外部上拉提供电流。当然不能超过GPIO的最大灌电流。

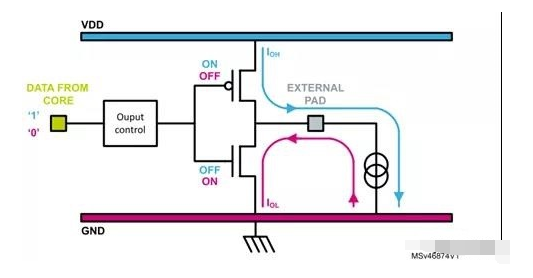

GPIO的驱动能力

主要就是说GPIO能输出多少电流(拉电流)或能输入多少电流(灌电流)。可以看下面这个图,明明白白了。

经常我们会拿GPIO直接去驱动LED 灯,这时就要注意GPIO的驱动能力够不够了,如果不够,就得外加个MOSFET或者BTJ.。

责任编辑人:CC

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请为cx3的io口没有内部上拉电阻或下拉电阻吗?2024-02-28 428

-

上下拉电阻分享2013-07-21 3213

-

stm32之上/下拉电阻对GPIO的影响2018-04-16 7340

-

STM32不同组的GPIO驱动能力有什么差别2018-10-26 6053

-

STM32不同组的GPIO驱动能力有什么差别?2018-12-06 1924

-

STM32不同组的GPIO驱动能力有什么差别呢?2018-12-11 2878

-

GPIO上下拉电阻的设置步骤2019-05-21 3010

-

上下拉电阻的作用2019-07-27 3327

-

用什么芯片可以增强GPIO口的驱动能力2020-05-29 2709

-

gpio驱动能力是什么意思2021-07-22 2329

-

CH32v103的GPIO怎么配置上拉还是下拉?2022-05-18 2071

-

一文快速理解STM32中的上/下拉电阻2021-11-02 14645

-

固件#06--STM32-MCU-GPIO工作模式2021-11-18 758

-

STM32初识及运用—GPIO2021-12-31 767

-

如何提高单片机的GPIO口驱动能力2023-03-24 11592

全部0条评论

快来发表一下你的评论吧 !