从叠DIE的角度介绍Package小型化的方式

电子说

描述

随着电子产品日趋便利化,对产品要求也趋小型、薄型化。即对现有的封装器件要求更小,更薄,而产品本身的内容却又不断在增加。如何在这种矛盾的条件下实现全部要求?这对整个封装行业提出了新的发展。

封装行业小型化发展有CSP、BGA等方向,本文从叠DIE的角度介绍Package小型化的方式。

封装流程Substrate→贴装元件→贴DIE→引线键合→塑封→切割→外观检查→测试→包装

封装形式平面贴DIE方式(图1)平面式

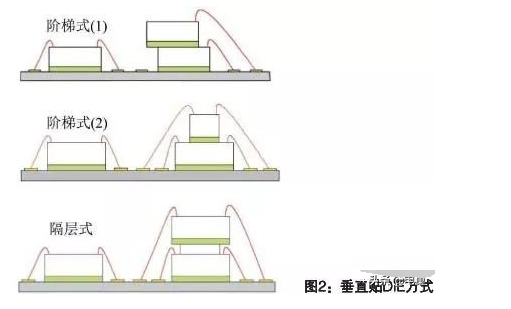

垂直贴DIE方式(图2)DIE之间直接相贴,阶梯式DIE之间间隔一层spacer

两种方式的受限之处平面贴DIE方式:多个DIE布局在同一平面,最大程度的占据了封装空间,难以满足尺寸受限制的条件。

垂直贴DIE方式:阶梯式(1)的叠DIE方式相对平面式的情况有所降低空间利用,但在多层同一类型DIE阶梯时,同样会占据较多空间,因为每递增一层,相当于DIE的尺寸增加约500um,当DIE数量多达8个时,则会增大500×8=4000um的空间。对尺寸紧凑条件,也是难以满足。

阶梯式(2)方式需求所叠层的DIE尺寸比下层的DIE尺寸小,这样才可以让出Wirebonding的空间,应用范围受限。

隔层方式在两层DIE之间增加一层DummyDIE,留出高度用于Wirebonding,增加工艺流程,材料成本,降低UPH。

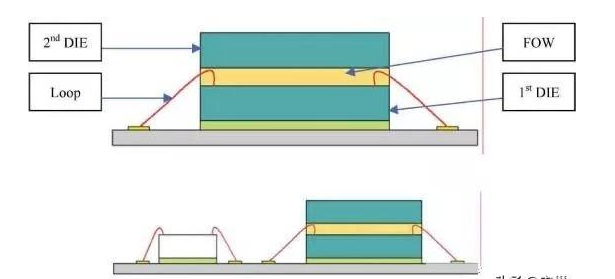

新型贴DIE方式新型的贴DIE方式综合了垂直方式中的两种优势(掩埋式)(图3)。

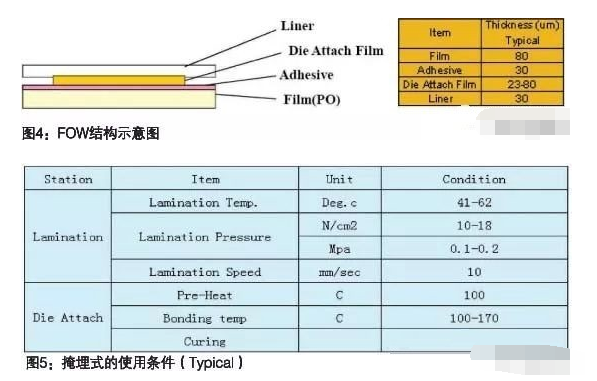

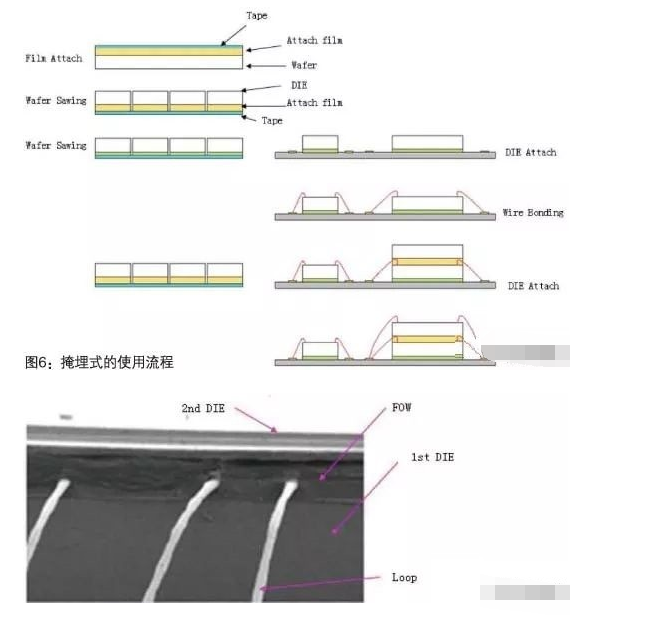

该方式采用一种新型的材料,名称为FOW(filmonwafer,如图4),利用filmattach技术粘附在DIE的bottom面,所粘DIE可直接attach在其它DIE之上,位置没有要求,即可以直接压附着下层DIE的loop。(多个同种DIE可以完全重合在一起,极大缩小了叠DIE占据的空间)

其使用条件、使用流程及效果图分别示于图5~7。

该方式的优势在于多个大小相同的DIE叠加在一起,所占据的空间为一个DIE所占据的空间,大大的节约了水平空间。对size要求严的产品是一个好的选择。size的减小同时也可以减低产品的成本。

叠加多层DIE时,Wirebonding完成后可直接贴装上一层DIE,而不需要增加一个隔层Spacer。缩短生产流程与降低外在因素影响,提高UPH。该方式可有效解决PACKAGE内包含多个DIE,而水平空间又受到约束的情况。随着器件小型化程度加快,此方式的应用也将普及。

责任编辑人:CC

- 相关推荐

- 热点推荐

- P

-

叠层固态电容:小型化封装,释放PCB更多空间2025-12-05 862

-

小型化晶振的影响有哪些2024-11-11 1371

-

实现小型化电源设计的4个小技巧2023-10-17 1373

-

电源小型化2023-06-14 1778

-

坚固的小型化和工业物联网2022-12-30 1357

-

机载计算机电源的小型化设计2021-11-12 1838

-

怎样去解决小型化DC/DC应用设计的问题?2021-04-21 1714

-

小型化的微带双分支定向耦合器设计介绍2019-06-25 4868

-

一款小型化L波段射频收发前端模块的设计过程讲解2019-06-24 2138

-

小型化医疗电子设备2019-05-17 2610

-

SJ MOSFET的效率改善和小型化2019-04-29 2988

-

基于MEMS传感器小型化的设计指南2017-09-18 980

-

无线的小型化的趋势分析2017-09-14 737

全部0条评论

快来发表一下你的评论吧 !