基于DSP TMS320DM642芯片实现运动控制卡的设计

处理器/DSP

描述

目前,视频运动控制卡的研究已经成为热点。本文针对TI公司的视频高速处理芯片TMS320DM642,设计了对目标物体进行视频实时跟踪的运动控制卡。希望通过本文分享DM642平台应用中的一些经验。

1 系统方案与原理

系统主要由视频解码器、CPLD采集控制、TMS320-DM642、视频编码器等部分组成。其总体框架如图1所示。CCD摄像头摄取视频图像,输出标准 PAL制式的模拟视频信号。视频解码器收到模拟视频信号,将其转换为标准格式的数字视频数据流,由CPLD控制视频解码器将数据采集到高速缓存中暂存,避免了数字视频数据长时间占用DSP外部总线。然后DSP的EDMA控制器通过DMA方式从高速缓存中将视频数据搬运到SDRAM中,采集到的视频数据经过 DSP图像处理后,一方面通过视频编码器将图像数据以PAL制式的模拟信号传送给视频转换盒,然后通过USB接口连接PC,显示跟踪结果。另一方面, DSP通过串口发送与目标物体三维坐标相关的控制命令,从而控制驱动器操纵舵机,实现对目标物体的跟踪与抓取。

2 图像采集的CPLD控制

系统采用CPLD控制视频解码器SAA7111A采集图像数据,送到高速缓存。SAA7111A芯片提供了很多同步信号来实现系统工作同步,逻辑控制器对这些信号进行逻辑运算,完成同步控制。

图2为控制图像采集的逻辑框图。其中虚线框部分由CPLD完成。CPLD上电后,首先使D触发器输出为高电平,控制FIFO写信号或门中的1路信号为高电平,这样FIFO写信号禁止,从而关闭图像采集开关。行计数器和像素计数器处于等待计数状态。待DSP、SAA7111A、EDMA和FIFO初始化完成后,由DSP发出启动图像采集的信号。在VREF为高电平且HREF为所要行时,行计数器开始计数,达到512行时行计数器复位。同时,在HREF为高电平且像素是想要的像素时,像素计数器开始计数,并在达到512个像素时计数器复位。经过SAA7111解码得到的PAL制式的图像最大分辨率为720× 576,要求采集的图像大小为512×512像素,只取其中部分像素。SAA7111A的像素时钟LLC2频率为13.5 MHz,作为CPLD的工作时钟。由SAA7111A的时序图可知,输出图像分为奇偶单场。奇偶单场中的VREF高电平都对应行有效,单场为288行 (288个HREF);输出VREF低电平表示场消隐信号,为25行(25个HREF)。由于单场为256行,要求采集图像为512行,所以不采集单场有效行的前16行和后16行图像数据。此处设计行计数器是用来达到取中间256行有效像素的目地。图3为采集一场图像的时序仿真图。同样,输出的HREF高电平表示1行有效像素,为720个LLC2周期,每行要求只采集中间的512个像素。因此编写像素计数器,目地是在HREF上升沿出现后,取中间的512 个像素作为有用的像素。

3 DSP的软件系统设计

3.1 双目视觉算法

本文所采用的摄像机的空间关系如图4所示。假设C1与C2摄像机的焦距相等,各内部参数也相等,且2个摄像机的光轴平行,x轴重合。由于光轴与图像平面垂直,故2个摄像机的图像坐标系x轴重合,y轴平行。因此,将第1个摄像机沿其z轴平移一段距离后与第2个摄像机完全重合。

当双摄像机这样配置时,2个摄像机坐标系只相差x轴方向上的1个平移,将平移距离1记为b。

如图4所示,O1O2为C1及C2坐标的x轴。PO1O2平面与2个图像平面I1及I2的交线分别为E1和E2。由于2个图像平面位于同一平面,则E1与 E2为该平面上的同一直线。又由于图像平面平行于x轴,故E1和E2与x轴平行。P1和P2分别为O1P与I1,及O2P与I2的交点,则P1与P2分别在E1和E2上。事实上,一幅图像上的任一点,在另一幅图像上的对应点只可能位于1条特定的被称为极线的直线上,而E1和E2就是此系统的2条极线。

假设C1坐标系为x1y1z1,C2坐标系为x2y2z2。在上述摄像机配置下,若任何空间点P的坐标在C1坐标系下为(x1,y1,zz),在C2坐标系下为(x1-b,y1,z1)。由中心摄影的比例关系可得:

可见,由P1与P2的图像坐标(u1,v1)、(u2,v2)可求出空间点P的三维坐标x1、y2、z1。

上述公式组中,b称为基线(baseline)长度,(u1-u2)称为视差(disparity)。分析表明,基线长度越长,x1、y1、z1的计算相对误差越小。但基线长度不可太长,否则,由于物体各部分的互相遮挡,2个摄像机可能不能同时观察到P点。视差是由于双摄像机位置不同,使P点在图像中投影点的位置不同引起的。由z1式可见,P点的距离越远(即z1越大),视差越小。事实上,当P点趋于无穷远时,O1P与O2P趋于平行,视差趋于零。

3.2 嵌入式实时系统DSP/BIOS设置

本文对嵌入式实时系统DSP/BIOS的配置分为4个部分:

①系统设置。配置系统的存储器为外部SDRAM,并指定存储地址。

②实时分析。指定调试函数,用于记录系统运行时间和调试结果。

③任务调度。采用RF5框架,定义了4个执行任务,分别完成视频输入、处理、控制、输出。

④同步控制。用于完成上位机对目标物体的设定。

系统DSP/BIOS设置如图5所示。

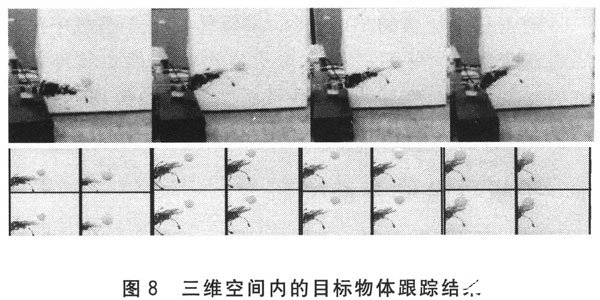

图8中第1行为视频跟踪卡应用在由舵机搭建手臂上,对三维空间小球的实时跟踪效果图。第2行为视频控制卡反馈回PC机的4路图像:第1路为左摄像头拍摄的真实图像,第2路为右摄像头拍摄的真实图像,第3路为对第1路图像中的小球进行颜色识别后图像分割的效果图,第4路为对第2路图像中的小球进行颜色识别后图像分割的效果图。

结语

本文设计的视频检测运动控制卡,可以在三维空间内准确定位目标物体,同时采用动态跟踪的方式对目标物体进行夹取。采用DSP与CPLD相结合的方式,并嵌入实时DSP/BIOS操作系统,提高了系统对视频处理的速度。该系统定位准确,功耗低,适合应用于移动机器人等领域。

责任编辑:gt

-

TMS320DM642 EVM OSD FPGA用户指南2024-12-24 477

-

TMS320DM642至TMS320DM6437迁移指南2024-10-15 361

-

从TMS320DM642迁移至TMS320DM648/DM64372024-10-14 483

-

怎么实现基于TMS320DM642视频采集驱动开发?2021-06-08 2374

-

基于TMS320DM642多媒体芯片实现视频监控系统的应用方案2021-03-17 4832

-

基于TMS320DM642视频采集驱动开发2019-02-03 1158

-

如何从进行TMS320DM642到TMS320DM6467的迁移2018-04-18 1539

-

TMS320DM642中文资料2017-04-24 1374

-

TMS320DM6422016-12-05 7501

-

TMS320DM642中文手册2016-08-05 877

-

TMS320DM642-500,pdf(Video/Imag2010-12-05 476

-

基于TMS320DM642的视频采集卡设计2010-12-03 1266

-

基于DSP TMS320DM642的H.264视频编码的实现2009-09-11 926

-

TMS320DM642 pdf datasheet2008-08-07 1612

全部0条评论

快来发表一下你的评论吧 !