用Elaborated Design优化RTL的代码

描述

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

通常情况下,我们总是习惯了打开综合后的设计,执行诸如

report_timing

report_timing_summary

report_design_analysis

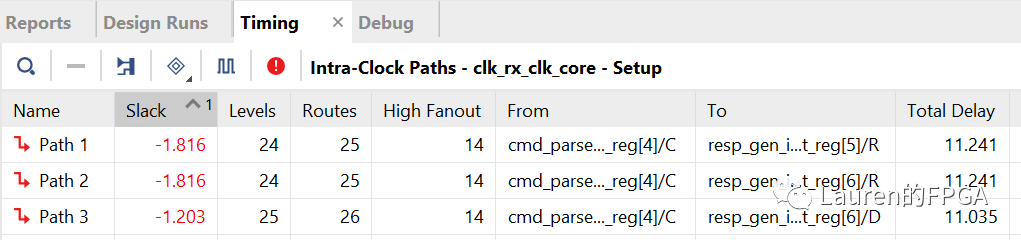

等命令分析时序,却忽视了RTL代码层面的优化。通过这些命令找到关键路径之后,一个重要的步骤是检查这些路径上的逻辑单元是否很好地映射到FPGA器件中。如果没有,就要尝试通过修改RTL代码、使用综合属性(Synthesis Attribute)、设置综合选项、使用BlockLevel综合技术或者使用不同的综合策略优化RTL代码,使得在综合之后时序能够达到一个较好的结果。这对于逻辑级数较高的路径尤为重要。因为高逻辑级数的路径会对后期布局布线带来很大的压力,同时成为设计整体性能提升的瓶颈,更明显的是改善高逻辑级数路径的常用且有效的方法是插入流水寄存器以降低逻辑级数,这一工作在设计初期完成最为快捷,越是在设计后期越难以做这一工作。

在Vivado Project模式下,同时打开Synthesized Design和ElaboratedDesign。在Synthesized Design下对设计进行分析,找到设计的关键路径,生成相应的时序报告,如下图所示。选中图中的时序路径,按下F4,会生成该路径对应的Schematic视图,同时还可以看到路径上的逻辑单元(cell)和单元之间的连线(net)都已被选中。此时切换到Elaborated Design,按下F4,可看到这条路径在Elaborated Design下的Schematic视图。这时候就可以检查这条路径的RTL逻辑单元,尤其是注意执行了哪些操作、数据位宽是否合理。

责任编辑人:CC

-

英诺达推出RTL功耗优化工具2025-03-20 1315

-

优化 FPGA HLS 设计2024-08-16 1117

-

优化FPGA HLS设计2023-10-30 1532

-

从可综合的RTL代码的角度聊聊interface2023-10-12 3413

-

Cadence 推出 Joules RTL Design Studio,将 RTL 生产力和结果质量提升到新的高度2023-07-17 1909

-

RTL级设计的基本要素和步骤是什么2023-01-17 11574

-

怎么解决Conformal做RTL和netlist的形式验证时综合优化的电路也会报不相等?2022-08-09 21988

-

如何在不改变RTL代码的情况下,优化FPGA HLS设计2020-12-20 2618

-

来自vivado hls的RTL可以由Design Compiler进行综合吗?2020-04-13 2760

-

怎么利用Synphony HLS为ASIC和FPGA架构生成最优化RTL代码?2019-08-13 2668

-

RTL功耗优化2017-09-11 1060

-

RTL级代码和仿真代码的区别2012-07-21 10452

全部0条评论

快来发表一下你的评论吧 !