ADI技术:应对有线电视基础设施下游发射器挑战

通信网络

描述

作者:Simon Whittle,ADI 技术项目经理

摘要

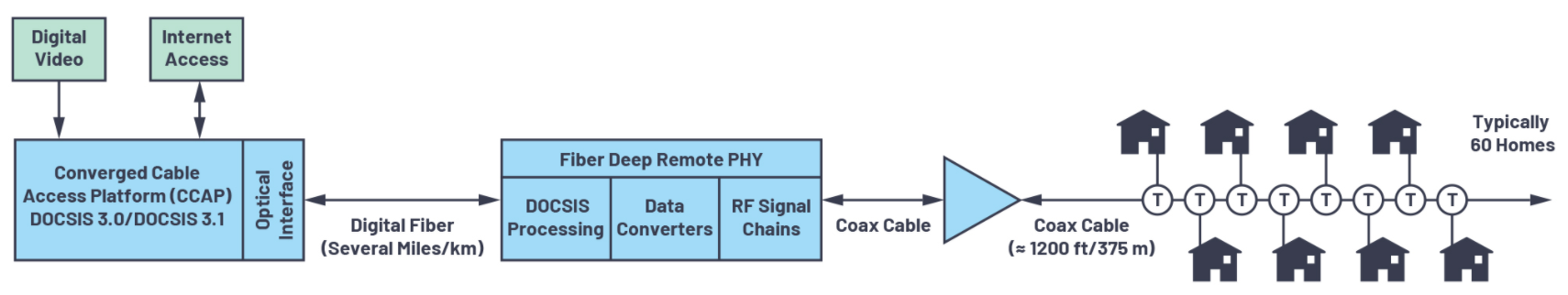

针对用户需要更快互联网连接的趋势,有线电视行业已开发新的网络架构,以便为用户提供数Gb服务。该光纤深入方法采用远程PHY设备(RPD),通过使用数字光纤将关键硬件移到更靠近用户的位置。这可与无线(蜂窝)网络中的远程射频头相媲美,可节约空间,减少前端散热,但也为远程设备带来了新的设计挑战。

虽然有线电视信号绝对频率较低,但其带宽比无线信号宽得多,从108 MHz到1218 MHz扩展了几个倍频程,并具有多个带内谐波。RPD让设计人员面临诸多挑战,包括RF和混合信号硬件必须涵盖更宽的频率范围,具有更高的RF功率、更低的底噪和更好的线性度,同时消耗更少的直流功耗。每个下行末级RF放大器的功率通常为18 W,对于4端口系统,这大约是通常能够提供给RPD(由RPD消耗)的140 W至160 W功率预算的50%。

将ADI的有线电视数字预失真(DPD)效率增强技术,应用于DPD优化功率倍增器(ADCA3992),并结合先进的高速数据转换器技术,利用单个DAC(例如AD9162)和单个ADC(如AD9208), 以及高度集成的时钟解决方案(HMC7044),来实现全频带DPD。

本文介绍远程PHY的演进,以及ADI公司如何使用专有DPD并将ADI的算法和IP内核集成到OEM的现有FPGA部署中来解决效率和线性度挑战。

背景知识

自从60多年前作为社区接入电视(CATV)引入,有线电视已从简单的单向(仅下行)模拟链路发展为复杂的多模、多频道双向系统(包括上行或反向路径),支持模拟电视、基于IP的标清(SD)和高清(HD)数字电视以及高速数据互联网下载和上传。这些服务由多个系统运营商(MSO)提供。

有线数据和数字电视服务把使用CableLabs及相关参与公司制定的有线电缆数据系统接口规范(DOCSIS)的数据提供给消费者。前端系统(电缆调制解调器终端系统或CMTS)的配置经过了多次演进,包括添加EdgeQAM调制器作为独立单元,或与CMTS集成为有线电视融合接入技术平台(CCAP)的一部分。对下行数据容量的需求现在正以约50%的复合年增长率(CAGR)增加,这意味着需求约每21个月翻一番。1为了满足这种需求,自从1997年发布DOCSIS 1.0以来,下行数据速率已从40 Mbps增加到1.2 Gbps(通过广泛部署实施DOCSIS 3.0)。

这些下行数据速率的提高通过结合使用多项技术来实现,包括频道绑定、更复杂的调制(从64 QAM移至256 QAM)和更高的下行频率上限(从550 MHz至750 MHz至1002 MHz)。在美国,所有这些都是在保留传统模拟电视服务6 MHz频道规划的情况下实现的(EuroDOCSIS和C-DOCSIS为8 MHz),但为了支持高达10 Gbps的下行速率,有必要做出更根本的改变,于是在2013年,发布了DOCSIS 3.1标准。在保留对传统标准支持的同时,DOCSIS 3.1采用频谱效率更高的正交频分多路复用(OFDM)技术,频道带宽高达190 MHz,支持高达4096 QAM。此外,下行频率范围的频率上限增加了超过20%,达到1218 MHz,并可选择扩展到1794 MHz。

但有一点始终没有改变,都是使用具有75 Ω阻抗的同轴电缆物理连接到用户电缆调制解调器。在20世纪90年代之前,系统前端和用户之间使用100%同轴电缆,但最新部署为混合光纤铜缆(HFC)。在HFC中,模拟电光转换器连接到前端的同轴输出;然后信号通过光纤传输至靠近服务区的节点,再通过光电转换器,最终经同轴电缆分配给用户。通过架空或地下电缆与用户的这最后一英里连接成为系统瓶颈,但升级到光纤到户(FTTH)链路的成本很高且具有破坏性,因此有线电视MSO决定充分利用现有的同轴电缆资产。与双绞线电话线相比,同轴电缆提供了一个相对良好的环境,本身能够屏蔽干扰或串扰,并且因阻抗不匹配产生适度的信号反射。但是,从节点到最远用户达1200英尺的典型距离下,频率相关损耗特征明显(108 MHz和1002 MHz之间存在近17 dB的斜率),需要插入具有高通响应的RF滤波器进行预加重或倾斜。

在典型的HFC部署中(如图1所示),从光纤节点连接的一根主干同轴电缆可服务数百个用户,通过多路RF分路器将信号分配给子组,然后通过分接头将分接电缆连接到个人用户。在典型的节点+ n系统中,宽带升压放大器以固定的间隔插入网络中,以放大信号电平,确保电缆调制解调器处具有足够的信噪比(SNR)。

为用户提供更大的数据容量

DOCSIS干线电缆上的可用数据带宽由所有连接用户共享,并可通过两种方式为所有用户提供更多带宽:

► 提高通过电缆传输的数据速率

► 减少连接到电缆的用户数量

如前所示,通过使用频道绑定、更高阶的调制方案以及扩展频谱以提供更多的频道,可提高关键信息(headline)数据速率。但是,增加下行容量只是解决方案的一部分,因此,网络架构也在不断发展以减少连接到节点的用户数量,最初是通过节点分割来实现的,将支持的用户数量从最多2000减少到不足500。这种方法有效但成本很高。节点分割的替代方法是修改网络架构,通过使用带数字光纤链路的分布式接入架构(DAA)将物理层(PHY)与CCAP分离,如图2所示。远程PHY硬件包含下行调制和RF级以及上行RF级和解调。从CCAP中移除体积庞大且耗电的PHY组件,在前端位置放一个边缘路由器也能实现虚拟CCAP。

数字光纤的性能远远高于模拟光纤,且覆盖范围更大(能够更灵活地确定节点位置),并且单根光纤支持大约5倍的波长。DAA方法还消除了传统HFC网络中的电光和光电转换。这些转换限制了光节点输出信号的动态范围:模拟转换的底噪和线性度都会影响调制误差率(MER),这将决定是否能够支持高数据速率所需的高阶调制。

挑战是什么?

光纤深入架构将通过更小的服务组规模、更自由的频谱分配和更好的线路末端SNR和MER(DOCSIS 3.1中实现高阶调制所必需的),来提升每个用户的容量。由于数字光纤和新硬件的位置相对靠近用户,因此还有机会提供补充服务节点,如在远程PHY节点上添加Wi-Fi接入点。但是,这也会给下行模拟传输链带来几个新的设计挑战。

图1.使用HFC部署有线电视

图2.使用远程PHY部署有线电视

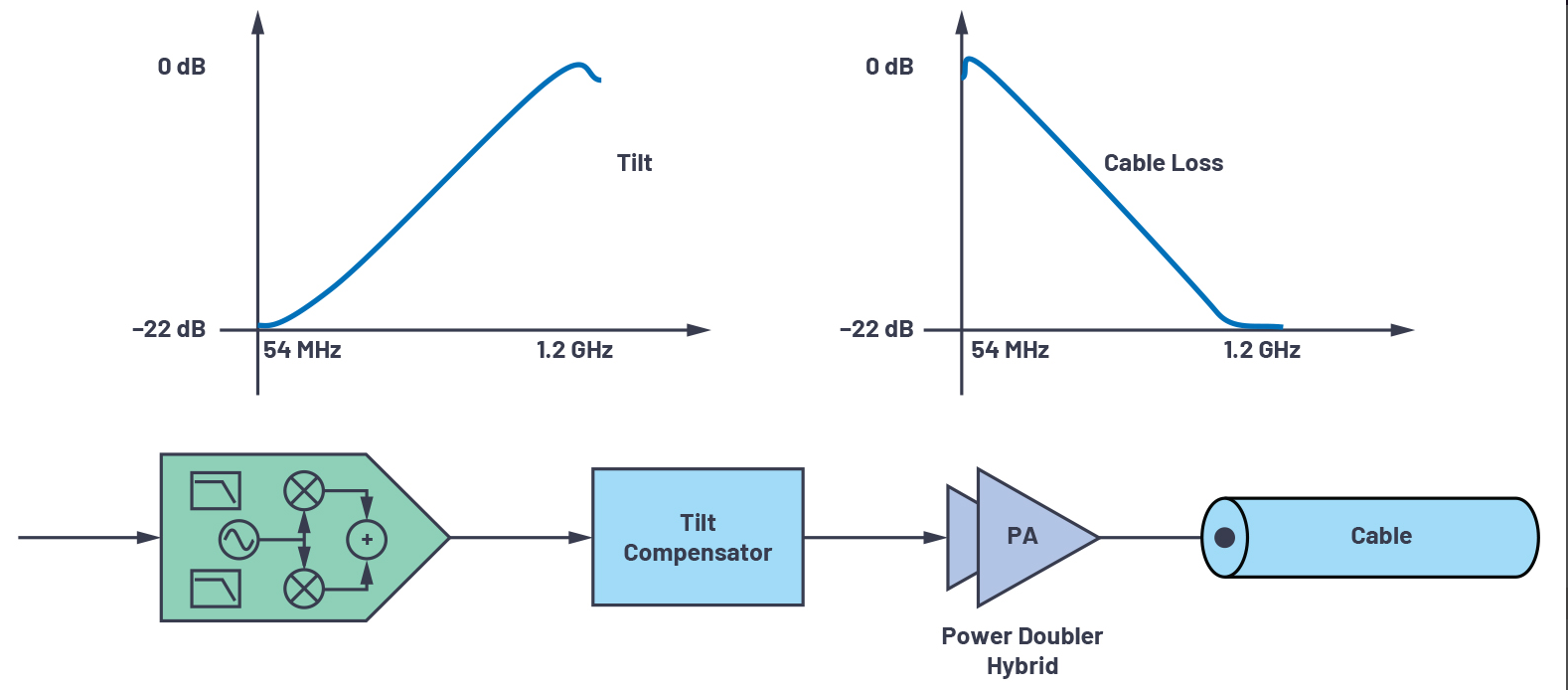

DOCSIS 3.1标准将下行频率上限从1002 MHz扩展到1218 MHz,意味着必须传输相当于35个额外的6 MHz频率通道,且向上倾斜度从17 dB增加到21 dB,如图3所示。

任何新系统都需要与现有部署保持兼容,因此最高DOCSIS 3.0频道中的功率(以999 MHz为中心)必须保持不变(通常为57 dBmV),这意味着最高频道(以1215 MHz为中心)中所需的RF功率为61 dBmV。由于添加了频道,增加了倾斜度,并且电缆调制解调器需要高SNR,因此节点输出端口前的最后一个有源元件,即A类超线性功率放大器(功率倍增器混合)所需的输出信号电平提高了一倍多,达到76.8 dBmV的复合电平。为了满足不断增长的RF功率需求,混合硬件设计人员必须将每端口混合直流偏置功率从10 W左右增加到18 W,并且在某些情况下,必须将直流电源电压从行业标准值24 V增加到34 V。由于节点通常支持多达4个RF端口,每个端口都有其自己的混合端口,并且通常由通过同轴电缆注入的60 V交流电源供电,这就迫使对设计做出重大更改,并产生了新的散热管理问题。

为了支持采用DOCSIS 3.1的更高阶QAM方案,节点输出端对MER的苛刻要求已从43 dB增加到48 dB。2在这样高的MER要求下,DAC时钟上的相位噪声和杂散信号会对系统性能产生影响。功率倍增器直接影响MER和带内带外失真的主要不利因素是非线性失真,包含谐波和交调失真。在108 MHz至1218 MHz的倍频程工作范围内,存在多个带内奇偶次谐波,而在185个D3.0载波(或等效载波)下,会产生一组非常复杂的IM产物。倾斜也有显著的影响,因为较高频道中的功率比最低频道中的功率大100多倍,所以这里会产生显著的差频积。峰均功率比(PAPR)超过12 dB。

所有这些因素结合起来,为功率倍增器设计人员带来了巨大的挑战:更宽的带宽、更高的峰均功率以及改善线性度。最新的A类GaAs/GaN推挽混合器件(如ADCA3992)可满足带宽、RF功率和线性度要求,但RF系统设计人员所面临的挑战无疑是降低功耗:650 mW的RF输出功率的直流输入约为18 W时(等效于76.8 dBmV复合电平),直流到RF的转换效率仅为3.6%。

系统解决方案是什么?

一旦混合设备能够支持所需的带宽和功率,解决方案的第一部分就是确保输出端口前的最后一个有源元件,即混合功率倍增器能够获得清晰的信号。通过使用高性能宽带16位RF DAC(如AD9162)和低相位噪声、低杂散辐射JESD204B兼容时钟源(如HMC7044),可在DAC输出端跨整个DOCSIS 3.1频率范围实现约52 dB MER。

解决方案的第二部分更复杂。理想情况下,任何解决方案都会既提高功率倍增器的输出功率能力又提高MER,同时降低功耗,但它们几乎是相互对立的:在恒定输出功率下,降低功耗会使MER性能下降,或者需要损失RF功率性能,才能使MER保持不变。虽然可以使用包络跟踪(ET)等技术来提高效率,但创建非常宽的带宽包络信号并将ET过程产生的显著失真线性化将带来额外的挑战。

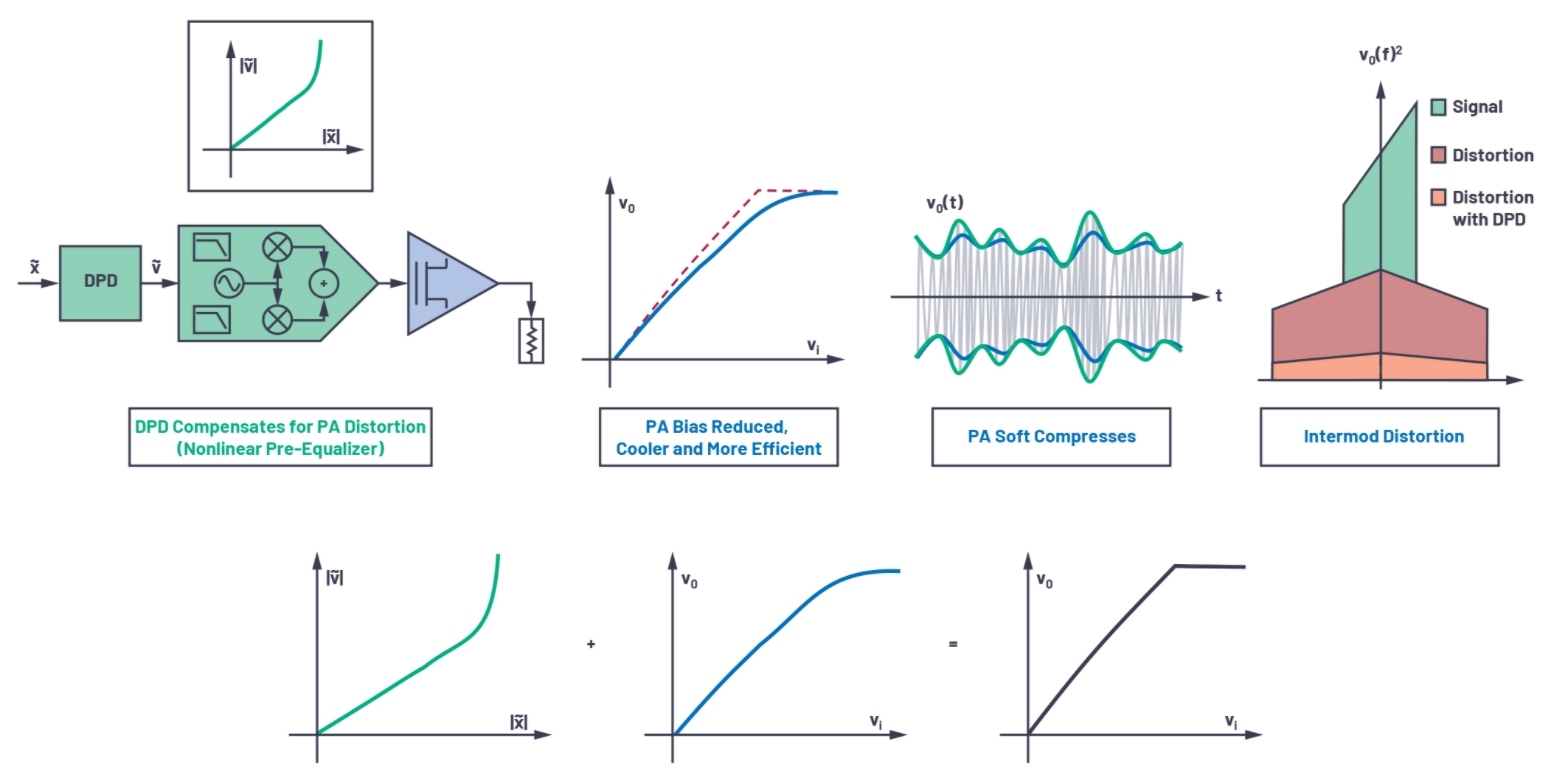

要兼顾效率和MER,具有吸引力的解决方案就是DPD,整个无线蜂窝行业几乎普遍采用。数字预失真(DPD)允许用户在更高效但非线性更明显的区域中运行混合功率倍增器,然后先预先校正数字域中的失真,再将数据发送到放大器。如图4所示,DPD在数据到达放大器之前对其进行整形,以抵消放大器产生的失真,从而扩大功率倍增器的线性范围。

图3.频率相关电缆损耗的倾斜补偿

图4.数字预失真

在扩大的线性工作范围中,DPD让放大器能够在降低的偏置电流或电源电压下更自由地运行(从而降低功耗),或提高MER和误码率(BER),甚至可能同时兼顾。尽管数字预失真已广泛应用于无线蜂窝基础设施,但在电缆环境中实施数字预失真有独特而又有挑战性的要求。这包括对超宽带宽应用线性化,尽量减少实施DPD所需的数字信号处理功耗,以及在高倾斜频谱下工作。所有这一切只能通过对硬件、FPGA和软件进行适度的更改(会增加成本)来实现。

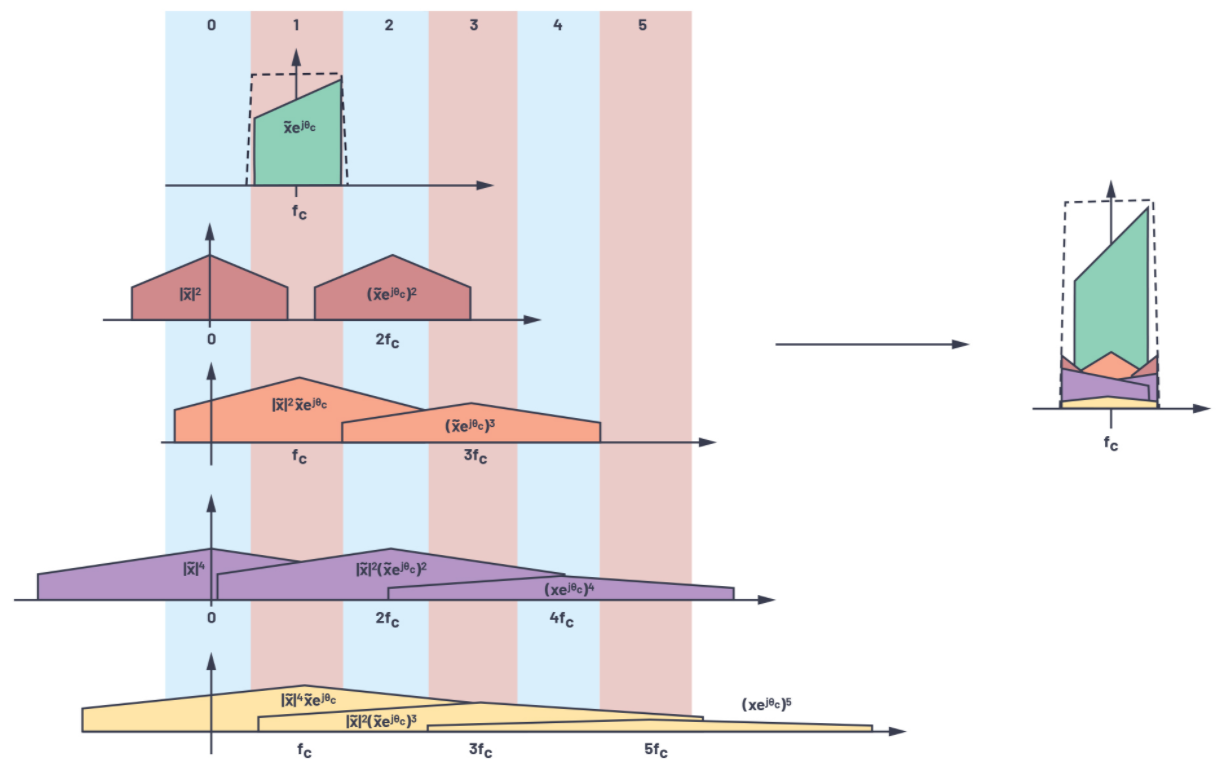

由于通过将放大器驱动到非线性工作区域来提高效率,多个带内失真产物给DPD带来了独特的挑战。不仅是大信号带宽,还有它在频谱(从直流开始仅为108 MHz)上的位置都对DPD构成了挑战。有线信号的性质与无线截然不同,无线信号其所需信号的带宽(例如,60 MHz)比RF中心频率(例如,2140 MHz)小很多。在典型的108 MHz至1218 MHz DOCSIS 3.1下行分配中,所需信号带宽为1110 MHz,中心频率为663 MHz。所有非线性系统都会发生谐波失真。电缆数字预失真的重点是带内谐波失真产物。在典型的无线系统中,三次和五次谐波最重要,因为其他产物在频带外,可通过传统滤波器滤除。在典型的电缆部署中,最低载波的前11个谐波都在频带内。

相比只需要考虑奇数次谐波的无线蜂窝应用,电缆应用中的偶数次和奇数次谐波均在频带内,可产生多个重叠的失真区域。这在一定程度上会对任何数字预失真解决方案的复杂性和精密性产生严重影响,因为算法必须通过简单的窄带假设。数字预失真解决方案必须适应所有阶次的谐波失真。每个阶次k需要[k/2] + 1项(二阶:k = 2 → 2项,三阶:k = 3 → 2项,四阶:k = 4 → 3项等)。在窄带系统中,偶数阶项可以被忽略,奇数阶在每个目标频带内产生1个项。电缆应用中的数字预失真必须考虑奇数阶和偶数阶谐波失真,并且还必须考虑到每个阶可能有多个重叠的带内元素。

谐波失真校正定位

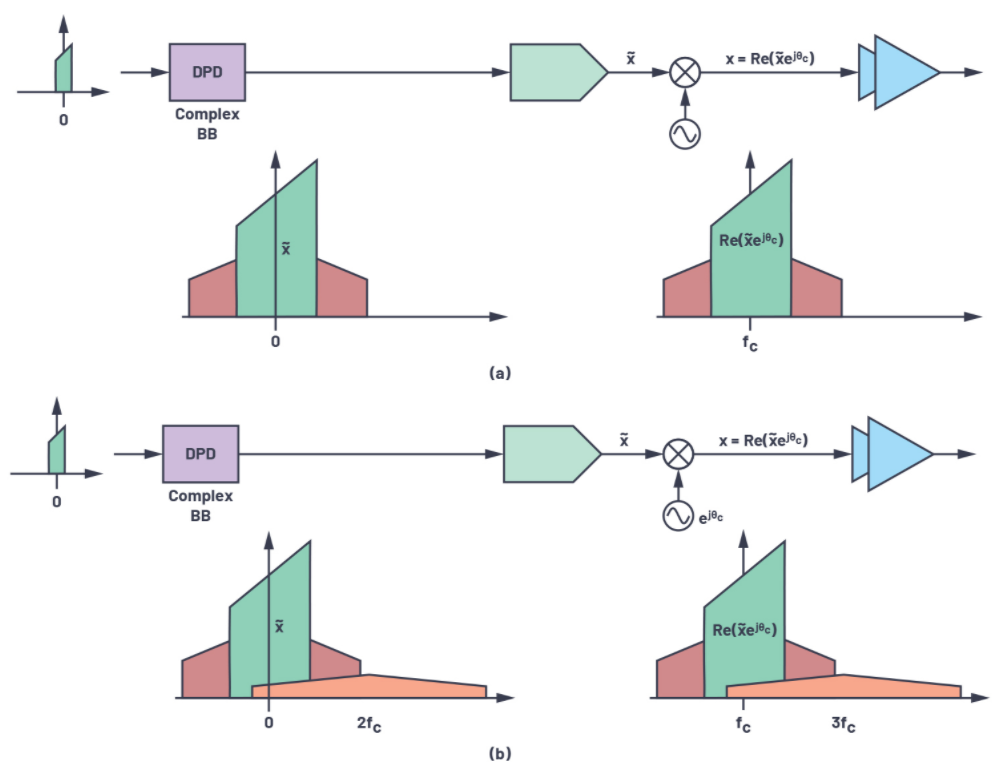

考虑到传统窄带数字预失真解决方案的处理在复杂的基带处完成,我们主要关注对称位于载波周围的谐波失真。在宽带电缆系统中,尽管保持了位于一次谐波周围的那些项的对称性,但是这一对称性不再适用于更高阶次的谐波产物。

图5.宽带电缆应用中宽带谐波失真的影响

如图6a所示,传统窄带数字预失真在复杂基带处完成。在这些实例中,仅一次谐波产物在频带范围内,因此其基带产物直接转换为RF。考虑宽带电缆数字预失真时(图6b),较高阶次的谐波失真必须是频率偏移,才能使上变频后的基带产物正确位于实际RF频谱中。

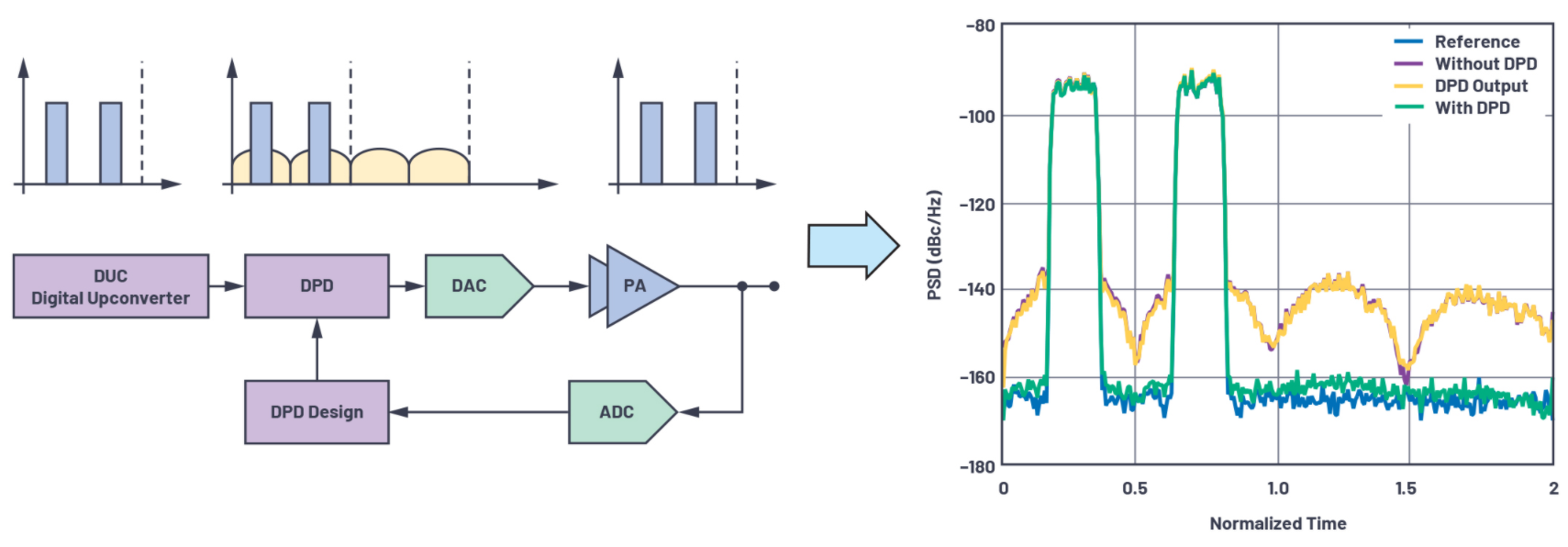

图7概要显示了一种数字预失真的实现。在理想情况下,从数字上变频器(DUC)(通过数字预失真)到DAC乃至通过功率倍增器的路径将没有带宽限制。同样地,观测路径上的ADC将对全带宽进行数字化。请注意,为了进行说明,我们扩展2倍带宽的信号路径;在某些无线蜂窝应用中,可扩展到3至5倍的带宽。理想方案是通过数字预失真产生带内项和带外项,从而完全消除功率放大器引入的失真。需要注意的是,为了准确消除失真,需要在目标信号的带宽之外创建项,这一点非常重要。在实际方案中,信号路径具有带宽限制和倾斜特性,数字预失真性能无法达到理想方案要求。

ADI公司开发了一个完全实时、闭环、自适应电缆数字预失真解决方案,由FPGA结构中的执行器和嵌入式处理器中基于软件的自适应机制组成。该实现方案使用Intel® Arria® 10 660 FPGA和嵌入式ARM® Cortex®处理器。DPD IP内核和ARM的功耗为5.3 W,尽管使用更新一代的FPGA或转换为ASIC,此功率仍应低于3 W。

图6.宽带数字预失真复杂基带处理中的频率偏移要求。(a) 传统窄带数字预失真在复杂基带处完成

(b) 宽带电缆数字预失真、OOB HD必须是频率偏移以允许RF上变频

图7.无带宽限制的理想化数字预失真方案

结果

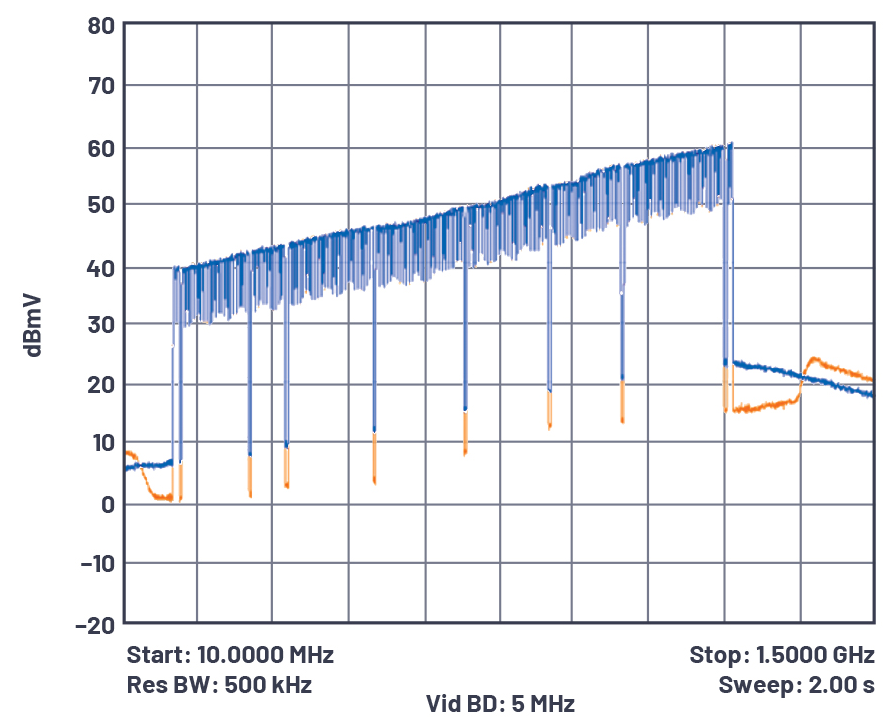

图8显示ADCA3992在76.8 dBmV总复合电源、34 V电源电压、400 mA偏置电流(13.6 W直流电源)下工作的测试结果。

图8.ADCA3992在76.8 dBmV下没有数字预失真(蓝色)和有数字预失真(橙色)时的性能

测试信号是一串DOCSIS 3.0载波,中心频率为111 MHz至1215 MHz,倾斜度为21 dB。引入了少量的间隙,以便观察频带失真。可以看到,频带底部失真约改善了6 dB,频带顶部超过8 dB。

与530 mA标称非数字预失真功率倍增器电流相比,直流电源节省4.4 W,那么,4端口系统节省的总功率为17.6 W减5.3 W FPGA电源,得到12.3 W。对于72 W至59.7 W的4端口系统,功耗(散热)显著降低。每个倍增器的偏置电流很可能进一步回退至350 mA (11.9 W),同时仍达到41 dB的MER目标值,从而系统净节省19.2 W。

结论

尽管高速移动数据和光纤日益得到广泛应用,但现有最后一英里网络的巨大覆盖范围及其相对良好的电气特性,可确保在可预见的未来,它们仍将是向消费者提供语音、视频和数据服务的重要工具。随着有线电视网络过渡到DOCSIS 3.1,并且不断地发展,满足更宽的频率范围、更高的功率、更好的调制精度以及更高的功效等系统性能要求变得更加困难。

数字预失真提供了一种可解决这些相互冲突需求的方式,但在电缆应用中的实施也构成了非常独特和极具难度的挑战。ADI已开发出一套全面的系统解决方案来应对这些挑战,其中包含混合信号硅(DAC、ADC和时钟)、RF功率模块(GaN/GaAs混合)和先进算法。这三种技术的结合为设备制造商提供了一个灵活的高性能解决方案,能够以最小的妥协在功耗与系统性能之间实现平衡。软件定义线性化还支持原有电缆技术到新一代电缆技术的轻松过渡,新一代电缆技术中预计将包含全双工(FD)、扩展带宽(至1794 MHz)和包络跟踪(ET)。

本文借鉴了Patrick Pratt的数字预失真图,笔者对此表示感谢。

参考资料

1 Robert L. Howald。“光纤前沿。”春季技术论坛论文集,2016年。

2 有线电缆数据服务接口规范,DOCSIS® 3.1—物理层规范:CM-SP-PHYv3.1-I08-151210。CableLabs,2017年5月。

作者简介

Simon Whittle是通信业务部门无线系统部的技术项目经理。工作地点在英国巴斯,主要负责有线电视和5G毫米波系统项目。在2012年7月加入ADI之前,Simon曾在蜂窝通信基础设施行业工作,负责领导团队开发3G和4G远程射频头技术。在此之前,他从事蜂窝、移动无线电和广播应用的接收器和高功率发射器开发工作,并拥有多项专利。他于1983年毕业于英国萨里大学,是IEEE成员。

-

大学有线电视光传输案例-中国纪检监察学院有线电视光传输系统应用浅议2024-01-28 1153

-

光纤推动有线电视发展!2022-12-26 1888

-

解决有线电视基础设施下游发射机挑战2022-12-19 1999

-

应对有线电视基础设施下游发射器的应用挑战2022-08-01 1125

-

如何用淘汰的有线电视放大模块制作CATV无线发射器2021-05-07 2399

-

有线电视常见故障有哪些?怎么解决?2021-04-06 2605

-

美国移动通信市场新挑战,有线电视进军无线领域2018-07-14 2072

-

有线电视濒临死亡!你还在使用有线电视吗?2017-05-12 2014

-

有线电视信号不好2012-09-19 2015

-

有线电视HFC网络技术2011-11-08 1353

-

有线电视解扰器电路原理图2009-08-23 1554

-

有线电视工作原理2009-08-21 12555

-

数字有线电视系统2009-08-01 913

-

有线电视三大技术指标详解2008-10-19 3016

全部0条评论

快来发表一下你的评论吧 !