关键嵌入式系统设计的演变过程

电子说

描述

从低功耗实时监视到具有用于人机界面 (HMI) 的多屏图形显示的高级多媒体应用,汽车、工业、机器人、楼宇控制和其他关键嵌入式系统应用预期需要承担更加多样化的工作负载。在满足这些广泛的功能要求的同时,它们还必须能够支持严格的安全标准,降低成本,减少占用空间以及优化功耗/性能平衡。

迄今为止,为满足这些有时往往相互冲突的要求,开发人员不得不牺牲功能,或增加必要的设备来支持特定的图形、安全性和安全等要求,导致设计和制造的复杂性增加。开发人员真正需要的是一种单一的解决方案,能够跨众多关键的嵌入式系统应用支持各式各样满足上述要求的产品。

本文将简单介绍关键嵌入式系统设计的演变过程。然后展示如何使用 NXP Semiconductors 专门设计的多核应用处理器来应对开发人员面临的挑战,这些处理器可以支持快速扩展的需求列表,包括众多功能性和安全认证能力。

嵌入式系统设计的演变过程注意事项

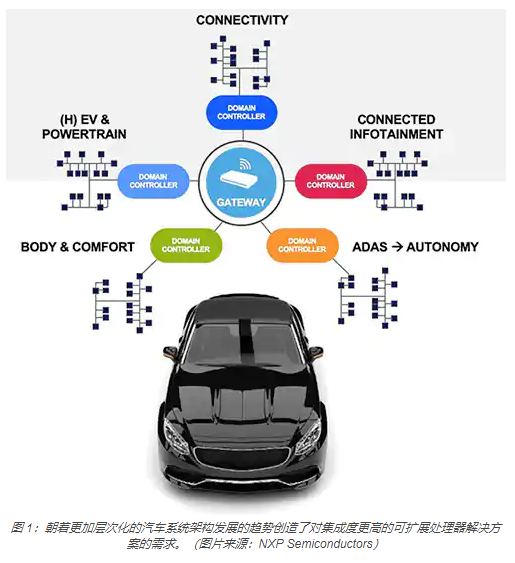

嵌入式设备在支持一组有限的系统功能方面的传统角色,在很大程度上已经被可提供广泛功能的设备的需求所取代。例如,在工业应用中,智能工具和设备对于增强型 HMI 功能的需求要求处理器能够在满足更多传统工业实时要求的同时,提供优化的图形。同样,汽车应用向包含功能域集群和网关的分层架构发展的趋势,推动了能够完全满足这些要求的处理器的需求(图 1)。

在每个功能域中,对于更复杂功能的需求不断提升性能和集成功能的门槛。例如,平视显示器的出现需要能够确保向驾驶员持续提供关键图形信息的解决方案。除了这些新一代的显示器之外,增强驾驶员感知能力的需求与日俱增,也对摄像头接口以及高性能地执行能够提供睡意检测功能的高级识别软件提出了更多的要求。

随着应用的持续发展,为满足日益多样化的要求,同时最大限度减少设计的占用空间并降低成本和复杂性,对于高度集成的可扩展解决方案的需求也变得更加迫切。利用 NXP 的 i.MX 8 系列应用处理器,开发人员可以将兼容的处理器平台与一系列必要的功能和性能相结合,来支持各种各样的应用需求。在 NXP 的 i.MX 8 家族中,i.MX 8X 系列满足了中端汽车和工业应用所需的安全认证处理器的新兴需求。

多核架构管理多样化的工作负载

开发人员在实现用于汽车和工业应用的设备时所面临的一大难题是过宽的需求广度。在开发人员预期处理实时或高级应用处理工作负载的情况下,对智能子系统的需求却将这些截然不同的计算类型合并到一起。开发人员越来越需要能够在支持功能安全要求的同时提供可靠的实时响应和高性能应用执行的解决方案。

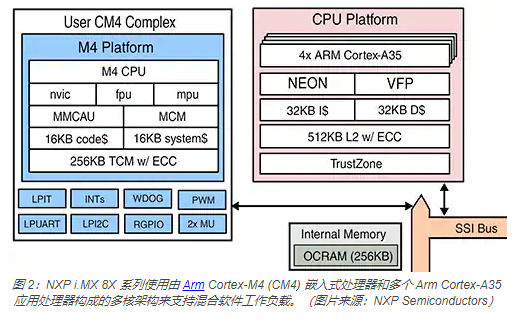

NXP i.MX 8X 系列处理器可提供实时功能、高性能处理,而且功耗很低,可充分利用复杂的多核中央处理器 (CPU) 架构来管理多样化的计算工作负载(图 2)。

对于通用型实时处理任务,i.MX 8X 器件包括一个带浮点单元 (FPU)、内存保护单元 (MPU)、内存映射加密加速单元 (MMCAU) 和混合控制模块 (MCM) 的 Arm Cortex-M4 (CM4) 处理器。为了支持传感器和致动器等外部外设,此用户 CM4 复合体将嵌套向量中断控制器 (NVIC) 与一套全面的接口和模块相结合,包括低功耗周期性中断定时器 (LPIT)、脉冲宽度调制 (PWM) 以及在汽车和工业应用中通常需要的其他功能。一对高速缓存存储器和具有纠错码 (ECC) 功能的紧耦合存储器 (TCM),有助于最大限度减少对外部存储器的访问,加快执行速度和处理存储器错误。

为了快速执行应用工作负载,该 CPU 平台由多个高能效的 Arm Cortex-A35 应用处理器 (AP) 构成,其中两个 AP 在 8DualXPlus 处理器(例如 MIMX8UX6AVLFZAC)中,四个 AP 在 8QuadXPlus 处理器(例如 MIMX8QX6AVLFZAC)中。除了专用指令 (I$) 和数据 (D$) 高速缓存外,该 CPU 平台还包括带有 ECC 的 512 KB 2 级 (L2) 共享高速缓存。

该架构的 Arm Cortex-A35 内核可提供软件兼容性和性能可扩展性,从而支持 32 位向后兼容性和 64 位性能。为了进一步加快计算密集型算法(如信号处理和机器学习)的执行速度,Arm Cortex-A35 处理器提供了矢量浮点 (VFP) 处理和 Arm 的 Neon 单指令多数据 (SIMD) 架构扩展。为了加快用于图像处理、计算机视觉和机器学习的软件的执行速度,Arm 计算库提供了经优化适用于 Arm 处理器和图形处理单元 (GPU) 架构的函数,而开源代码 Ne10 C 库则提供了经 Arm 优化适用于计算密集型操作的函数。

专用引擎分担主 CPU 的负荷

除了用户 CM4 复合体和 Arm Cortex-A35 多核 CPU 平台之外,该架构还提供了专门用于多媒体应用的额外引擎。除了用于音频和语音编解码器处理的数字信号处理器 (DSP) 之外,该架构还集成了 GPU 和视频处理单元 (VPU)。该器件的 GPU 支持标准图形库,使用具有 16 个执行单元的四个独立的四分量浮点矢量 (VPU) 和高性能二维位传输引擎来加速操作。VPU 用于处理常见的视频格式,加速解码高达 4Kp30(逐行、30 Hz)的视频和编码高达 1080p30 的视频。反过来,该芯片的专用显示控制器模块可以将图形输出驱动至多达三个独立的显示器。

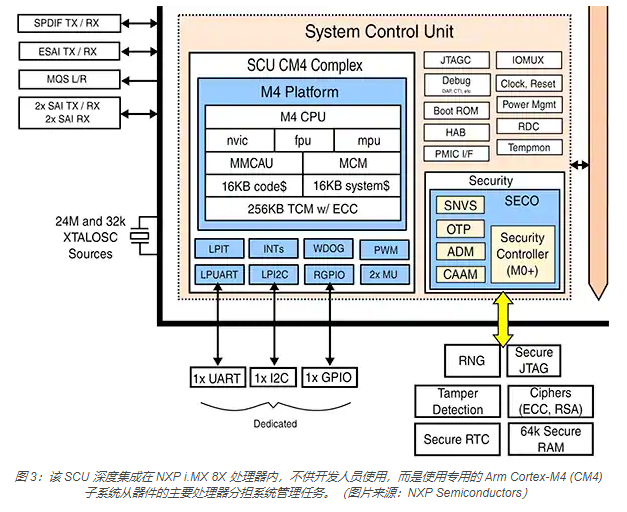

为进一步实现最大化性能,i.MX 8X 架构还集成了更多处理器内核,这些内核旨在将主 CPU 平台从通常在执行系统管理和安全性服务时发生的其他处理负载中解放出来。针对系统管理,该架构的系统控制单元 (SCU) 集成了一个与用户 CM4 复合体匹配的 CM4 复合体,但将其保留完全专用于 SCU 操作,而且不供开发人员使用(图 3)。

除了管理电源、时钟和其他内部功能外,该 SCU 还控制正常操作中的引脚多路复用和输入/输出 (I/O) 通道驱动强度。实际上,用户 CM4 复合体和 Arm Cortex-A35 AP 都不能直接访问这些不同的底层硬件功能。相反,该 SCU 起到了抽象这些功能的作用,因此在用户 CM4 或 AP 上运行的软件只需调用 SCU 固件应用编程接口 (API) 函数,便可执行诸如关闭不需要的功率域这类功能。例如,如果该功率域正在与另一个处理器共享,则该 SCU 仅确认断电请求,但仍将该域保持通电,直到前述另一个处理器也发出了断电请求。

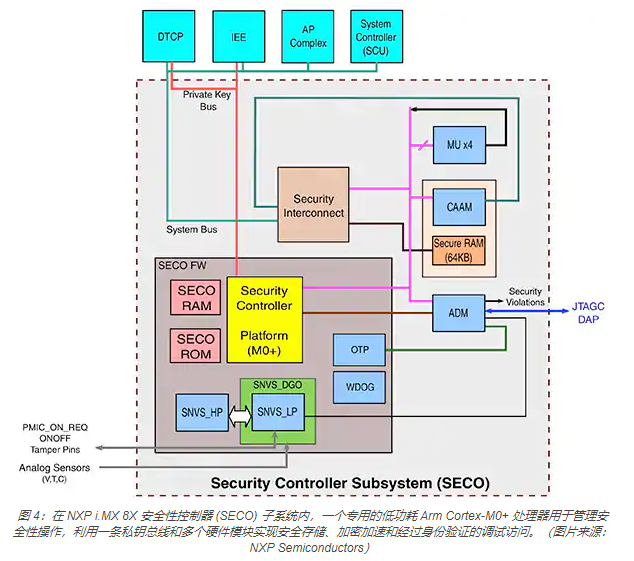

为了管理 i.MX 8X 器件广泛的安全性支持,另一个专用处理器将在器件的安全性控制器 (SECO) 子系统中发挥作用。在 SECO 子系统内,一个集成的低功耗 Arm Cortex-M0+ 处理器用于执行固件,以支持基于硬件的安全性功能,包括用于安全密钥的专用总线访问、用于安全密钥存储的一次性可编程 (OTP) 存储器,以及用于其他私有数据或临时密钥的安全非易失性存储 (SNVS)(图 4)。

除了这些核心安全性机制之外,SECO 子系统还协调安全性操作,实现通过其经过身份验证的调试模块 (ADM) 进行仲裁的篡改检测和安全调试。为保证安全执行,集成的加密加速和保证模块 (CAAM) 硬件安全性模块支持一整套安全性算法,包括对称和非对称密码、哈希函数和一个随机数生成器 (RNG)。

在正常操作中,包括 SCU、AP 和数字传输内容保护 (DTCP) 加速器在内的器件处理单元使用 SECO 安全性互连,通过系统总线访问 CAAM 功能。除了通过 CAAM 直接存储器访问 (DMA) 功能访问外,SECO 的专用 Cortex-M0+ 处理器无法访问系统总线。相反,它使用受保护的内部连接来访问外设、安全随机存取存储器 (RAM) 和只读存储器 (ROM) 及其专用私钥总线。

除了使用 DTCP 加速器外,此私钥总线还在 i.MX 8X 处理器的实时加密和解密支持方面发挥核心作用。在这里,安全性处理器使用其资源提供设备的直插式加密/解密引擎 (IEE) 模块所需的私钥,因为它能安全地从加密存储中读取或写入数据,而无需请求处理器、DMA 控制器或 I/O 设备的参与。

SECO 子系统基于器件的 Cortex-A35 处理器中集成的 Arm TrustZone 技术构建,也可以在安全启动过程中与 SCU 一起使用。在此过程中,SCU 解释启动设置、配置启动源,并将引导映像加载到内部或外部存储器。反过来,SECO 子系统使用其加密功能在已签名的固件映像加载之后、执行之前对其进行身份验证。

保护关键的显示和控制功能

尽管高效且安全地处理多样化工作负载的能力非常重要,但对于诸如汽车和工业领域的任务关键型应用而言,保护关键功能的能力同样至关重要。NXP 的 i.MX 8X 系列将其处理能力与满足这些关键要求所需的安全认证能力相结合。

该处理器系列的安全支持内置于多个层次,始于采用可增强系统可靠性的全耗尽绝缘体上硅片 (FD-SOI) 工艺技术进行制造。由于系统安全依赖于强大的安全性基础,因此启用了 TrustZone 的 AP、SECO 子系统和安全启动功能的组合,可以提供必要的受信任环境,以阻止安全和安全性威胁。

与此同时,利用用户 CM4 复合体独立处理时间关键型任务以及将关键系统任务分担到 SCU 和 SECO 子系统的功能,都有助于确保不论处理负载如何变化,任务关键型应用功能都能保持可用状态。实际上,NXP 通过该公司的 SafeAssure 技术扩展了这一概念,以支持任务关键型显示,该技术在 i.MX 8X 器件中集成了一条支持 B 级汽车安全完整性 (ASIL B) 的硬件显示故障切换路径。利用 SafeAssure,如果器件检测到数据完整性或 GPU 错误,便会自动为用户提供故障切换映像。该故障切换映像在后台运行,可确保即使在主显示器出现故障期间,关键信息仍旧可用。

在基于 i.MX 8X 的系统中,对安全应用的支持扩展到了内存访问。在受其支持的存储器接口中,i.MX 8X 器件为双倍数据速率 3 低压 (DDR3L) 内存提供了 8 位 ECC。除了 L2 高速缓存中的 ECC(请再次参见图 2)之外,此 DDR3L ECC 功能还支持工业安全完整性级别 3 (SIL 3)。i.MX 8X 架构还将 ECC 支持扩展到了外部闪存存储设备。在这里,集成的 Bose、Ray-Chaudhuri、Hocquenghem (BCH) 编码器和解码器模块提供了 62 位 ECC,能够校正从这些存储设备读取的数据块内的 2 到 20 个单比特错误。

启动基于 i.MX 8X 的应用

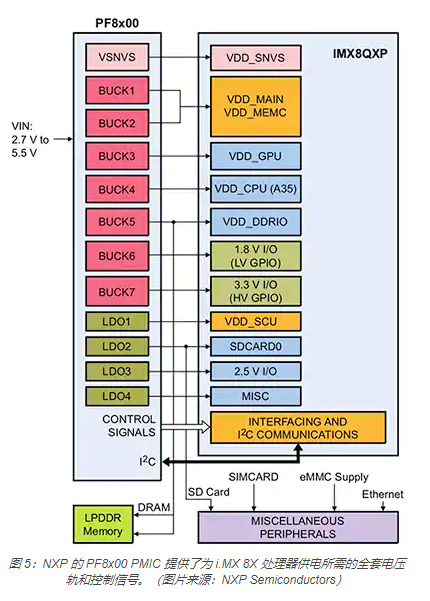

与此类别的任何处理器一样,实现基于 i.MX 8X 的设计需要仔细注意严格的电源要求,包括关键的上电序列。为 i.MX 8X 器件通电时需要依次或同时为四个不同的电源组通电,从 SVNS 子系统开始,再到 SCU、I/O 和存储器接口,最后是器件的其余部分。开发人员只需使用 NXP 的 Pf8x00 电源管理集成电路 (PMIC) 器件便可满足此要求,该器件可提供支持 i.MX 8X 处理器以及外部存储器和典型系统外设所需的整套电压轨和控制信号(图 5)。

在实施他们自己的基于 i.MX 8X 的设计时,开发人员可以使用 NXP MC33PF8100CCES PMIC,该 PMIC 经过预编程,可与 8QuadXPlus 处理器(如 MIMX8QX6AVLFZAC)一起使用。其他 PF8x00变体,如 MC33PF8100A0ES 和 MC33PF8200A0ES,均支持 i.MX 8X 处理器,但未预编程。

对于安全应用,诸如 MC33PF8200A0ES 这类 PF8200 系列器件集成了旨在支持 ASIL B 系统的功能。除了多个内部监视器(包括一个带有专用带隙基准的输出电压监视器),PF8200 PMIC 还包括一个故障安全输出 (FSOB) 引脚,用于在上电期间或发生电源故障事件时使系统保持安全状态。此外,模拟内置自检 (ABIST) 例程将测试所有电压监视器,而自检例程将验证其他器件功能。

尽管 PF8x00 PMIC 可以简化基于 i.MX 8X 的系统的硬件设计,但某些开发人员可能需要立即开始评估 i.MX 8X 器件并快速制作基于 i.MX 8X 的应用原型。NXP 的 MCIMX8QXP-CPU i.MX 8X 多传感器支持套件 (MEK) 提供了一个就绪的开发平台,其结合了 NXP i.MX 8QuadXPlus 处理器、NXP F8100 PMIC、3 GB RAM、32 GB 嵌入式多媒体控制器 (eMMC) 内存和 64 MB 闪存。除了显示器、摄像头和音频接口外,该 MEK 板还包括一组通常用于汽车或工业应用的传感器。为了获得更多的连接、音频和扩展选项,开发人员还可以添加可选的 NXP MCIMX8-8X-BB 基板。

总结

对于汽车、工业、楼宇控制和 HMI 等越来越多的应用而言,处理工作负载已扩展到既包括传统的实时 I/O 处理,也包括新兴的具有多媒体图形的应用级处理。尽管每种工作负载类型都有相应的设计选项,但很少有可用的解决方案能够满足以下日益增长的需求:能够满足汽车和工业应用中的安全认证设计要求的高性能、高能效解决方案。

如上所示,使用 NXP Semiconductors 的多核处理器系列,开发人员可以更有效地实现能够满足上述多样化要求且易于扩展的设计,从而满足新兴的高性能需求。

责任编辑:lq

-

buck电路的演变过程2023-09-25 1474

-

buck电路原理图讲解 buck电路的演变过程2023-08-23 2152

-

了解关键嵌入式系统设计的演变过程如何满足多样化的功能和 安全要求2022-02-15 1873

-

嵌入式系统的开发过程2021-12-22 1266

-

入门物联网,嵌入式是关键2021-07-01 9796

-

【视频分享】降压电路的演变过程2021-06-22 3249

-

定位技术的演变过程2021-03-13 2311

-

嵌入式系统设计的演变过程中如何实现功能和安全要求说明2020-12-29 785

-

嵌入式系统和实时系统开发的关键工艺是什么?2019-08-23 1528

-

嵌入式系统和实时系统开发的关键工艺2019-07-11 1590

-

关于嵌入式系统8大关键特性详解2018-07-05 1345

-

嵌入式系统关键技术分析与开发应用2010-01-19 485

全部0条评论

快来发表一下你的评论吧 !