基于CPLD和电力线载波MODEM芯片实现高压电力线FSK MODEM的设计

可编程逻辑

描述

1 国内电力线载波的应用

在电力系统中,由于电力线载波使用坚固可靠的高压电力线作为信号的传输媒介,可节省大量的通道建设投资,再加上电力线载波信息传输稳定可靠、路由合理、安全保密以及能够同时复用远动信号等特点,使得这种电力系统独有的通信方式在数字微波、一点多址、光纤、特高频等通信方式相继出现的今天仍得到持续的发展。

由于数据信号的信噪比决定传输距离的远近,因此电力线载波通信的关键就是设计出一个功能强大的电力线载波专用MODEM芯片。国外在电力线载波通信技术方面发展较早,多家国外公司陆续推出了自己的电力线载波MODEM芯片,并制定了电力线载波适用频率范围的标准。由于国外电力线载波MODEM芯片是针对本地区电网特性和结构的,且一般是针对家庭内部自动化而设计,因此在国内使用都难尽如人意。

电力线载波MODEM芯片虽然容易使用,但它的中心频率和频偏比较固定,对特殊的应用场合就难以发挥作用。因此有根据特殊应用来开发电力线载波MODEM的必要。以下讨论的就是一个应用于100kV 的高压电力线FSK MODEM的设计。

2 实现电力线载波通信的难点

由于电力线是给用电设备传送电能的,而不是用来传送数据的,所以电力线对数据传输有许多限制,因此电力线通信具有以下特点。

①配电变压器对电力载波信号有阻隔作用,所以电力载波信号只能在一个配电变压器区域范围内传送。

②三相电力线间有很大信号损失(10dB~30dB)。通信距离很近时,不同相间可能会收到信号。一般电力载波信号只能在单相电力线上传输。

③不同信号耦合方式对电力载波信号损失不同,耦合方式有线-地耦合和线-中线耦合。与线-中线耦合方式相比,线-地耦合方式电力载波信号损失十几dB,但线-地耦合方式不是所有地区电力系统都适用。

④电力线存在脉冲干扰。目前国内使用的交流电频率为50Hz,周期为20ms。在每一交流周期中,出现两次峰值。两次峰值会带来两次脉冲干扰,因此电力线上存在固定的100Hz脉冲干扰,干扰时间约2ms。为了保证数据传输的可靠性,必须加以处理。有一种利用波形过零点的短时间内进行数据传输的方法,但由于过零点时间短,实际应用与交流波形同步不好控制,现场通信数据帧又比较长,所以难以应用。

⑤电力线对载波信号造成高削减。当电力线上负荷很重时,线路阻抗可达1Ω以下,造成对载波信号的高削减。实际应用中,当电力线空载时,点对点载波信号可传输到几km。但当电力线上负荷很重时,只能传输几十m。因此,只有通过进一步提高载波信号功率来满足数据传输的要求。提高载波信号功率会增加产品成本和体积。

因此电力线上的高削减、高噪声、高变形,使电力线成为一个不理想的通信媒介;但由于现代通信技术的发展,使电力线载波通信已成为可能。

3 系统组成及工作原理

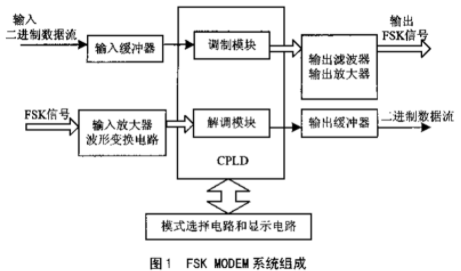

如图1所示,系统主要由两部分组成:调制部分和解调部分。

待解调的二进制数据流通过输入缓冲器后进入调制模块。调制模块输出的FSK方波经过输出滤波器和输出放大器后,变成FSK正弦波耦合到线路上。

待解调的FSK正弦波通过输入放大器,波形变换电路变换成为FSK方波,在输入到解调模块解频之后,经过输出缓冲器就可以得到二进制数据流。

在下面我们将对这两部分作详细进行说明。

3.1 调制部分

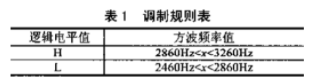

调制方式为FSK,数据为‘1‘时,输出在2860~3260Hz之间正弦波;数据为‘0‘时,输出在2460~2860Hz之间的正弦波。

输入的二进制数据流经过缓冲隔离后,由CPLD采样来判断当前输入电平的高低,并在FSK信号输出端产生相应频率的方波。表1为二进制数据对应的方波频率表。

随着二进制数据的跳变,在FSK信号输出端产生不同频率的方波,从而形成了FSK调制波形(方波)。

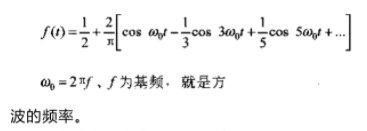

由于方波是由无穷个逐次倍频的正弦波组成的,如下式所示:

所以我们可以在CPLD的FSK信号输出端后,加入一个低通滤波器来滤除方波的高频谐波分量,滤波器输出的则是对应于方波的同频率的正弦信号,经过缓冲放大后即可输出FSK信号。

3.2 解调部分

FSK信号是通过波形变换电路(由比较电路及缓冲放大电路组成)变换成为同频同相的方波。CPLD对方波进行频率识别,并在数据输出端输出解频后的数据流。

3.3 技术指标

载波上限频率—3260Hz。

载波下限频率—2460Hz。

载波中心频率—2860Hz。

波特率—300bps,600bps,1200bps。

调制方式—FSK。数据为‘1‘时,输出在2860~3260Hz之间的正弦波;数据为‘0‘时,输出在2460~2860Hz之间的正弦波。

4 硬件设计

4.1 输入缓冲及输出缓冲

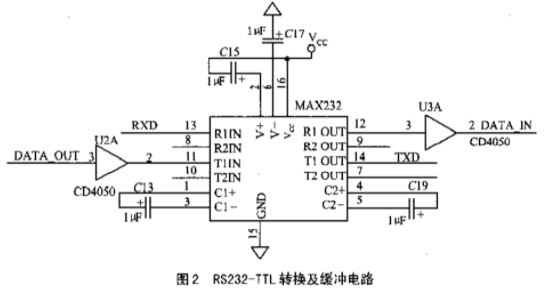

计算机一般是通过串口传输数据,所以要用RS232TTL转换芯片MAX232来进行电平转换,同时通过缓冲器CD4050来隔离并驱动后级,如图2所示。

4.2 输出滤波器,输出放大器

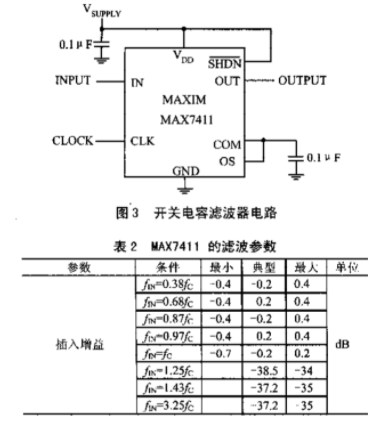

因为需要滤掉载波下限频率的三次倍频7380Hz(2460Hz×3)以上的频率,因此该滤波器的截至频率设计为 4000Hz(》3260Hz)。为了减小体积,这里采用了Maxim公司的开关电容(switched capacitor)滤波器MAX7411。MAX7411是一个五阶低通椭圆开关电容滤波器,具有非常快的下降度且电路十分简洁。图3是由 MAX7411构成的滤波器。

INPUT为输入频率fIN,OUTPUT为输出频率fout‘CLOCK为截至频率fc。该滤波器的效果如表2所列。

由表2可见,在1.25fc处信号衰减达到-38.5dB,已经可以忽略了。

我们的截止频率是4000Hz,即4000=1.25×fC。所以fc=3200Hz。该频率由CPLD产生。

为了能够推动后级设备,必须在滤波器之后加上输出放大器,这里采用FC411。电路为普通的反相放大器电路。

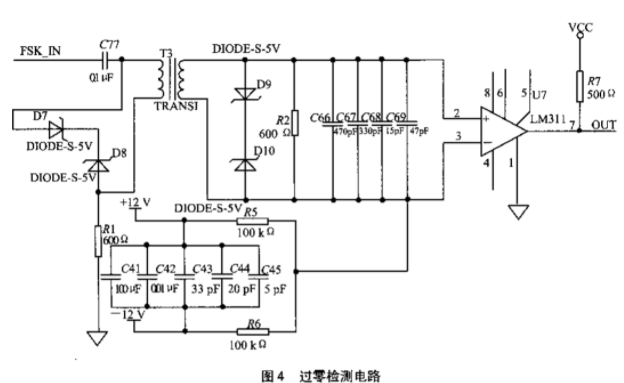

4.3 输入放大器和波形变换电路

如图4所示,输入的FSK和正弦信号经过运放TLE2037放大后,输入比较器LM311进行过零点检测。由于在接地处有较强的噪音,因此必须在电路设计上考虑抗干扰的问题,如采取隔离、浮地等措施。LM311是一款高速比较器,比较速度最在为165ns,它的输出兼容TTL和MOS电路。 LM311通过过零检测,把FSK波形转换成方波输入CPLD,由CPLD进行频率分析,从而实现解频的目的。

5 软件设计

该系统软件最主要的部分就是调制和解调软件的设计,还有一部分是滤波器的时钟产生及工作状态指示与工作模式选择。

此系统可以选择300bps、600bps、1200bps三种波特率,由外部的跳线决定。

工作指示用来指示波特率及系统是否繁忙。如果需要还可以输出同步的时钟信号。

5.1 调制部分

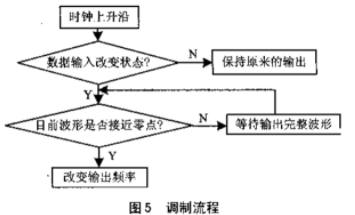

如图5所示,在时钟的上升沿检测数据输入引脚的状态,如果状态变化,则检测当前的波形是否完整(为了保证相位的稳定,要求必须在最靠近波形零点的地址切换频率),如是则切换输出频率。

5.2 解调部分

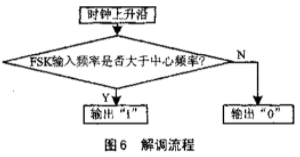

如图6所示,在时钟的上升沿检测FSK信号的频率,并切换输出的数据。

结语

原来采用MCU调制和解调,但是MCU的速度极大的影响了系统性能,尤其是抗干扰能力,使得决定采用高速的比较器和CPLD来进行调制和解调,使得系统的整体性能得到了较大的提高,目前已用于100kV的高压电力线上的控制数据传输。

责任编辑:gt

-

FSK电力线载波通信实验2009-10-11 7197

-

基于电力线载波的注水测调通信系统的研究2010-05-06 3002

-

如何寻找基于OFDM技术采用小波原理的电力线载波芯片2020-06-17 2604

-

LM1893电力线MODEM原理及应用2009-04-22 1428

-

电力线Modem芯片ST75362009-04-24 805

-

FSK Modem MSM7512B 在电力线通信中的应用2009-05-13 844

-

基于CPLD 的高压电力线FSK MODEM 设计2009-05-15 584

-

DSP 用于电力线载波通信研究2010-04-02 591

-

基于OFDM的电力线载波通信的系统设计2010-12-27 1093

-

200M速率电力线Modem设计与实现2008-08-05 1671

-

FSK调制和电力线接口电路2009-02-26 834

-

电力线接入,电力线接入是什么意思2010-04-06 3383

-

根据低压电力线的智能载波模块的设计2010-04-20 1997

-

高压电力线温湿度实时监测系统的设计_吕川2017-01-18 1289

-

基于电力线载波芯片ST7538实现TTU通信模块的设计2020-01-08 9626

全部0条评论

快来发表一下你的评论吧 !