PCIe错误报告的两种机制详解

电子说

描述

1. PCIe错误报告的两种机制

1. Baseline Error Reporting:该机制是PCIe设备必需支持的一种错误报告机制,同时设备会定义最小的错误报告请求。应该是通过配置Device Control和Command寄存器做到通知其他设备产生了错误的一种机制。

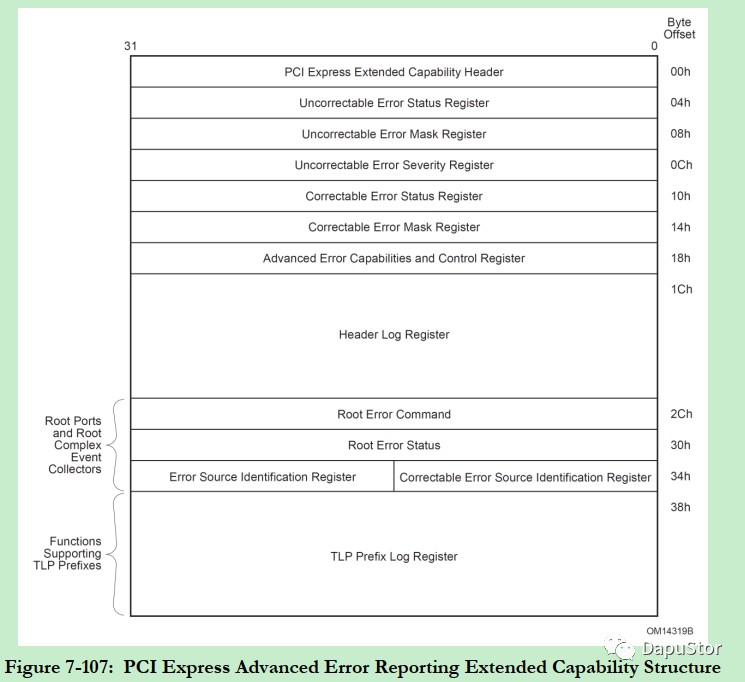

2. Advanced Error Reporting(AER):该机制是PCIe设备用来获取更健壮的错误报告信息的一种特殊机制。该机制的相关寄存器会在PCIe扩展配置空间中上报。

2. PCIe错误的分类

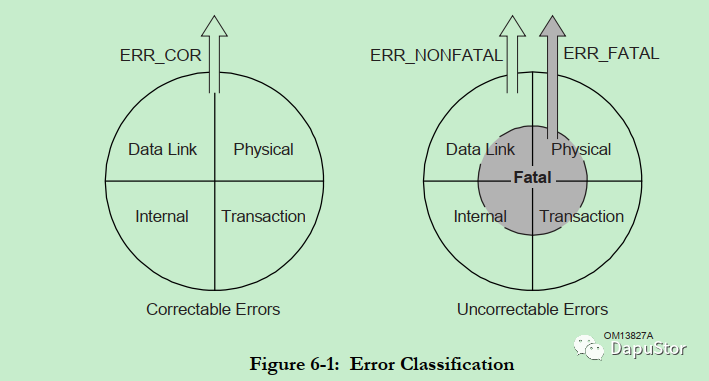

由上图可以看出PCIe将各个层产生的错误大致分为两类:Correctable和Uncorrectable。

其中又将Uncorrectable分为Fatal和Nonfatal两种。通过分类平台可以对Correctable甚至Uncorrectable-Nonfatal的错误分配低优先级的处理,或者检测错误频率等处理;对于Uncorrectable-Fatal的错误可能直接对系统复位处理。

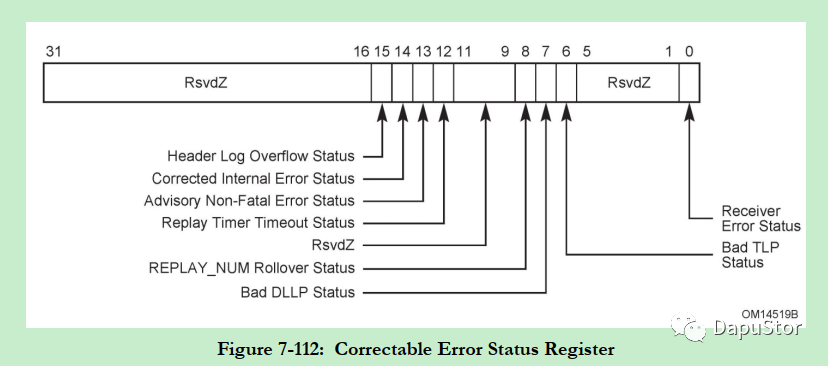

Correctable Errors:是指可纠正的错误,在硬件不经过软件的干预可以通过自身的逻辑纠正的错误。对于一些可纠正的错误如果处理校正的设备不处理的话需要将错误报告成Uncorrectable Errors。

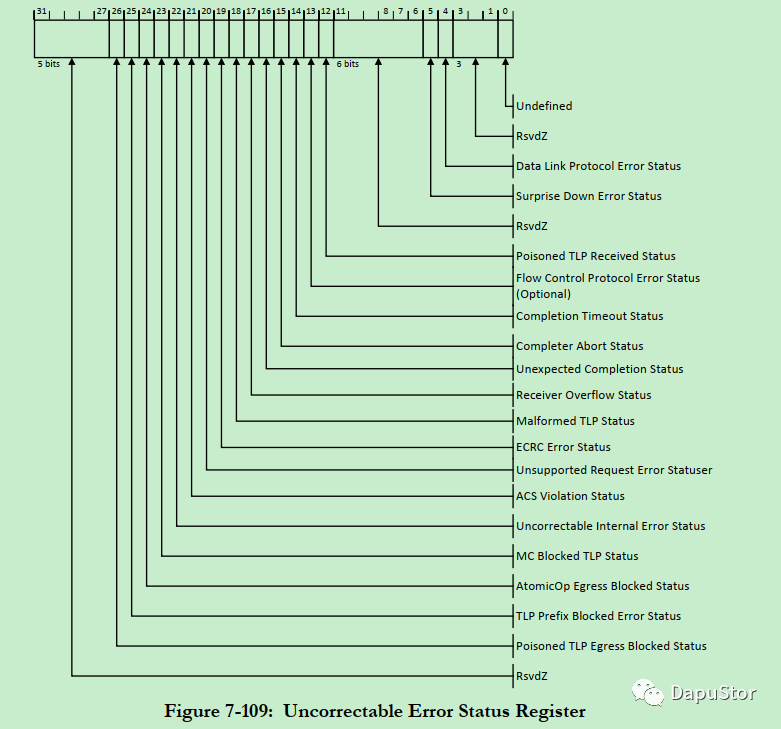

Uncorrectable Errors:不可纠正的错误,这类错误会影响接口的功能,这类错误在协议中没有明确的机制可以纠正。对于PCIe具备更健壮的错误处理机制的设备来说,会进一步区分该错误为:Fatal和Non-Fatal。

Fatal Error:这类错误导致链路和硬件异常只有通过复位操作实现恢复。

Non-Fatal:这类错误可能会导致特定的传输变得不可靠,但是链路和硬件的其他功能不受影响。设备驱动软件提供恢复机制,并不会影响到链路和其他设备的运行。

3. 错误信号转发和通知

PCIe提供了三种方式转发通知错误:

1. 通过回复完成状态Completion Status

2. 通过错误消息 error Messages

3. 通过错误转发机制Error Forwarding

3.1 Completion Status:

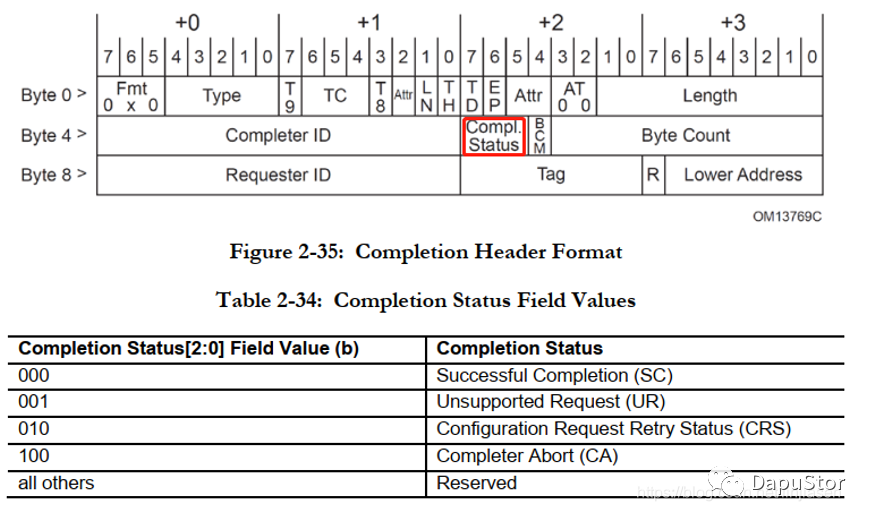

针对Non-Posted请求,一些错误可以通过completion status的方式通知系统或其他设备,这种方式的通知,使上层协议或者软件有机会可以判断状态做相应的补救处理。

3.2 Error Message:

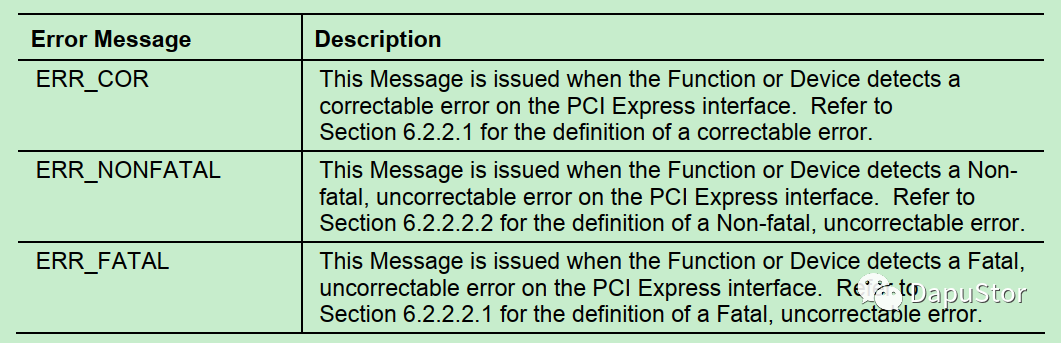

根据错误的严重程度,不同类型的Error Message会被发送给RC。

对于PCIe1.0和1.0a之前的协议一般规定:correctable error发送ERR_COR,non-fatal errors发送ERR_NONFATAL,fatal error发送ERR_FATAL。

随后版本的协议支持Role-Based Error Reporting,可以进一步通过检测设备的身份和AER相关配置将non-fatal error以ERR_NONFATAL或ERR_COR的方式发出去,甚至不发通知。因为在一些平台下发送ERR_NONFATAL可能会阻止其他设备的恢复操作或者决定错误的最终处理,由于不是最合适决定错误最终处理的设备,该设备可以通过配置AER来将错误已ERR_COR的形式通知其他设备,如果是最合适的设备则会以ERR_NONFATAL消息的方式通知其他设备。

对于ERR_NONFATAL,如果软件想避免后续接受设备的错误检测,可以直接配置AER将该错误升级为ERR_FATAL,后续的设备总是会以ERR_FATAL的方式转发下去,无论后续设备是哪种身份。

3.2.1错误消息严重性可编程

对于不同的设备对致命和非致命的界定不同,AER提供了错误消息可编程的机制。AER以协议Error list中判定的消息结果作为默认发送的方式,但是也可通过编程AER的一些寄存器发送更高级的错误消息。

3.2.2错误消息屏蔽

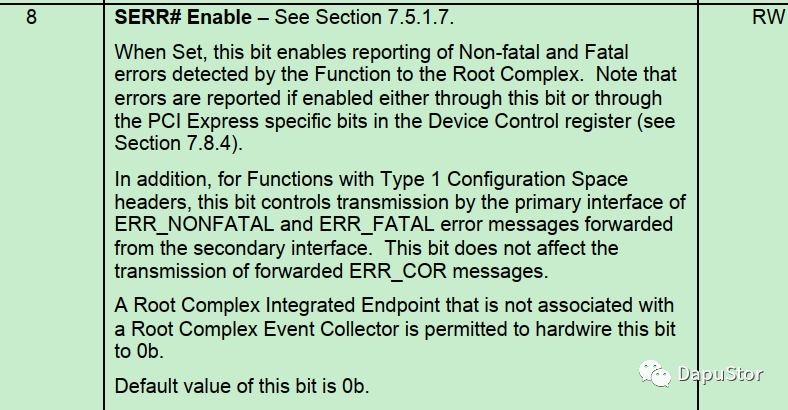

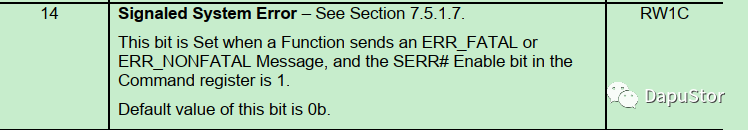

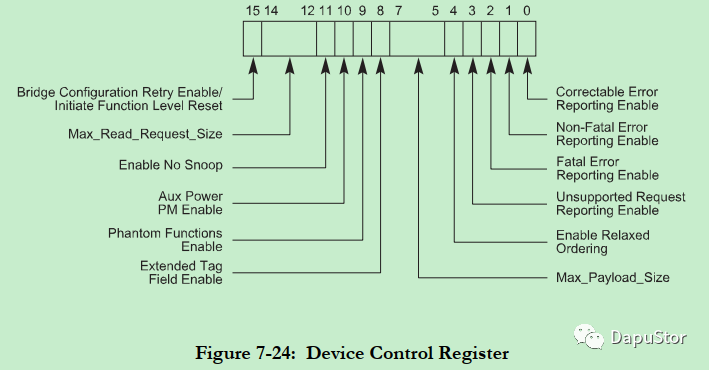

只有当Device Control 寄存器的Reporting Enable fields或PCI Command寄存器的SERR# Enable位置1的情况下设备才能转发消息,此外如果配置了AER的设备可以通过Uncorrectable Error Mask寄存器和Correctable Error Mask寄存器对不同的error进行屏蔽操作。

3.2.3 错误消息污染

如果错误没有得到隔离导致后续的错误覆盖最根本的错误这种情况就是错误污染,比如一个TLP在数据链路层出错的话就不再上传到事务层,而是丢弃这个TLP,上报错误消息。如果产生错误污染就很难定位到根本的错误消息是从哪里产生的。对于产生自同一源的错误协议规定了错误的优先级,越底层的错误其优先级越高。

· 不可更正的内部错误(Uncorrectable Internal Error)

· 接收端Buffer溢出

· 流量控制协议错误

· ECRC校检失败

· 异常的TLP(Malformed TLP)

· AtomicOp Egress Blocked

· TLP包头异常(TLP Prefix Blocked)

· 访问控制服务(Access Control Services,ACS)异常

· MC(Multi-cast) Blocked TLP

· 不支持的请求(Unsupported Request,UR),Completer Abort(CA)或者不对应的返回包(Unexpected Completion)

· 接收到损坏的数据包(Poisoned Packet)

3.2.4 Advisory Non-Fatal Error(警告性的非致命错误)

在一些情况下如果检测到ERR_NONFATAL错误的设备并不是最终决定错误处理的设备,设备如果配有AER则发送ERR_COR提醒软件,若果没有配置AER则不发送消息通知软件。PCIe规定以下几种情况为警告性的非致命错误:

1. Completer Sending a Completion with UR/CA Status

2. Intermediate Receive

3. Ultimate PCIExpress Receiver of a Poisoned TLP

4. Requester with completion timeout

5. Receiver of an unexpected completion

3.3错误转发(Data poisoning)

一旦出现这种情况TLP的EP位被置1,TLP整个路由流程中的接收者都将报告接收到这个poison的TLP,从而能追踪出现问题的位置。

4. 错误日志记录

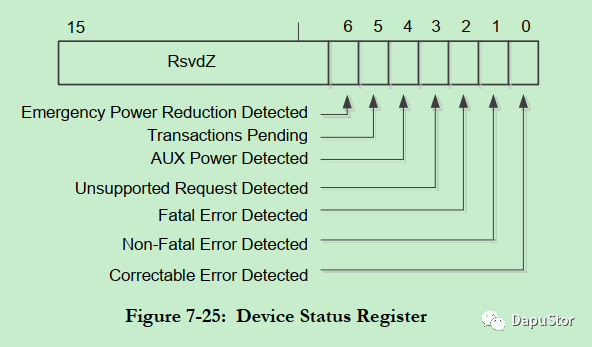

如果设备不支持AER,只有通过查看Device Status寄存器中是否检测到错误,如果支持AER则对应的Uncorrectable Error Status寄存器和Correctable Error Status寄存器会记录相应状态。对于明确的事务层的错误AER的Header Log寄存器会记录第一个uncorrectable error TLP的头。

4.1 错误源溯源

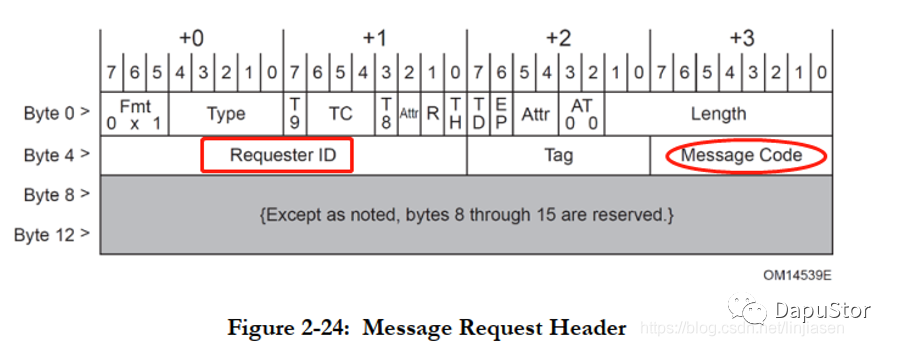

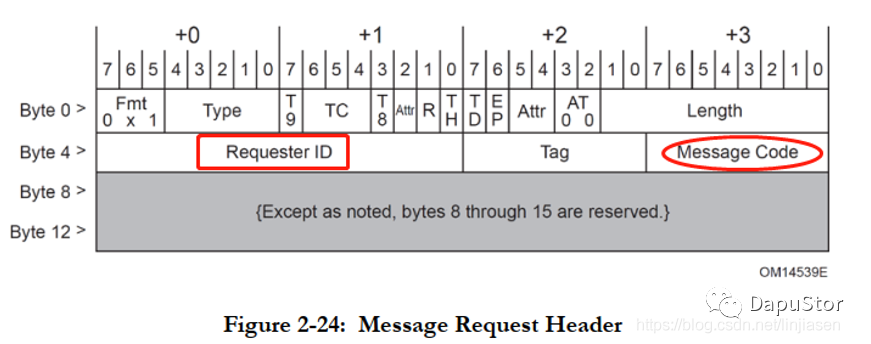

错误消息中包含Requester ID如下图:

系统软件可以根据Root Port或者Root Complex Event Collector 的AER寄存器的内容获取有效的信息

4.2 多条错误的处理(支持AER设备)

对于一个设备如果同时收到多条错误,其AER状态寄存器的位会置上,直到软件清理或者复位清除。即使AER的多个状态位被置起,但是First Error Pointer寄存器和Header Log寄存器中记录的信息还是第一个错误的信息。即使这样还是应该及时的处理First Error Pointer寄存器和Header Log寄存器的信息,防止后续错误增加系统的风险。

5. 流程中涉及到的寄存器介绍

5.1 PCIe标准配置空间的Command Register和Status Register

5.2 PCIE Capabilities寄存器的Device Control和Status寄存器

5.3 AER寄存器介绍

5.3.1 Uncorrectable/correctable Error Status/mask/severity Register

Uncorrectable和correctable的status mask severity寄存器类似,值得注意的是correctable系列的寄存器有个Advisory Non-Fatal Error Status(mask/severity),处理上文中提及的警告性的非致命错误。对于Uncorrectable的错误有Severity寄存器来配置对应错误的严重性,而Correctable的错误并没有对应的Severity寄存器。

Status:当产生相应的错误时,Status寄存器的相应位会被置1;

Mask:当对应错误的mask位置1时,将不再上报错误消息,虽然mask被置1,但是如果有错误产生status相应位仍会置1;

Severity:根据设备的不同要求,可以将uncorrectable error的严重程度配置,1则表示fatal error;

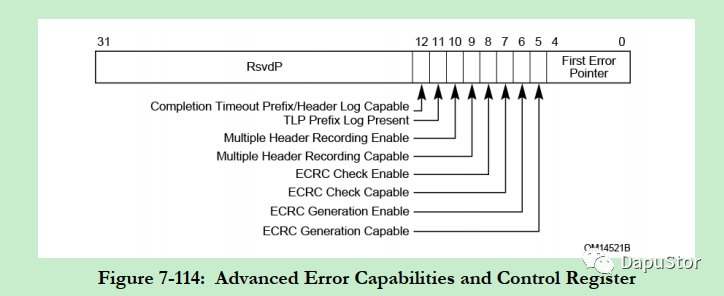

5.3.2 Advanced Error Capabilities and Control Register

First Error Pointer:表示status中报告的第一个错误(对应的status的bit位)

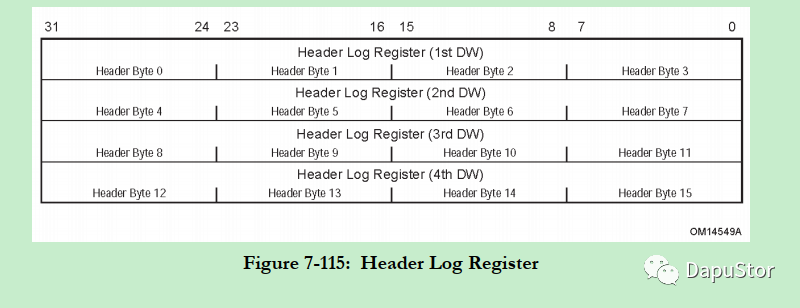

5.3.3 Header Log Register

Header Log Register:记录了第一个错误TLP的Header内容。

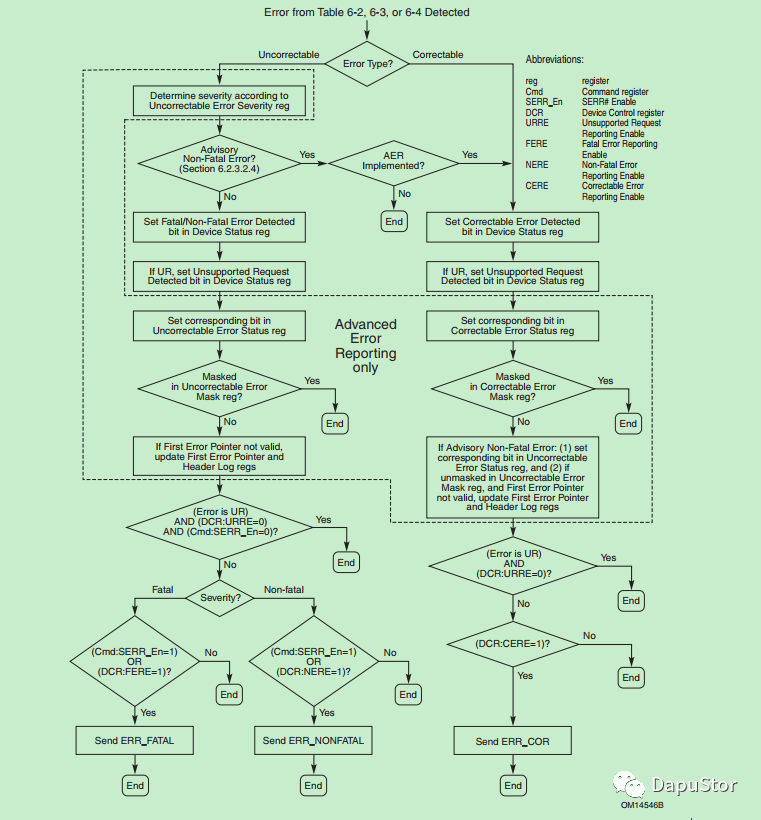

6. 错误消息上报和记录流程

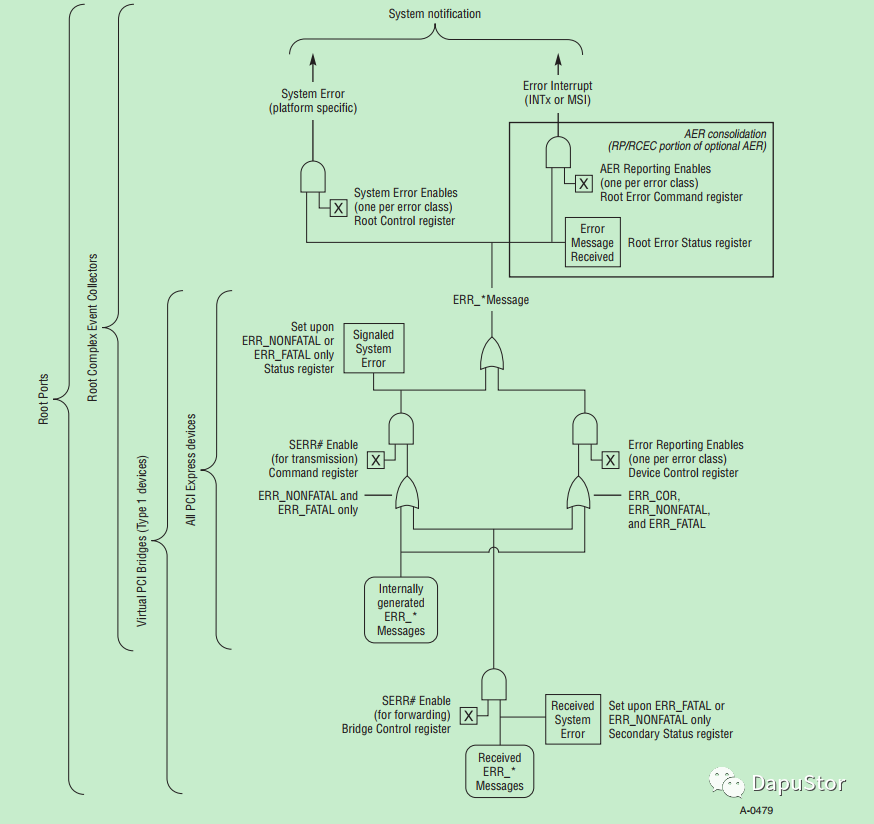

7. Error message路由过程中的寄存器控制流程

8. 总结

Advanced Error Reporting(AER)机制提供了更健壮和丰富的错误消息机制,比传统的PCIe Baseline Error Reporting机制提供了更多的错误处理。AER机制让错误信号更加丰富,让Fw开发人员可以根据不同的场景对错误做出不同的响应。

责任编辑人:CC

- 相关推荐

- 热点推荐

- PCIe

-

PCB设计中如何进行统一批量检测并生成错误报告2018-04-04 11676

-

Win8系统操作不当弹出错误报告2015-06-24 2136

-

仿真停止后怎样关掉错误报告?2016-06-23 2955

-

关于Quartus II 错误报告Error (171173): Node from partition Top cannot preserve previous placement at PIN_P8 and honor the location assigment to PIN_F82016-11-04 11996

-

MPLAB X IDE v3.20编译器使用错误的行号引用报告错误2019-09-16 1055

-

为什么我设计的TMS320VC5402板子在调试软件时总会出现存储器错误报告?2019-09-17 1323

-

当PCIe配置为端点时,如何启用AER(高级错误报告)驱动程序?2023-04-19 770

-

ICC错误集锦、ICCAVR的报错2010-09-09 1129

-

基于软件错误报告数据集成的改进贝叶斯算法2017-12-18 891

-

PCIe总线的错误报告机制中四个比较重要的概念2018-08-17 7896

-

PCIe扫盲—PCIe错误检测机制的详细资料概述2018-08-18 16166

-

PCIe总线的三种错误报告方式2018-08-23 15272

-

PCIe错误报告机制上高级错误报告AER2018-08-27 8716

-

Root如何处理来自其他PCIe设备的错误消息2018-08-28 5429

-

查看服务器连接错误报告的方法说明2022-01-07 1321

全部0条评论

快来发表一下你的评论吧 !