带你深入了解FPGA开发流程

电子说

描述

FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照下图进行,有些步骤可能由于其在当前项目中的条件的宽度的允许,可以免去,比如静态仿真过程,这样来达到项目时间上的优势。但是,大部分的流程步骤还是需要我们循规蹈矩的去做,因为这些步骤的输入是上一个步骤的结果,输出是下一个步骤的输入的关系,这样的步骤就必不可少了。

FPGA开发的具体难度,与软件开发有输入、编译、链接、执行步骤对应的就是设计输入、综合、布局布线、下载烧写,FPGA开发只是为了确保这核心实现主干路每一个环节的成功性加了其他的修饰(约束)和验证而已。下面将以核心主干路为路线,介绍每个环节的物理含义和实现目标。

开发流程

设计输入

1. 设计输入方式

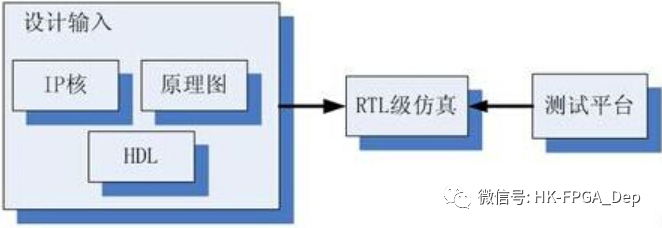

从FPGA开发流程图中的主干线上分离出第一步设计输入横向环节,并做了进一步的细节的处理,如图2,从图上看到,设计输入方式有三种形式,有IP核、原理图、HDL,由此展开设计输入方式的探讨。

①

原理图输入

原始的数字系统电路的设计可能大家还不可能想象,是用笔和纸一个个逻辑门电路甚至晶体管搭建起来的,这样的方式我们称作原理图的输入方式。那个时候,硬件工程师们会围绕的坐在一块,拿着图纸来讨论电路。幸亏那时候的数字电路的还不是很复杂,要是放到今天,稍微大一点的系统,也算得上是浩大工程,稍微有点电路要修改的话,这个时候你要是一个没耐心或是一个急性子的人可能就就会丧失对这个领域的兴趣。话说回来,那个年代出来的老工程师们,电路基础功夫确实很扎实。

事情总是朝着好的方向发展的,后来出现了大型计算机,工程师们开始将最原始的打孔的编程方式运用到数字电路设计当中,来记录我们手工绘画的电路设计,后来存储设备也开始用上了,从卡片过度到了存储文本文件了,那个时候网表文件大致是起于那个时候。

需要注意的问题是原理图和网表文件的关系,原理图是我们最开始方便我们设计的一个输入方式,而网表文件是计算机传递原理图信息给下一道流程或是给仿真平台进行原理图描述仿真用的。设计输入方式不一样,但是对于功能仿真来讲,最终进度到仿真核心的应该是同一个文件,那么这个文件就是网表文件了。

有了计算机的辅助,数字电路设计起来可以说进步了一大截,但是如果依然全部是基于逻辑门晶体管的话,还是比较繁琐。于是后来出现了符号库,库里包含一些常用的具有通行的器件,比如D触发器类的等等,并随着需求的发展,这些符号库不断的在丰富。与在原理图里利用这些符号库构建电路对应的是,由原理图得到的这个网表文件的描述方式也相应的得到扩展,那么这里网表文件里对电路符号的描述就是最开始的原语了。

作为最原始的数字电路ASIC设计输入的方式,并从ASIC设计流程延续到FPGA的设计流程,有着它与生俱来的优点,就是直观性、简洁性,以致目前依然还在使用。但是需要注意的是,这也是相对的,具体讨论见下一小节。

②

HDL输入

HDL全称是硬件描述语言Hardware Description Language,这种输入方式要追溯的话得到20世纪90年代初了。当时的数字电路的规模已足以让按照当时的输入方式进行门级抽象设计顾左顾不了右了,一不小心很容易出错,而且得进行多层次的原理图切割,最为关键的是如何能做到在更抽象的层次上描述数字电路。

于是一些EDA开始提供一种文本形式的,非常严谨,不易出错的HDL输入方式开始提供了。特别是在1980年的时候,美国军方发起来超高速集成电路(Very-High-Speed Integrated Circuit)计划,就是为了在部队中装备中大规模需求的数字电路的设计开发效率,那么这个VHSIC硬件描述语言就是我们现在的VHDL语言,它也是最早成为硬件描述语言的标准的。与之相对的是晚些时间民间发起的Verilog, 后来到1995年的时候,它的第一个版本的IEEE标准才出台,但是沿用至今。

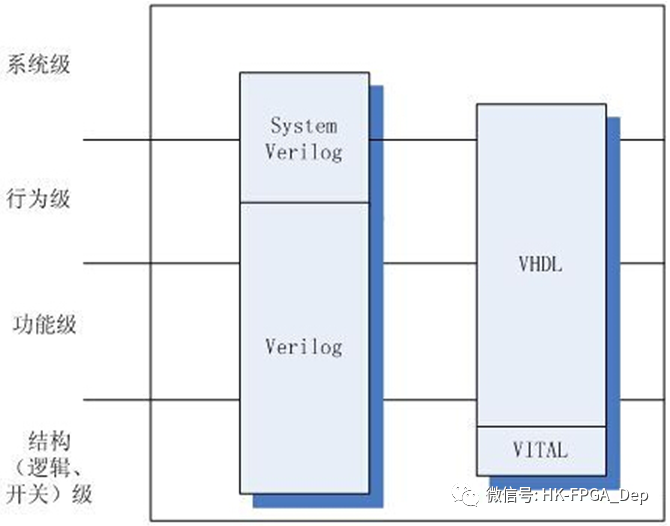

前面提到HDL语言具有不同层次上的抽象,这些抽象层有开关级、逻辑门级、RTL级、行为级和系统级,如图3。其中开关级、逻辑门级又叫结构级,直接反映的是结构上的特性,大量的使用原语调用,很类似最开始原理图转成门级网表。RTL级又可称为功能级。

HDL语言除了前面提到的两种外,历史上也出现了其他的HDL语言,有ABEL、AHDL、硬件C语言(System C语言、Handle-C)、System verilog等。其中ABEL和AHDL算是早期的语言,因为相比前面两种语言来讲,或多或少都有些致命的缺陷而在小范围内使用或者直接淘汰掉了。而因为VHDL和Verilog在仿真方面具有仿真时间长的缺陷,System verilog和硬件C语言产生了,从图3看,System Verilog是在系统级和行为级上为Verilog做补充,同时硬件C语言产生的原因还有就是有种想把软件和硬件设计整合到一个平台下的思想。

③

IP(Intellectual Property)核

什么是IP核?任何实现一定功能的模块叫做IP(Intellectual Property)。这里把IP核作为一种输入方式单独列出来,主要考虑到完全用IP核确实是可以形成一个项目。它的产生可以说是这样的一个逆过程。

在随着数字电路的规模不断扩大的时候,面对一个超级大的工程,工程师们可能是达到一种共识,将这规模巨大而且复杂的设计经常用到的具有一定通用性的功能给独立出来,可以用来其他设计。当下一次设计的时候,发现这些组装好的具有一定功能的模块确实挺好用的,于是越来越多的这种具有一定功能的模块被提取出来,甚至工程师之间用来交换,慢慢大家注意到它的知识产权,于是一种叫做IP知识产权的东西出来了,于是集成电路一个全新领域(IP设计)产生了。

IP按照来源的不同可以分为三类,第一种是来自前一个设计的内部创建模块,第二种是FPGA厂家,第三种就是来自IP厂商;后面两种是我们关注的,这是我们进行零开发时考虑的现有资源问题,先撇开成本问题,IP方式的开发对项目周期非常有益的,这也是在FPGA应用领域章节陈列相关FPGA厂家IP资源的原因。

FPGA厂家和IP厂商可以在FPGA开发的不同时期提供给我们的IP。我们暂且知道他们分别是未加密的RTL级IP、加密的RTL级IP、未经布局布线的网表级IP、布局布线后的网表级IP。他们的含义在后面陆续介绍FPGA的开发步骤的时候,相信大家能够恍然大悟。需要说明的是,越是FPGA靠前端步骤的时候提供的IP,他的二次开发性就越好,但是它的性能可能是个反的过程,同时也越贵,毕竟任何一个提供者也不想将自己的源码程序提供给他者,但是为了不让客户走向其他商家,只能提高价卖了,同时加上一些法律上的协议保护。那么越朝FPGA开发步骤的后端,情况就相反了,越是后端,IP核就会进一步做优化,性能就越好,但是一些客户不要的功能就不好去了。

FPGA厂商提供一般常用的IP核,毕竟为了让大家用他们家的芯片,但是一些特殊需要的IP核还是需要付费的。当然这里需要说明的是FPGA厂商的IP是很少可以交叉用的,这一点很容易想,对厂家来讲不会做这种给竞争者提供服务事情的。IP厂商一般会高价的提供未加密的RTL级源码,有时FPGA厂商为了扩大芯片市场占有率,会购买第三方的IP做进一步的处理后免费提给该FPGA芯片使用者的。

2. 输入方式使用探讨

在上面我们介绍了三种输入方式,有些地方会讲到第四种输入方式,就是门级网表文件输入的形式,我们这里并没有把它归为一种输入方式,原因在于,本身这些门级网表文件的产生还是源于介绍的三种输入方式中的一种或是几种混合的方式。所以这里没有把它归为一类。

好了,在上面三种输入方式介绍的基础上,我们来探讨一下这令人眼花缭乱的输入方式,探讨的目的就是为了让我们更好的使用他们。

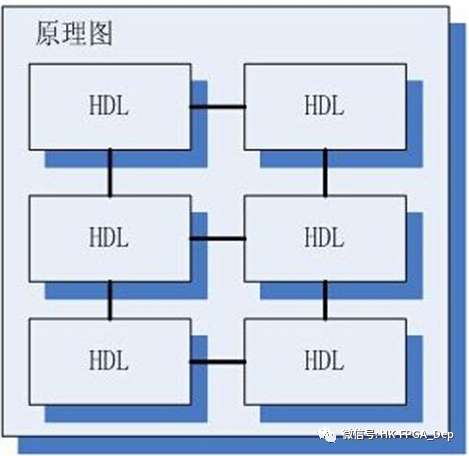

首先,来总结一下三者的优缺点,其实是两种,因为IP核不管是哪个层次,或者在原理图中被以符号的形式被例化,或者在HDL中被模块例化。所以这里集中探讨的是原理图和HDL的优缺点。原理图的优点就是结构直观性,HDL的优点是严密性、支持甚宽的抽象描述层次、易于移植、方便仿真调试等等,缺点就是不具备对方的优点。当时出现HDL的时候,人们确实是想着原理图该退出历史舞台了,但是到现在它还依然存在着。存在即是有道理的,存在就得用它,但是又得使用HDL,于是存在一种混合编程的形式。除了顶层模块用原理图之外,其他的内部子模块全部使用HDL来描述,HDL描述的模块可以通过工具转换成符号,然后在顶层模块中引用这些符号,这就完成混合编程。

在接触的很多FPGA的初学者很容易被原理图的输入方式给迷惑,甚至爱的深沉,加上本身其他输入方式的繁琐的输入的厌恶,更是爱的无法自拔。当开始强制性要求开始时养成多用HDL输入的习惯的时候,有些甚至有着痛心疾首般的痛苦,但是随着学习的深入,做的东西越来越大,尝到HDL输入方式带来的甜头的时候,就会觉得那个苦没有白吃。 我觉得原理图输入方式从现在的一些线索看来,在今后的某一天将会终结。首先是找到了原理图自身带有优势的替代品,那就是主流FPGA集成环境中的综合器和第三方综合器都具有RTL视图生成功能,这个视图完全展示了项目的结构组成,可以上下分层,最大的好处就是可以检查核实写的RTL级代码的综合后电路情况。

还有一条线索是,大家用的仿真软件Modelsim并没有提供原理图输入的支持,是原理图的设计必须在集成环境成转换成RTL级代码或是综合成网表形式来做仿真,也是一件繁琐的事。原理图的离开只是时间问题。 至于目前HDL选择哪一种比较好,这个问题放到开始将HDL基础语法知识的地方进行探讨。这里要说明的是,并不是我们这里讲Verilog使用就否定其他的HDL语言。各种HDL的争端从未停止过,现在还是依然存在四种开发人,第一种是使用Verilog/System Verilog的人,第二种是使用VHDL的人,第三种就是使用System C的人,第四种是混合型的人,到底哪种好,也有也许是时间问题吧,时间证明一切。

综合

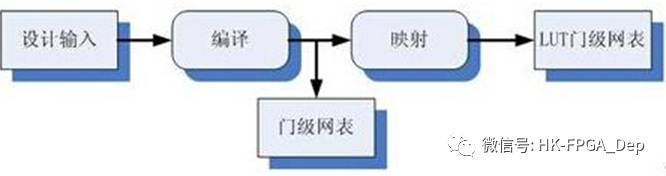

不管是采用单一的输入方式,还是采用的是混合编程(这种在很多跨公司合作项目中会碰见,也许A公司用的是VHDL,B公司用的是Verilog,那这个项目中很大可能采用混合型),我们统称得到设计输入后,都得把设计输入得到一个可以和FPGA硬件资源相匹配的一个描述。假设FPGA是基于LUT结构的,那么我们就得到一个基于LUT结构门级网表。在这个过程中,又可以分为如图两个步骤

需要说明的是在Altera的开发流程中,将编译、映射过程按照我们叙述的合称综合,而在Xilinx开发流程中,由设计输入得到门级网表的过程叫做综合,而映射过程归结到其叫做实现的某一子步骤中。但是整体的流程还是遵循这个顺序的,只是叫法一些外表性的不一样而已。

Synthesis

1. 编译

原理图、HDL、IP核这些都将通过编译后生成门级的网表,这里生成门级网表的过程其实是早期ASIC的步骤,直接生成门电路网表。这个时候的网表文件和具体的器件无关,也就是说,生成的门电路网表也是一种平台移植的媒质。

2. 映射

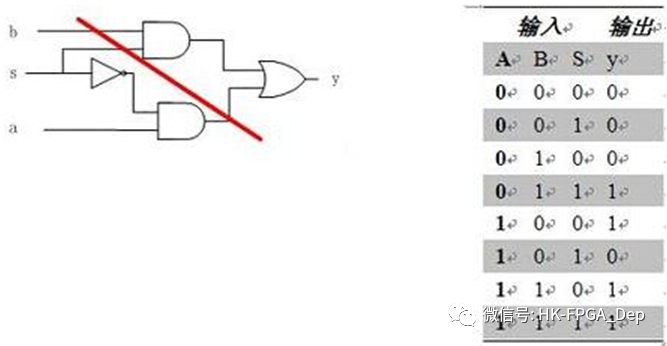

我们通过编译得到一张门级网表之后,与早先ASIC开发流程中在这个门级网表布线后去做掩膜不同,接下来就得考虑如何与我们选择的硬件平台结合起来,毕竟我们使用的硬件平台是由一个一个的LUT(假设这类FPGA)组成的。那么这个结合的过程就是映射过程。 这个过程其实很复杂,首先需要把形成的网表逻辑门给规划成一些小的组合,然后再去映射到LUT中,这个过程中规划按照一定的算法和章程进行。不同的算法和章程就会得到不同的映射,不同的映射就会为后面的过程提供不同的选择,最终生成性能不一样的电路了。 我们把讲基于SRAM技术的FPGA的二选一多路器拿出来举个例子,如下图,可以按照红色线将二选一多路器完全劈成两边,原来的一个表就可以规划到其他两个表或表内容中,因为被劈成的两部分可单独成表,也可以被规划到其他电路形成的表里。

映射的工程比较复杂,运算量也很大,也是为什么FPGA开发过程中,一直存在的一个问题,形成最终的可配置二进制文件的时间非常长,特别是一些大一点的项目,时间消耗比较长的一个点就是映射了,至于具体的映射算法就超出了书的范围了。再强调的是,映射是和器件有关的,即使是同一个系列,不同型号的FPGA内部就够也是有区别的,好比从外观看都是一个单元楼内的单元房,但是每个单元房内装修、家具摆设等都是不一样的。

原文标题:带你深入了解FPGA开发设计之设计输入&综合

文章出处:【微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

拆解FPGA芯片,带你深入了解其原理2024-04-17 878

-

深入了解 GaN 技术2023-12-06 8168

-

深入了解安全光栅2023-06-25 3716

-

干货 | 拆解FPGA芯片,带你深入了解其原理2023-06-02 1568

-

采用抓取波形的方式对SPI进行一下深入了解2022-02-17 1083

-

带你深入了解示波器2022-02-07 1098

-

深入了解主动电扫描阵列(AESA)雷达系统2021-05-24 4001

-

你了解IC内部结构吗本文带你深入了解2019-03-09 13673

-

深入了解单片机汇编重要吗?2015-07-21 3398

-

深入了解LabVIEW FPGA资料分享2015-05-27 5335

-

单片机的深入了解!2014-10-12 3447

-

专家开讲:深入了解电池技术 ──Part 12014-08-18 5009

-

深入了解示波器2013-11-14 6358

-

带你深入了解光耦2012-03-16 1709

全部0条评论

快来发表一下你的评论吧 !