射频PCB的共面波导设计

描述

看看任何受人尊敬的开发板,高频模拟板,雷达板或其他RF系统,您都会看到直接嵌入到PCB布局中的独特波导结构。在用于高频布局和布线的各种RF波导结构中,共面波导设计可能是最常见的。这样做有一些特殊原因,其中许多原因是由于其易于放置在PCB表面层上。

共面波导设计易于在RF PCB布局中进行布线,并且通常用于受控阻抗布线。这对于RF应用非常重要,因为RF应用通常需要将信号路由到放大器,混频器,天线或其他RF组件。在本简要指南中,我编译了在PCB布局中设计受控阻抗时所需的重要共面波导方程。

共面波导设计入门

所有共面波导都有两种类型:标准共面波导和接地共面波导。标准共面波导可以放置在接地平面上方,也可以不接地放置(即,在没有内部接地的PCB的2层顶部)。尽管您都可以创建在内部层中运行的变体,但两者都是为在表面层上布线而设计的。

与标准微带或带状线设计相比,使用共面波导设计具有一些优势:

l 高隔离度。这可能是使用共面波导设计的最常见原因。尽管波导在表面层上布线,但由于周围的接地层,它将具有一定的横向隔离。这与使用倒灌液填充低速走线布线的表面层的原因相同:它提供了额外的EMI屏蔽并终止了走线产生的磁场线。

l 损耗比带状线低。带状线和一些其他波导(例如,集成了衬底的波导)将磁场完全限制在衬底上,因此,波完全看到了有损的PCB衬底。在共面波导中,许多场线穿过电介质上方的区域,因此它们不会遭受那么多的损耗。

l 可调带宽。可以通过调整几何形状来调整结构的带宽。在〜5 GHz处使用的共面波导可能会很大,但是带宽可以限制在单模传播所需的频率范围内。

l 单模传播。带宽是可调的,这意味着我们可以将带宽限制为仅单模(在栅形波导中通常为TE模式)所需的值。

l 与现有的PCB制造工艺兼容。这些结构不需要特殊的制造过程即可生产。当前的制造工艺可用于制造载波频率高达〜100 GHz或更高的共面波导设计。

作为共面波导设计的一部分,需要计算两个主要量:阻抗和有效介电常数(这与微带走线的含义基本相同)。用于这些计算的主要数学工具是第一类椭圆积分,这是由于使用保形映射来导出这些结构中的波阻抗而产生的。让我们更仔细地查看每种类型的结构,以了解如何执行这些计算。

标准共面波导

这里需要涉及椭圆积分的一整套方程。有兴趣的读者应该阅读Brian C. Waddel的《传输线设计手册》,第73-74页,而不是在此处重复列出等式。这一出色的资源为各种射频结构提供了封闭形式的设计方程式,任何射频设计人员均应阅读。

地面共面波导

这种结构是从微带到真正的共面波导的过渡。在大约等于b的基板高度h的极限下,我们现在具有大约微带行为。否则,我们可以以合理的精度使用上述共面波导方程。

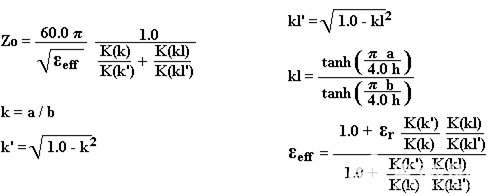

在这里,尽管场线现在可以终止于下层地面,但场线被限制在表层的中心导体和附近的地面之间。有效介电常数大约与波导的几何形状无关,并且大约是空气和基底介电常数的平均值。对于阻抗,我们需要使用如下所示的椭圆积分K(k)。

在此等式中,a是中央走线的宽度,b是接地平面边缘之间的距离。在线上有很多计算器,还有一些开源工具可以为您处理上述计算。

接地共面波导方程

在这里,我们有一个简单的结构,该结构添加了用于模式选择的通孔和更大程度的辐射抑制(即更高的隔离度)。此结构可在PCB上用作微带线的替代品。条带与地面之间的间隙必须小于信号的载波频率,但必须大于基板的厚度,因此,磁场包含在条带与下部接地平面之间。最后,当通孔间隙小于信号载波波长的一半时,可以确保TEM传播。

到目前为止,我还没有看到接地共面波导设计阻抗的闭合形式方程。您会在网上找到的计算器使用的曲线拟合结果仅在特定参数范围内有效。超出此范围,这些曲线拟合近似将失败。使用矩量法的场求解器将为阻抗,传播常数和有效介电常数提供高精度解决方案。

带有波导的更高级的射频设计

还有其他波导几何形状可用于高频路由。由于附近的接地屏蔽,这些波导可以提供TE模式传播并可以提供隔离。这些其他波导布线样式可以在我们博客的另一篇文章中找到。这些其他布线方式也可以采用标准工艺制造,使其易于包含在您的下一个RF PCB中。

就像共面波导设计一样,这些其他布线样式也不提供TEM模式传播。它们还具有高隔离度,可调带宽和单模传播的相同优势。此外,通过选择合适的端接,可以在结构中形成直立模式,这对于耦合到PCB上的天线或其他无源RF组件很有用。如果您可以访问Mathematica之类的程序,则可以高精度计算上面列出的椭圆积分,并确定共面波导设计的电磁性能。更复杂的结构可能需要场求解器才能准确描述设备中的波传播。

当前,最先进的高速和高频路由标准涉及宽带设计,其中在整个信号带宽中都考虑了网络参数和系统中的色散。要了解有关RF设计这一重要领域的更多信息,请看我最近在2020 IEEE EPEPS会议上发表的技术演讲之一。通过查看波导中的波阻抗,可以在整个信号带宽内设计具有所需阻抗的结构。即将到来的高速数字标准(例如USB 4.0)正在采用这种方法进行互连设计,RF设计人员也可以这样做,以消除其波导设计中的信号失真。

-

共面波导传输线特性分析及工程应用2023-01-30 6824

-

怎样去设计分布式电容共面波导结构式移相器?2021-06-08 2454

-

高频PCB设计:影响射频信号性能的因素2021-05-14 7078

-

接地共面波导射频馈线的优化方案解析2021-04-09 8404

-

普通微带线和共面波导结构有哪些优缺点2020-10-10 7834

-

微带线和共面波导的界限是什么?2019-12-18 7885

-

怎么设计微带与共面波导CPWG?2019-08-21 8135

-

一种DC-40GHz带状线到共面波导过渡设计2019-02-04 9577

-

PCB材料对微带线和接地共面波导电路有着怎样的影响2019-01-08 2620

-

由共面波导馈电的单极子双频天线设计与特点介绍2018-12-26 13081

-

干货!抢先看微带与共面波导CPWG设计2018-05-28 46756

-

基于共面波导的NVNA相位参考设计及应用_徐清华2017-01-19 845

-

ADS仿真共面波导问题2013-11-05 9027

-

超导共面波导谐振腔稳频振荡器的实验研究2010-05-14 1033

全部0条评论

快来发表一下你的评论吧 !