输入阻抗和输入电容

电子说

描述

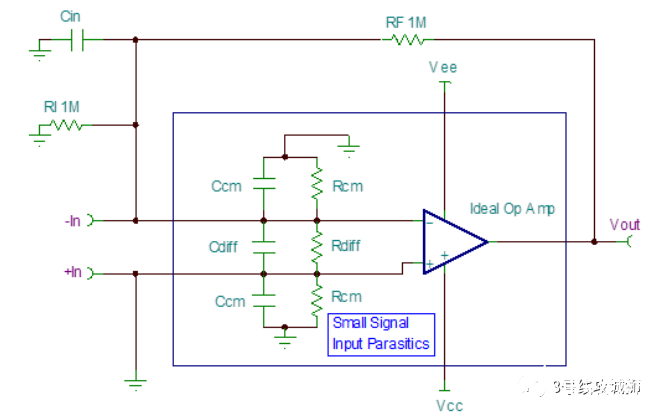

下图 1 形象的说明了运放的输入端阻抗的特性。主要有两个参数,输入阻抗和输入电容。对于电压反馈型运入,输入阻抗主要由输入级的决定,一般BJT输入级的运放。的共模输入阻抗会大于40MΩ。差模输入阻抗大于200GΩ。对于JFET和CMOS输入级的运放,输入阻抗要大的多。这个阻抗通常表现为电阻性。作为常识被我们所熟知。

图 1 运放输入端阻抗特性

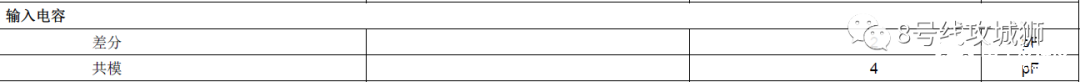

更值得我们多加关注的是运放的输入电容。这个参数通常在datasheet的表格中所列出,但常被忽视。运放的输入电容,通常分为共模输入电容Ccm和差模输入电容Cdiff。如下图 2 是OPA333的datasheet中列出的输入电容。

图 2 OPA333的输入电容

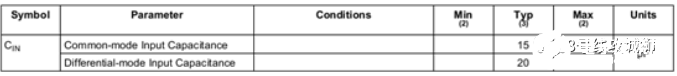

对于有EMI抑制特性的运放,如LMV832,它的输入电容会被设计的正大的些。下图 3 是带EMI抑制功能的LMV832的输入电容值。

图 3

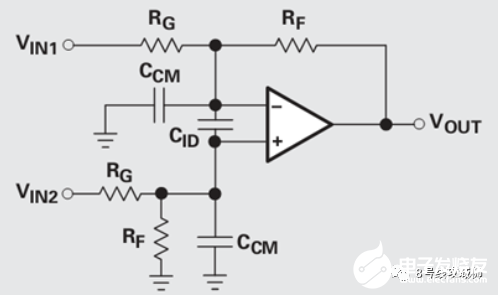

运放的输入共模电容Ccm 和差模电容 Cdiff会形成运放的输入电容 Cin。在许多应用中,运算放大器的输入电容都不会造成问题。但在某些应用中会引起放大电路的不稳定。尤其是反向输入端的电容,是放大电路不稳定的几大罪魁祸首之一。如下图 4 所示是运放在有输入电容的影响下的模型。

图 4 等效模型

这个反向输入端的电容会在运放的环路增益中引入一个极点。正是这个极点的存在,在某些条件下,可能会引起放大电路的不稳定。

运放输入电容引入的极点如下式。即使这个极点0-dB交截越频率之内,而是非常靠近0-dB交越频率,它也有可能引起问题。在这个极点的频率点上,相位会有45度的相位延迟,它很可能减少放大电路的相位裕度。如放大电路的0-dB交截越频率是2MHz。在2MHz处的相位裕度是89°。如果这个极点的频率点也在2MHz处,它将使相位裕度减少45°。而变为φ = 89° – 45° = 44°。44度的相位裕度就显得的不够了。

通常放大电路的输入电容不只由运放的输入电容组成,还包括布线引起的杂散电容和引脚电容。应尽量避免运算放大器反相输入端存在外部杂散电容,尤其是在高速应用中。反相输入周围区域应去除接地层,从而最大程度地减小PC板杂散电容,此外,该引脚的所有连接都应尽量短。

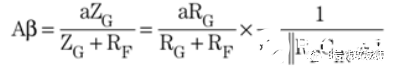

在一些应用,常会加入反馈电容来增加放大电路的稳定,加入反馈电容后的电路的环路增益为,可见反馈补偿电容给环路增益中引入了一个零点。

责任编辑:haq

-

输入阻抗和输出阻抗的工作原理2023-07-25 2590

-

输入阻抗和输出阻抗讲解2023-06-25 20876

-

关于输入阻抗和输出阻抗的理解总结2023-04-17 2932

-

输入阻抗和输出阻抗是什么意思?输入阻抗和输出阻抗的区别是什么?2022-12-27 7463

-

AD9249输入阻抗2021-05-27 887

-

AD9681输入阻抗2021-05-22 874

-

AD9656输入阻抗2021-05-16 896

-

AD9655输入阻抗2021-05-14 868

-

输入阻抗怎么测(输入阻抗测试步骤教程)2017-12-11 78797

-

输入阻抗有什么意义2017-10-26 5090

-

输入阻抗和输出阻抗的基本知识2009-04-22 4948

-

低输入阻抗电路2009-01-18 1142

-

输入阻抗 输出阻抗 阻抗匹配问题2007-12-10 6228

全部0条评论

快来发表一下你的评论吧 !