PCB走线宽度在PCB设计中的重要性

描述

在下一个PCB原型的PCB设计过程中,有几个因素会影响走线的宽度,长度和样式。本文将深入探讨各种需要特定走线布局特征以及如何或何时将它们纳入您的PCB设计的应用。

什么是走线宽度?

让我们从基础开始。迹线宽度到底是什么?为什么指定特定的迹线宽度如此重要?PCB走线的目的是将任何一种电信号(无论是模拟,数字还是电源)从一个结点连接到另一个结点。

结点可以是组件的引脚,较大迹线或平面的分支,也可以是用于探测的空焊盘或测试点。迹线宽度通常以密耳或数千英寸为单位。普通信号的标准走线宽度(无特殊要求)可能在7-12密耳范围内,长达几英寸,但是在定义走线的宽度和长度时,应考虑许多因素。

该应用程序通常会驱动PCB设计中的走线宽度和走线类型,并且在某个时候,通常在PCB制造成本,电路板密度/尺寸和性能方面保持平衡。如果电路板具有特定的设计要求,例如速度优化,噪声或耦合抑制或高电流/电压,则迹线的宽度和类型可能比优化裸PCB的制造成本或整体电路板尺寸更为重要。

PCB制造中与走线相关的规范

通常,以下与走线有关的规格开始增加裸露的PCB制造成本。

由于更严格的PCB公差和制造,检查或测试PCB所需的高端设备,成本变得相当高:

l 迹线宽度小于5密耳(0.005英寸)

l 迹线间距小于5密耳

l 直径小于8密耳的通孔

l 痕迹厚度小于或等于1盎司(等于1.4密耳)

l 差分对和受控长度或走线阻抗

结合了PCB占用空间的高密度设计,例如极细间距的BGA或高信号计数的并行总线,可能需要2.5密耳的走线宽度,以及直径不超过6密耳的特殊类型的通孔,例如激光钻孔的微通孔。相反,某些高功率设计可能需要非常大的走线或平面,从而消耗了整个层,并且浇注的盎司量比标准的要厚。在空间受限的应用中,可能需要非常薄的板,其中包含几层并且有限的铜浇注厚度为半盎司(0.7密耳厚度)。

在另一些情况下,从一个外设到另一个外设进行高速通信的设计可能需要走线具有受控的阻抗以及彼此之间的特定宽度和间距,以最大程度地减少反射和电感耦合。或者设计可能需要一定的长度才能匹配总线中的其他相关信号。高压应用需要某些安全功能,例如最小化两个暴露的差分信号之间的距离,以防止产生电弧。无论特征或特性如何,跟踪定义都很重要,因此让我们探索各种应用程序。

各种走线宽度和厚度

PCB通常包含多种走线宽度,因为它们取决于信号的需求(如图1所示)。所示的较细迹线是针对通用TTL(晶体管-晶体管逻辑)电平信号的,对大电流或噪声保护没有特殊要求。

这些将是电路板上最常见的走线类型。

较粗的走线已针对电流承载能力进行了优化,可用于需要更高功率的外围设备或与电源相关的功能,例如风扇,电动机以及向较低级别组件的常规电源传输。在图的左上部分甚至显示了一个差分信号(USB高速),其定义的特定间距和宽度可满足90Ω的阻抗要求。图2显示了一块稍微密集的电路板,该电路板具有6层,并且需要一个BGA(球栅阵列)组件,需要更细的走线。

PCB走线宽度如何计算?

让我们逐步完成为功率信号计算一定迹线宽度的过程,该功率信号将电流从一个功率组件传递到外围设备。在此示例中,我们将计算用于直流电动机的电源路径的最小走线宽度。功率路径始于保险丝,穿过H桥(用于管理跨DC电机绕组的功率传输的组件),并终止于电机的连接器。直流电动机所需的平均连续最大电流约为2安培。

现在,PCB走线充当电阻器,走线越长和越窄,添加的电阻就越大。如果走线定义不正确,那么大电流可能会损坏走线和/或给电机带来明显的电压降(导致速度降低)。图3中所示的NetC21_2长约0.8英寸,最大需要承载2安培的电流。如果我们假设一些常规情况,例如1盎司铜的浇注量和正常运行期间的室温,则需要计算最小走线宽度和在该宽度下的预期压降。

如何计算PCB走线电阻?

以下是用于迹线面积的方程式:

面积[mils²] =(电流[Amps] /(k *(Temp_Rise [°C])^ b))^(1 / c),其中遵循IPC外部层(或顶部/底部)准则,k = 0.048, b = 0.44,c = 0.725。请注意,我们真正需要插入的唯一变量是current。

在下面的方程式中使用该区域将为我们提供必要的宽度,该宽度告诉我们承载电流而没有任何潜在问题所需的走线宽度:

宽度[mils] =面积[mils ^ 2] /(厚度[oz] * 1.378 [mils / oz]),其中1.378与标准1盎司浇注厚度相关。

通过在上述计算中插入2安培电流,我们得到的走线最小值至少为30密耳。

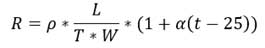

但这并不能告诉我们电压降将是多少。这涉及更多,因为它需要计算走线的电阻,可以按照图4所示的公式进行计算。

在该公式中,ρ=铜的电阻率,α=铜的温度系数,T =迹线厚度,W =迹线宽度,L =迹线长度,t =温度。如果将所有相关值插入30mils宽度的0.8英寸长的走线中,我们发现走线电阻约为0.03?并会降低约26mV的电压,这对于该应用而言还可以。了解什么会影响这些值会很有帮助。

PCB走线间距和长度

对于具有高速通信的数字设计,可能需要特定的间距和调整的长度,以最大程度地减少串扰,耦合和反射。为此,一些常见的应用是基于USB的串行差分信号和基于RAM的并行差分信号。通常,USB 2.0将需要以480Mbit / s(USB高速等级)或更高的速度进行差分对路由。这部分是因为高速USB通常在低得多的电压和差分下工作,从而使总信号电平更接近本底噪声。

有路由高速USB线时要考虑三个重要的事情:线宽,引线间隔和走线长度。

所有这些都很重要,但是三个中最关键的是确保两条走线的长度尽可能匹配。根据一般经验,如果走线的长度彼此之间相差不超过50密耳(对于高速USB),则会显着增加发生反射的风险,这可能会导致通信不良。90欧姆匹配阻抗是差分对布线的通用规范,要实现此目的,应在宽度和间距上优化走线。

图5显示了为高速USB接口布线的差分对的示例,该差分对在15 mil的间隔内包含12 mil宽的走线。

包含并行接口的基于内存的组件的接口(例如DDR3-SDRAM)在走线长度方面将受到更严格的限制。大多数高端PCB设计软件将具有长度调整功能,可优化走线长度,以匹配并行总线中的所有相关信号。图6显示了具有长度调整的走线的DDR3布局的示例。

地面填充的迹线和平面

带有噪声敏感组件的某些应用(例如无线芯片或天线)可能需要一点额外的保护。设计带有嵌入式接地过孔的走线和平面可以极大地帮助最大程度地减少附近走线或平面拾取的耦合以及爬入板边缘的板外信号。

图7显示了一个蓝牙模块的示例,该模块放置在板的边缘附近,其天线(通过丝网印刷“ ANT”标记)在一条厚的走线外部,该走线包含连接到接地层的嵌入式过孔。这有助于将天线与其他板载电路和平面隔离。

这种通过地埋的走线(在这种情况下为多边形平面)的另一种方法可用于保护板电路免受外界的板外无线信号的影响。图8显示了一个噪声敏感的PCB,其沿板的周边具有接地通孔嵌入式平面。

PCB布线的最佳实践

许多因素决定着PCB领域的走线特性,因此在布线下一块PCB时,请务必遵循最佳实践,您会发现PCB晶圆厂成本,电路密度和整体性能之间达到平衡。

如果您正在寻找下一个PCB应用的报价,请与我们的专家团队联系,以帮助您以合适的价格准确获得所需的东西。我们专注于PCB制造和PCB组装,以适应典型的董事会无法制造或组装的复杂设计。

让我们来帮助您将您的设计变为现实。

-

PCB设计中的走线宽度与电流管理2025-12-09 1126

-

揭秘PCB走线宽度计算:原理、方法与实战技巧2025-03-06 1907

-

不可忽视!PCB设计中线宽的“微”妙之处2024-12-25 1291

-

千万不要忽略PCB设计中线宽线距的重要性2024-05-29 2161

-

pcb板走线宽度的设计指南2024-02-23 3122

-

什么是PCB走线宽度?如何计算PCB走线宽度?2023-07-12 14780

-

PCB设计时铜箔厚度,走线宽度和电流的关系.zip2022-12-30 942

-

什么是PCB走线宽度2022-08-22 4141

-

PCB设计的走线宽度与电流有何关系2021-10-14 10187

-

PCB设计时铜箔厚度走线宽度和电流的关系2016-12-16 1241

-

PCB走线宽度标准(军用)2013-09-09 1540

-

PCB走线宽度变化产生的反射2009-11-18 1491

-

PCB设计时铜箔厚度,走线宽度和电流的关系2007-12-12 16028

全部0条评论

快来发表一下你的评论吧 !