BUCK电路原理及PCB布局与布线注意事项

电子说

描述

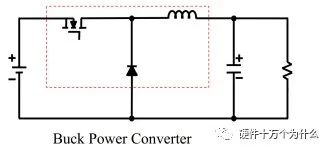

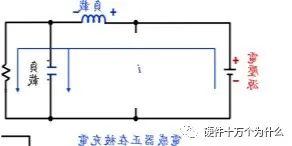

Buck架构:

当开关闭合的时候:

当开关断开的时候:

根据伏秒平衡定理可得:

(Vin-Vout)*DT=Vout(1-D)T===>Vin/Vout=D<1

在实际DCDC应用中:

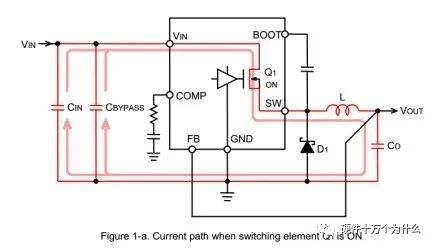

当Q1闭合的时候,在图1-a中,红线示出了当开关元件Q1导通时转换器中的主电流流动。CBYPASS是高频的去耦电容器,CIN是电容器大电容。在开关元件Q1导通的情况下,电流波形的大部分陡峭部分由CBYPASS提供,然后由CIN提供。

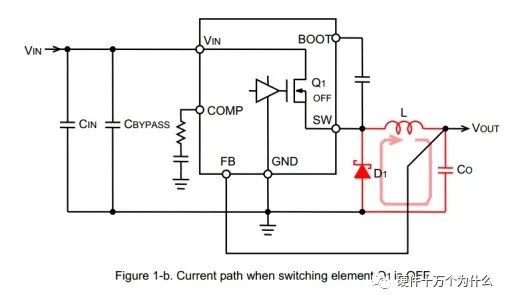

在图1-b中,红线示出了当开关元件Q1断开时的电流流动的状态。续流二极管D1导通,存储在电感器L中的能量释放到输出侧。对于降压转换器拓扑,由于电感插入输出串联输出电容电流平稳。

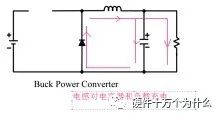

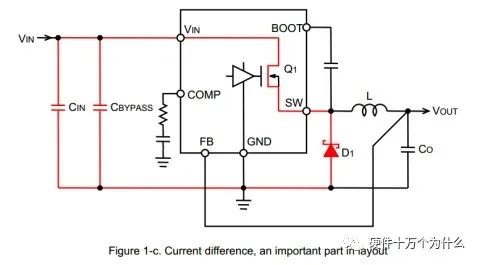

在图1-c中,每当开关元件Q1从OFF变为ON时,该红线中的电流剧烈变化,反之亦然。这些急剧的变化引起几个谐波波形。这种系统差异需要在PCB期间得到最大的注意

PCB布局需要注意一下几点:

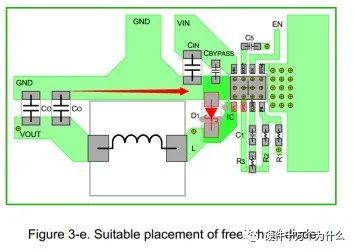

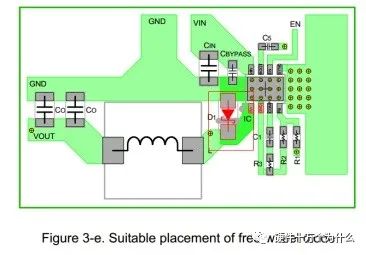

1.将输入电容器和续流二极管置于与IC端子相同的PCB表面层上,并尽可能靠近IC。

2.如果需要,包括热通孔,以改善散热。

3.将电感靠近IC,不需要像输入电容那么近。这是为了最小化来自开关的辐射噪声节点和不扩大铜面积超过需要。

4.将输出电容靠近电感。

5.保持返回路径的布线远离噪声引起的区域,例如电感器和二极管

对于buck电路来说:

首先先讲输入滤波电容及旁路电容:建议采用10UF+0.1uF,当输出负载为Io小于1A的时候,可以选择一个较小的电容放在CIN端,关于Cbypass的布线强烈建议缩短布线甚至1mm,但是即使Cbypass距离IC很近,但是在降压转换的时候也会产生几百MHZ的高频被加载在CIN的地上,因此CIN和CO的接地彼此必须分开至少1cm到2cm。

续流二极管:需采用短而宽的接线方式直接接在IC的GND端子和SW端

输入电容器和续流二极管的放置:

首先,开始放置最重要的部分,如输入电容和续流二极管。单个陶瓷电容器可用作CIN和CBYPASS,用于输入电容器的较小电容值,在小电流电源设计中(IO≤1A)。这是因为频率特性越好,因为陶瓷电容器的电容值变小。但是陶瓷电容器具有不同的频率特性,因此对于使用的实际部件来说是重要的。

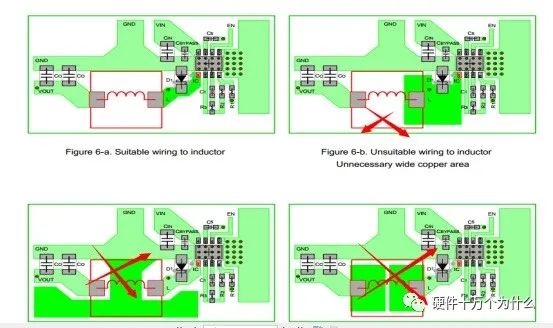

放置电感:

放置电感不需要跟放置输入电容一样距离IC那么近,以最小化开关节点的辐射噪声。增加铜面积最有可能被认为是改善电线电阻和冷却装置,但是扩大的区域可以用作天线并且可以导致EMI的增加。

一般不建议电感下面铺铜,接地层出现的涡流会导致电感的感量变小,

输出滤波电容:尽可能的靠近电感

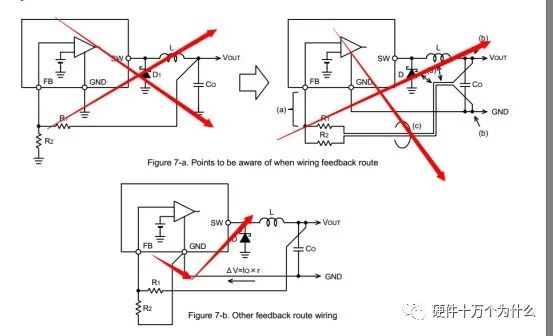

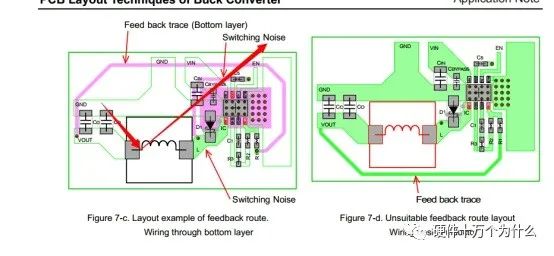

回授控制端:

不要进行将输出的分压电阻分来进行采集输出电压:

a) IC的反馈端子输入反馈信号,通常设计为高阻抗。此端子和电阻交叉网络的输出必须用短线连接。

b)。检测输出电压的部分必须在输出电容器之后或在输出电容器的两端连接。

c)。将电阻分压器电路靠近并且并联,使其更好的抗噪声性。

d)。将导线远离电感和二极管的开关节点。不要直接在电感和Q二极管下方接线,也不要与电源线并联。多层板也必须以相同的方式接线。

通过通孔将反馈路径传输到PCB的底层,并将布局远离交换节点。

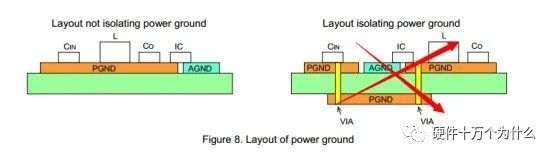

GND 地:

模拟小信号地和电源地必须隔离。铺设电源地,而不从顶层分离是非常理想(图8)。通过通孔连接底层上的隔离电源地导致损耗并加剧由于的噪声通孔的电感和电阻的影响。在PCB内层和底层提供接地层是减少和屏蔽直流损耗,并且更好地散热,但它只是一个补充接地

责任编辑:lq

-

Buck电路中PCB layout布局设计和注意事项2024-08-28 6264

-

高频高密度PCB布局设计注意事项2023-07-19 1537

-

DC-DC芯片PCB布局及注意事项2023-07-04 2699

-

buck电路原理及PCB布局与布线注意事项讲解2022-11-09 2123

-

电源PCB布局、布线、调试要点及注意事项2022-01-06 2509

-

电源PCB布局、布线、调试要点及注意事项相关资料分享2021-12-28 2468

-

电路PCB布局注意事项2021-03-01 4247

-

pcb电源布线注意事项2021-02-25 3604

-

PCB板在手环布局和布线的注意事项2020-10-29 2171

-

PCB电源知多少,开关电源布线注意事项2019-11-21 2808

-

PCB设计高频电路板的布线技巧和注意事项详细概述2018-10-14 7469

-

瞬时电流达到60A的电机供电电路,PCB布局布线设计时注意事项2018-05-07 4515

-

pcb布局的注意事项2012-09-02 4549

-

PCB布线设计,PCB布线注意事项及技巧 DOC下载2009-10-21 14853

全部0条评论

快来发表一下你的评论吧 !