AXI4-Lite总线信号

描述

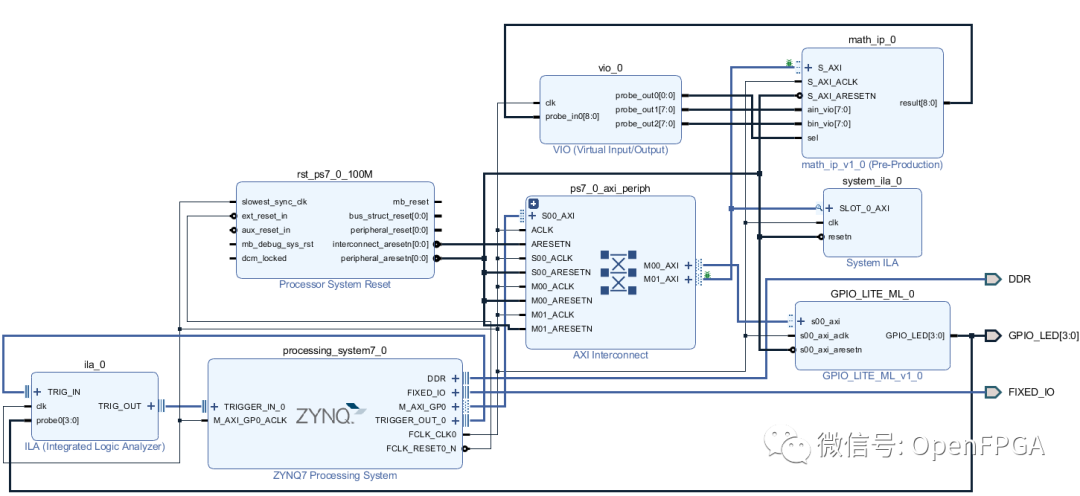

在《AXI-Lite 自定义IP》章节基础上,添加ilavio等调试ip,完成后的BD如下图:

图4‑53 添加测试信号

加载到SDK,并且在Vivado中连接到开发板。

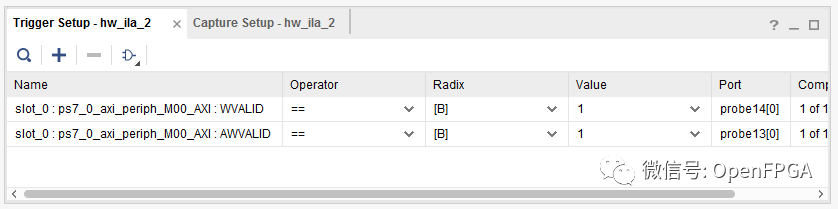

Trigger Setup,点击“+”,选择 AXI_WVALID,双击添加。设置 Radix 为 B,触发条件 Value 为 1。

图4‑54 添加信号

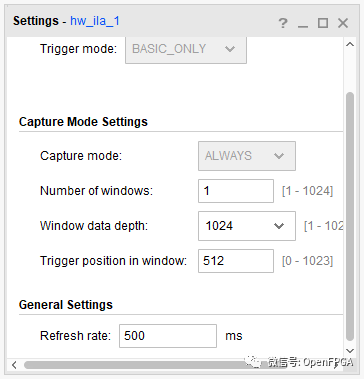

设置触发位置为 512

图4‑55 设置触发位置

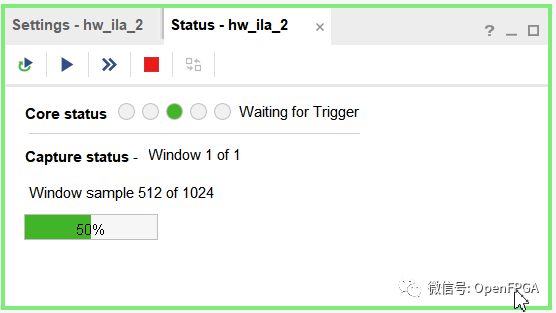

单击运行按钮,启动触发,进入等待触发状态。

图4‑56 等待触发

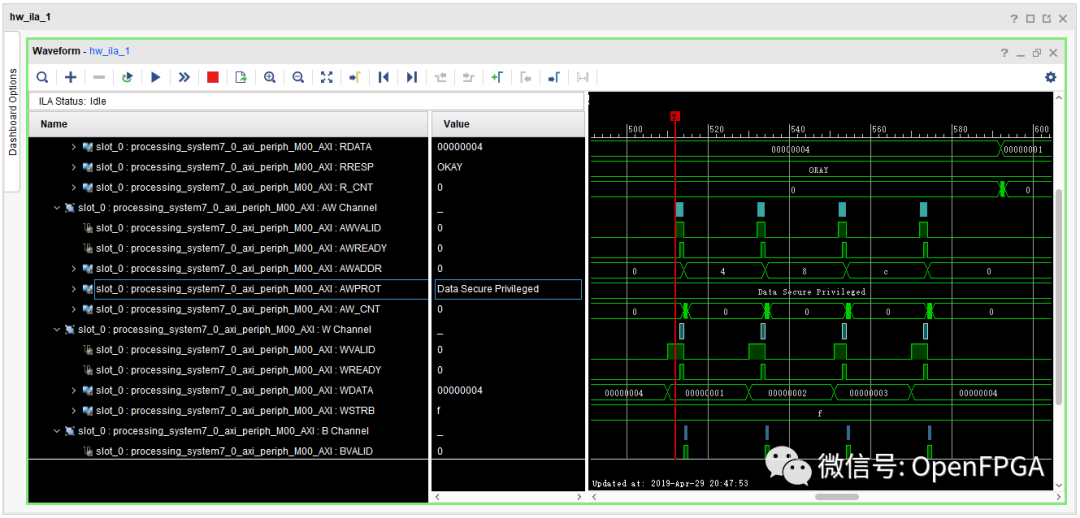

单击 SDK 中的运行按钮后, VIVADO 中 HW_ILA2 窗口采集到波形输出,可以看到 AXI 总线的工作时序。

SDK中 mian.c 程序功能是向 AXI4 总线写入 1~4,再从 AXI4 总线读数据,从上面对未修改直接封装的 IP 分析,可以读出的数据应等于写入的数据。

从波形图可以看出,写入的数据是 1、 2、 3、 4,对应基地址的偏移地址是 0、 4、 8、 12。

图4‑57 仿真结果

责任编辑:xj

原文标题:观察 AXI4-Lite 总线信号

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RDMA简介8之AXI 总线协议分析12025-06-24 1036

-

NVMe IP之AXI4总线分析2025-06-02 6203

-

FPGA通过AXI总线读写DDR3实现方式2024-04-18 2706

-

自定义AXI-Lite接口的IP及源码分析2023-06-25 5189

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3260

-

AXI4-Lite协议简明学习笔记2023-06-19 5972

-

使用AXI4-Lite将Vitis HLS创建的IP连接到PS2022-08-02 1378

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10950

-

AXI接口协议详解2022-04-08 6025

-

Zynq中AXI4-Lite和AXI-Stream功能介绍2020-09-27 10097

-

如何在Vitis HLS中使用C语言代码创建AXI4-Lite接口2020-09-13 7686

-

AXI4-lite端口可以保持未连接状态吗?2020-05-15 1401

-

如何创建基本AXI4-Lite Sniffer IP以对特定地址上正在发生的读写传输事务进行计数2020-04-30 3316

-

将DSP设计融入嵌入式系统的AXI4-Lite接口2018-11-27 3879

全部0条评论

快来发表一下你的评论吧 !