DSP48的演变史

描述

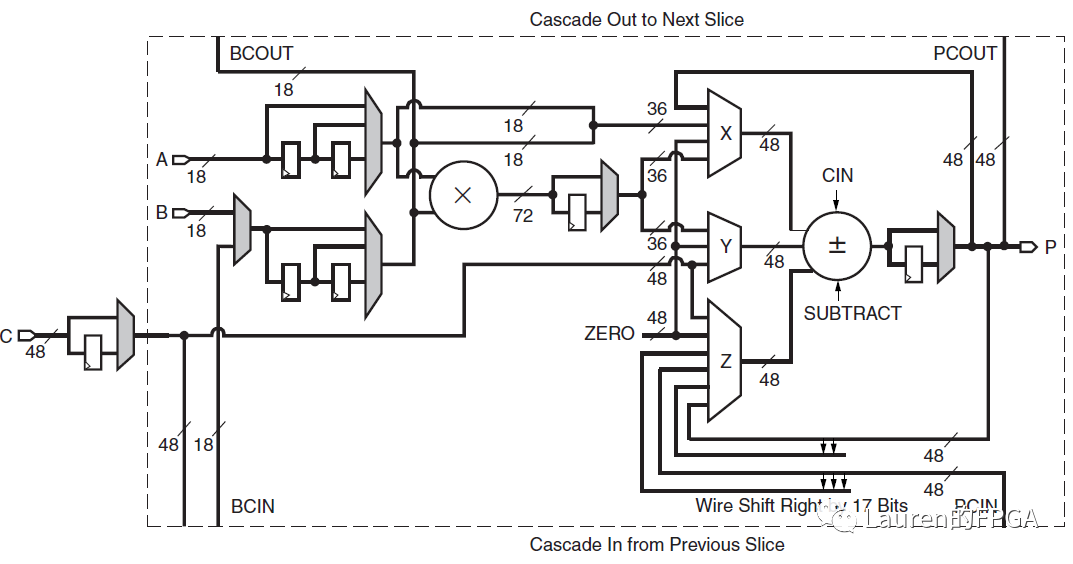

DSP48最早出现在XilinxVirtex-4 FPGA中,但就乘法器而言,Virtex-II和Virtex-II Pro中就已经有了专用的18x18的乘法器,不过DSP48可不只是乘法器,其功能更加多样化。DSP48基本结构如下图所示(图片来源:ug073, Figure 2-1)。DSP48中的核心单元是18x18的乘法器。从图中不难看出,DSP48可实现基本数学函数P=Z±(X+Y+CIN)。这里X、Y和Z是图中3个MUX的输出。根据图中MUX的输入,上述数学函数可以变为P=A*B+C或P=A*B+PCIN,后者需用级联DSP48。因为PCIN和PCOUT是专用走线相连。同时,与Virtex-II不同,Virtex-II中,相邻的DSP48和Block RAM共享互连资源,而在Virtex-4中,DSP48和Block RAM有独立的布线资源。

此外,从资源角度看,Virtex-4SX55包含的DSP48最多,一共8列512个DSP48,在全流水模式下,可运行到的最高频率为500MHz。

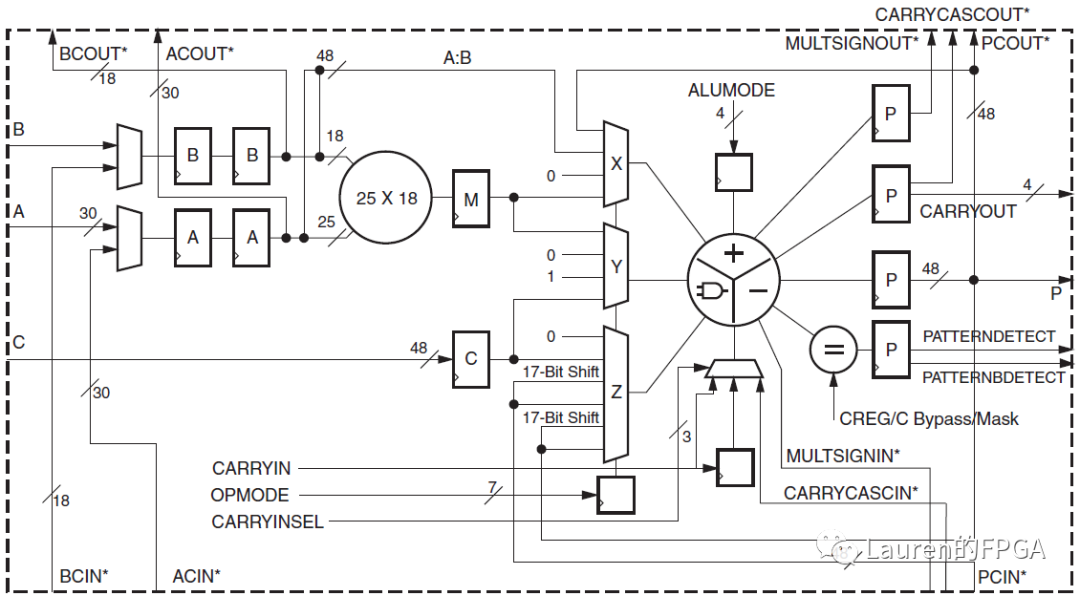

在Virtex-5中,引入了增强型DSP48,称之为DSP48E,其基本结构如下图所示(图片来源ug193, Figure 1-1)。这种增强体现在以下几点:乘法器变为25x18;A端口变为30位,其中低25位可用于乘法器的输入,A和B可拼接为48位,从而可实现{A,B}+C(两个48位数据相加);乘法器之后不再是简单的累加器,而是功能更为多样的ALU(算术逻辑单元),可实现算术运算和逻辑运算。这里特别介绍一下ALU,ALU支持SIMD功能(Single InstructionMultiple Data),使得ALU可配置为2个24位的加法器或者4个12位的加法器。从资源角度看,Virtex-5 SX240T包含的DSP48E最多,共1056个,在全流水模式下,可运行到的最高频率为550MHz。

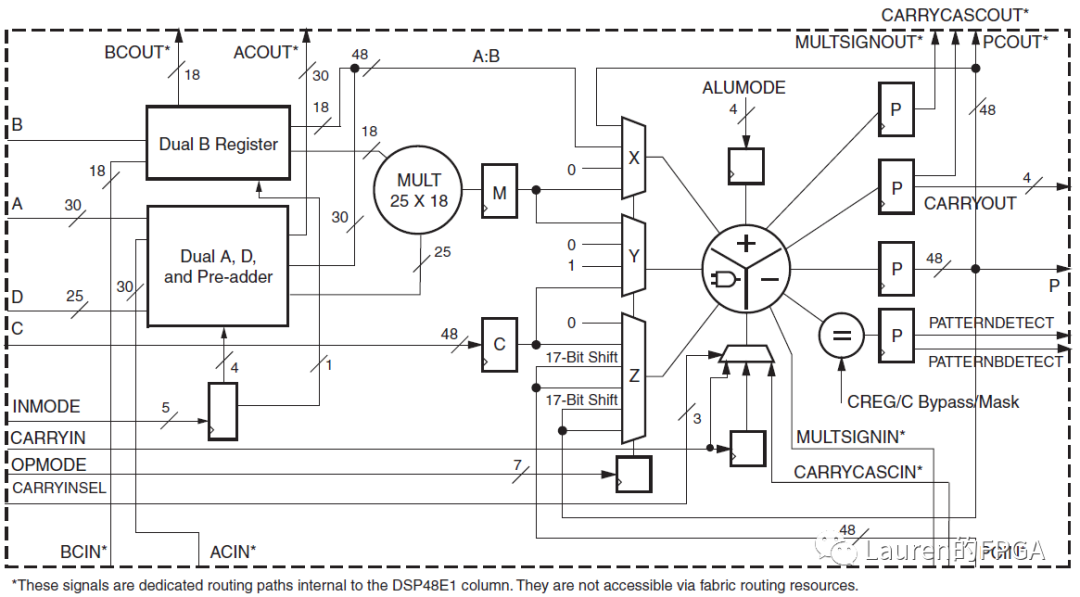

在Virtex-6和7系列FPGA中,DSP48E功能进一步增强,称之为DSP48E1,其基本结构如下图所示(图片来源ug369, Figure 1-1)。最显著的变化是在DSP48E中添加了预加器(可实现25位的加法运算),这对于系数对称的滤波器而言非常有利,可将乘法器资源减半。

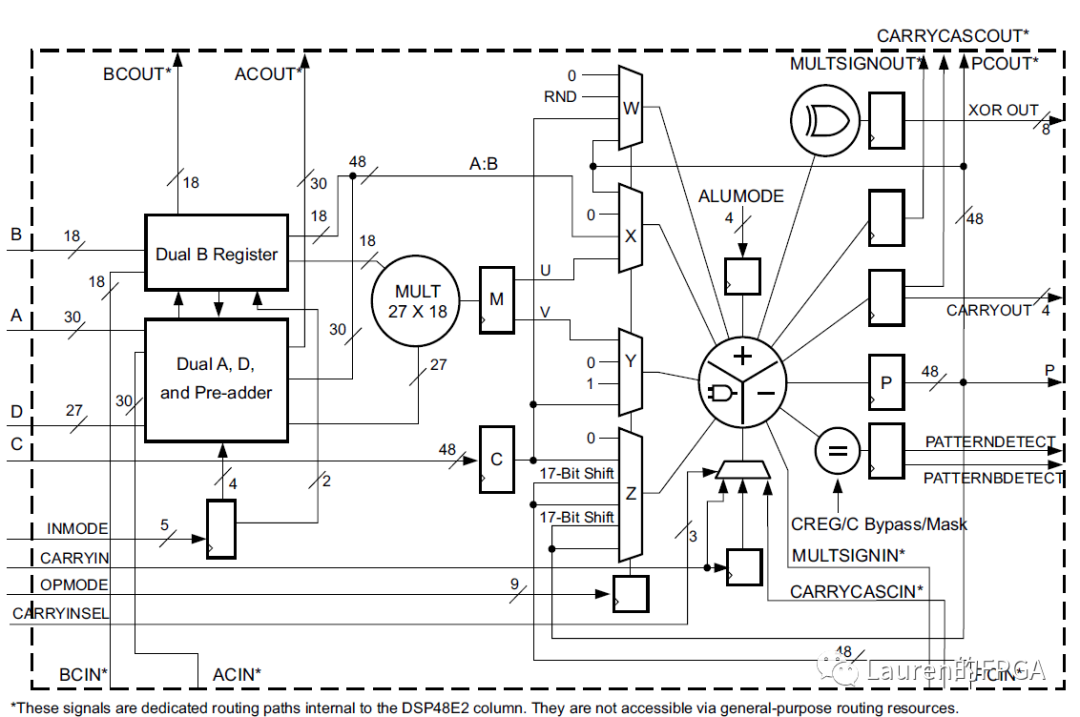

在UltraScale和UltraScale Plus系列FPGA中,引入了DSP48E2,其基本结构如下图所示(图片来源ug579,Figure 2-1)。相比于DSP48E1,其中的乘法器变为27x18,端口D的位宽也由25位变为27位,这样预加器可支持27位的加法运算。预加器的输出可同时送给乘法器的两个输入端口,从而很容易实现平方运算。同时,增加了一个MUX,对应图中的W。ALU可实现Z+W+X+Y。

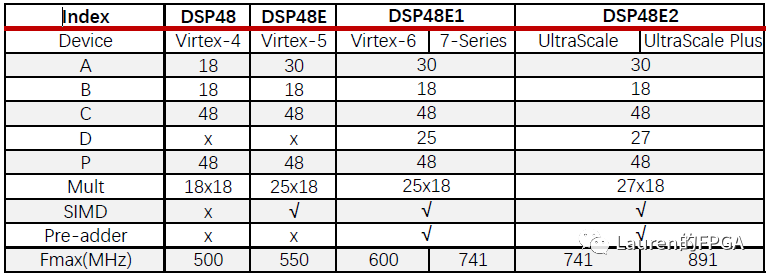

对比DSP48、DSP48E、DSP48E1和DSP48E2,如下表所示。

Tcl之$$a 80%的概率...... AI Engine到底是什么?

ACAP不可不知的几个基本概念

嵌套的for循环,到底对哪个执行pipeline更好

HLS中循环的并行性(2)

HLS中循环的并行性(1)

HLS优化方法DATAFLOW你用了吗

HLS中如何控制流水程度

Vivado HLS学习资料有哪些

如何查看可综合C代码的中间结果

如何在C代码中插入移位寄存器

HLS IP Library? HLS Math Library:csim ?C/RTL co-sim(2) HLS Math Library:csim ?C/RTL co-sim(1) 用Tcl实现Vivado设计全流程(1) 借助Elaborated Design优化RTL代码 (a-b)^2如何高效实现? 如何快速找到组合逻辑生成的时钟 并行加法的高效实现 加法树还是加法链?

两个数相加,三个数相加有什么不同

加法运算很简单? AXI-4 Lite与AXI-4 Memory Mapped有什么区别? 深入理解AXI-4 Memory Mapped 接口协议 AXI是Interface还是Bus? 如何阅读时序报告 时序报告要看哪些指标 如何使set_max_delay不被覆盖 一些小巧的IP IP是用DCP还是XCI? 如果使用第三方综合工具,Xilinx IP… IP生成文件知多少 IP的约束需要处理吗? IP为什么被Locked? copy_ip你用过吗? IP是XCI还是XCIX 如何降低OSERDES/CLK和CLKDIV的Clock Skew 如何获取Device DNA 谈谈设计复用 过约束到底怎么做 时序收敛之Baseline 什么情况下要用OOC综合方式 异步跨时钟域电路该怎么约束 如何复用关键路径的布局布线信息 Vivado学习资料有哪些? 异步跨时钟域电路怎么设计 ECO都有哪些应用 FPGA中的CLOCK REGION和SLR是什么含义 FPGA中的BEL, SITE, TILE是什么含义 约束文件有哪些 如何高效复用Block的位置信息? 如何复用关键寄存器的位置信息 部分可重配置都生成哪些.bit文件 VIO你用对了吗 Device视图下能看到什么 Schematic视图下能看到什么 都是pin,有什么区别 都是net,有什么区别 如何快速查找目标cell 学习笔记:深度学习与INT8 学习笔记:多层感知器 学习笔记:单层感知器的局限性 学习笔记:单层感知器基础知识 学习笔记:神经网络学习算法 学习笔记:神经网络模型 学习笔记:ReLU的各种变形函数 学习笔记:神经元模型(2) 学习笔记:神经元模型(1) 学习笔记:深度学习之“深” 学习笔记:深度学习之“学习” 学习笔记:人工智能、机器学习和深度学习 2019文章汇总

责任编辑:xj

原文标题:DSP48演变史

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

-

DSP48E1详解(3): DSP48E1属性2022-07-25 7103

-

UltraScale DSP48 Slice架构的优势是什么?2021-05-24 3490

-

DSP48E1详解(1):7系列FPGA DSP48E1片的特点2021-01-27 2029

-

苏州站-史迅:ADI的MCU与DSP产品的介绍(2)2019-08-09 3433

-

苏州站-史迅:ADI的MCU与DSP产品的介绍2019-08-08 3372

-

请提供DSP48 slice中的Multipumping示例2019-08-06 1801

-

DSP48A在SPARTAN 3A-DSP上的瞬态2019-05-14 1697

-

DSP48E1作为延迟移位寄存器2019-04-18 2457

-

spartan-6 FPGA DSP48A1芯片的详细资料介绍2019-02-15 5900

-

怎么避免在Synplify中生成DSP48模块2018-10-15 2653

-

如何利用FPGA技术来解决DSP的设计难题?2018-08-18 2306

-

关于fpga的dsp核2017-07-14 2274

-

7 50T FPGA试用笔记(二)/DSP48E12017-02-07 3229

-

飞机机翼的演变史2010-02-24 3124

全部0条评论

快来发表一下你的评论吧 !