关于ARM 处理器的两种主要缓存系统

电子说

描述

为了从 ARM710a 和 StrongARM SA-110 等处理器获得最大性能,必须启用缓存。例如,应用程序可以通过系统上的底层微内核来完成这项工作。但是,如果没有这样的内核,应用程序将不得不自己启用缓存。

ARM 处理器上使用了两种主要的缓存系统。这些都是:

内存管理单元(例如 ARM610、ARM710a、SA-110)

保护单元(例如 ARM940T)

本应用笔记提供了一些示例代码,用于在两种类型的 ARM 处理器上启用缓存,并概述了 ARMulator 的 PageTables 模块。它还讨论了:

@armasm@ 和 @tasm@ 中的重复组装

@armasm@ 和 @tasm@ 条件汇编

@armasm@ 和 @tasm@ 中的宏

带有 C 编译器的内联汇编器

内联函数

内存管理单元 (MMU)

内存管理单元提供完整的虚拟内存系统。有关更完整的说明,请参阅 ARM 体系结构参考手册 (ARM DDI 0100)。简而言之,它使用片外页表向处理器描述:

虚拟到物理地址映射

访问权限

缓存和写缓冲区控制。

支持三种页面大小(1MB、64kB 和 4kB)。(还提供了 16kB 和 1kB 的子页面用于访问控制。)“域”的附加系统用于在多线程环境中提供有效的访问保护。

例如,该系统允许多个具有按需分页和交换的虚拟地址空间。UNIX 操作系统的风格已经移植到使用这种内存管理单元的 ARM 计算机上。

该系统的优点是:

以细粒度完全控制内存

基于域的保护

虚拟到物理地址转换。

主要缺点是它需要内存页表(如果不启用 MMU,则无法启用缓存)。

保护单元 (PU)

保护单元为更嵌入式的环境提供访问和缓存控制。有关更完整的说明,请参阅 ARM940T 数据表 (ARM DDI 0092)。

简而言之,保护单元有一组片上寄存器,其中包含以下描述:

访问权限

最多八个(可编程)内存区域的缓存和写缓冲区控制。

该系统允许在例如嵌入式应用程序中使用基本的内存保护和缓存控制。

该系统的优点是:

访问控制完全在片上(不需要任何片外表)

提供四级访问控制、缓存和写缓冲区控制

对指令和数据缓存的单独控制。

缺点是:

区域数量少

区域大小和对齐的限制。

例子

内存布局

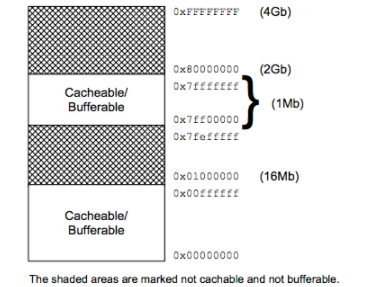

尽管两个系统不同,但都使用协处理器 15 来控制系统。两个系统都有足够的通用功能来区分正在使用的系统。例如,考虑图 1 所示的内存映射。

底部的 16MB 内存被标记为可缓存。这是应用程序代码和堆的基础。

紧邻 2GB 的 1MB 内存也被标记为可缓存,因为这是放置堆栈的地方。

其余内存既不可缓存也不可缓冲。真实系统也可能将该内存标记为“不可访问”(中止生成)。

编辑:hfy

- 相关推荐

- 热点推荐

- ARM处理器

-

ARM920T处理器技术参考手册2023-08-02 1123

-

在FPGA和DSP两种处理器之间实现SRIO协议的方法2023-03-20 4178

-

概述ARM处理器的工作状态和工作模式2020-07-08 2089

-

Arm处理器入侵服务器的两种途径2020-03-01 3405

-

ARM920T高缓存处理器有哪些性能参数和特性?2019-09-26 4102

-

ARM Cortex-A9处理器2018-09-06 12577

-

arm的协处理器有几个?ARM协处理器详解2018-04-24 9826

-

ARM处理器的2种工作状态和7种工作模式及37个寄存器介绍2018-04-23 16159

-

ARM处理器工作模式2017-11-06 2211

-

两种ARM 64位处理器学习平台2016-10-26 6665

-

ARM处理器及ARM处理器工作模式2011-01-27 2851

-

ARM,ARM处理器是什么意思2010-03-26 5683

-

ARM处理器的工作模式2010-03-01 749

-

什么是处理器缓存2010-02-04 1154

全部0条评论

快来发表一下你的评论吧 !