MCU原型设计系统上关于Cortex-M0的使用

电子说

描述

本应用笔记涵盖了 HMALC-AS3 Hpe®_module 与 Gleichmann Electronics Research 的 Hpe®_midiv2 FPGA 开发系统的操作。它描述了 HMALC-AS3 上 CPU FPGA 的内容,包括 CPU 本地的时钟结构和外设。

2. 硬件平台概述

本应用笔记旨在用于装有 ARM Hpe®_module(如图 2 所示)的微控制器原型系统(如图 1 所示)。

微控制器原型系统

ARM Hpe®_module HMALC-AS3

入门

系统预配置了一个安装在客户 FPGA 上的示例设计,如 [3] 中所述。CPU FPGA 预配置了ARM Cortex-M3 处理器,BootMonitor 软件加载到系统闪存中。

关于处理器实现

本应用笔记随附的 FPGA 映像包含 ARM Cortex-M0 r0p0 处理器的实现,以及 2.2 节中描述的外设和总线基础设施。ARM Cortex-M0 处理器实现了 ARMv6-M 架构。

除了实现的调试接口外,两个 FPGA 映像是相同的:

@fpga_processor_cortex-m0_serial_wire_encrypted.pof@:串行线

@fpga_processor_cortex-m0_jtag_encrypted.pof@:JTAG

固定配置

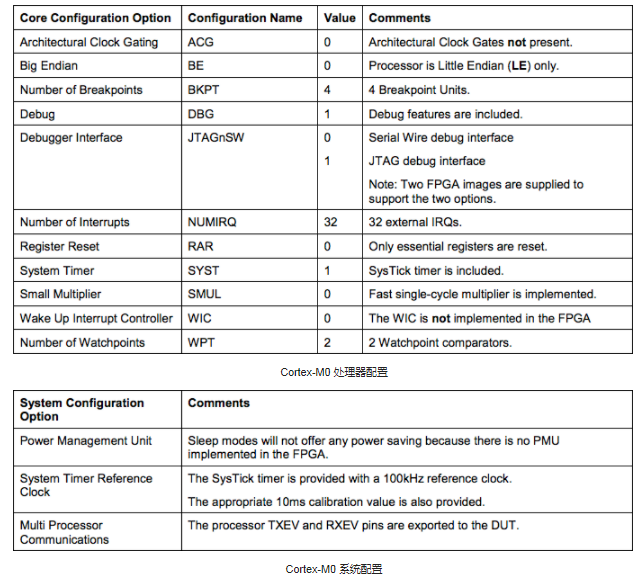

ARM Cortex-M0 r0p0 处理器包括许多配置选项,可在设备综合时设置这些选项。图 3 中的表格列出了为本应用笔记随附的 FPGA 实现选择的选项。图 4 列出了与该 FPGA 映像相关的系统配置选择。

“配置名称”是用于配置处理器的 Verilog 参数名称,供处理器许可证持有者参考。

编辑:hfy

-

怎样去设计基于ARM Cortex-M0核的MCU2021-11-10 1309

-

具有灵活模拟子系统的Cortex-M0 MCU2022-12-08 520

-

ARM Cortex-M0设计启动评估用户指南2023-08-18 662

-

深入浅出Cortex-M0学习资料2010-06-18 1201

-

新唐科技推出基于Cortex-M0内核的32位MCU2010-01-09 1256

-

Cortex-M0的指令集2016-01-13 1132

-

TinyM0配套教程】LPC1100系列Cortex-M0最小系统设计2017-09-29 1153

-

TinyM0配套教程LPC1100系列Cortex-M0最小系统设计2017-10-09 1072

-

cortex-m0加密2017-10-13 1335

-

新塘 Cortex-M0 最小系统2017-10-16 1567

-

基于ARM Cortex-M0核的MCU设计及应用2021-11-05 1232

-

使用megawin Cortex-M0 MCU的BLE(蓝牙低能量)访问2022-07-01 619

-

全球最强性能Cortex-M0 MCU诞生!2022-12-20 2402

-

IDT ARM Cortex-M0 用户指南2023-07-10 633

-

敏矽微电子Cortex-M0学习笔记02——Cortex-M0开发环境的建立及调试2023-09-26 3406

全部0条评论

快来发表一下你的评论吧 !