PIC32MZ器件系列中的 1 级(L1)CPU 缓存实现

描述

本应用笔记的目的是让读者了解PIC32MZ器件系列中的 1 级(L1)CPU 缓存实现,让读者了解缓存系统中可能发生的危险,并描述解决这些问题的方法。对于高级用户,还讨论了 microAptiv™ 内核中管理缓存以获得最佳性能的特殊指令。

本文档不打算全面讨论缓存体系结构或实现,也不涉及缓存管理的每个细节。从未使用过具有 L1 缓存的嵌入式控制器的开发人员,或希望了解 PIC32MZ 器件中 L1 缓存实现的开发人员,应阅读本文档。

CPU 缓存是一个单独的内存块,用于补偿主内存的访问时间。被描述为一级缓存的缓存使用与 CPU 一样快的内存,因此只要 CPU 正在访问缓存,它就永远不必等待指令或数据。2 级和 3 级高速缓存与 1 级高速缓存结合使用,其内存访问时间大于 CPU,但小于主内存。

该PIC32MZ器件系列仅采用1级高速缓存。L1缓存分为两部分,指令缓存和数据缓存。CPU 可以直接访问内存或通过缓存访问内存。高速缓存的使用对于实现PIC32MZ器件系列的最大性能至关重要。与通过系统总线进行访问时的多个时钟周期相比,对高速缓存的内存访问发生在单个时钟周期内。

PIC32MZ 架构

以下部分介绍了PIC32MZ架构的 L1 缓存和其他两个部分,它们对其操作和配置至关重要。

闪存预取模块

Flash Prefetch 模块用于隐藏 Flash 等待状态。它通过使用 128 位数据路径(是 32 位 CPU 总线宽度的四倍)获取程序闪存来实现。它是预测性的,假设下一个需要的数据是下一行地址。只要代码不分支,下一条指令总是可用的。加载新行时,分支会导致停顿。该模块中的寄存器确定闪存等待状态以及预取是应用于指令访问、数据访问、两者还是两者都不进行。

内存映射单元

在所有 PIC32 架构中,CPU 对存储器和外设的访问都是通过虚拟地址空间完成的。虚拟地址空间分为五个段,分别命名为 KSEG0 到 KSEG3 和 KUSEG。物理到虚拟 KSEG0 到 KSEG1 地址的映射是固定的,所有内部存储器都存在于 KSEG0 和 KSEG1 段中。KSEG1 从不缓存,而 KSEG0 是可缓存的段。

PIC32MZ 架构引入了基于转换后备缓冲器(TLB)的存储器映射单元(MMU)。TLB 可以配置为对 KUSEG、KSEG2 和 KSEG3 执行虚拟内存到物理内存的转换。这些段的可缓存性属性是在使用 CPU 协处理器 0 (CP0) EntryLo0 和 EntryLo1 寄存器配置 TLB 时定义的。

L1 指令和数据缓存

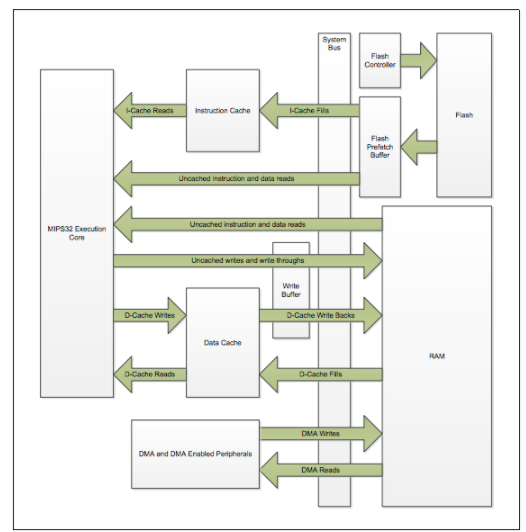

如图 1 所示,CPU 可以直接访问系统 RAM,也可以通过缓存访问。同样,对 Flash 的访问可以直接发生,也可以通过缓存发生。DMA 访问总是直接通过 RAM 进行。除了 CPU 和缓存之间的访问之外,所有访问都涉及系统总线。

在复位时,代码执行从 KSEG1 使用非缓存访问发生。这是必要的,因为缓存在被启动代码初始化之前无法使用。一旦缓存被初始化,代码执行就可以从 KSEG0 开始,它利用缓存来获得最佳性能。

当 CPU 使用缓存进行访问时,系统将检查所需的数据是否已存在于缓存中。如果数据存在于缓存中,则不执行任何操作。这称为缓存命中。如果没有,硬件会使用内存内容填充指令或数据缓存。这称为缓存未命中。缓存未命中会导致性能损失,而缓存命中则不会。

缓存的大小是闪存或 RAM 大小的一小部分。它可以在初始化时以多种方式进行配置以优化性能。MPLAB 开发工具将 PIC32MZ 缓存配置为“四路关联”,因为这将是大多数应用的最佳配置。四路关联配置将缓存分为四个相等的部分,称为路。其中每一个都分布在整个内存地址范围内。每个缓存路被分成缓存线,这些缓存线代表可以在缓存和闪存或 RAM 之间传输的最小数据量。每行数据都包含将其与物理内存相关联并跟踪其状态的标签。因此,每个内存位置都可以在四个高速缓存路之一的高速缓存行中表示。

PIC32MZ 缓存实现

编辑:hfy

-

CUP缓存(L1、L2、L3)是什么2022-10-14 13826

-

什么是CPU一级缓存/二级缓存?2010-02-04 1489

-

Microchip 32位PIC32MZ EF单片机系列喜添新成员 部分器件可支持扩展级温度范围2016-11-24 1404

-

Microchip 32位PIC32MZ EF单片机系列喜添新成员, 部分器件可支持扩展级温度范围2017-02-10 493

-

AN1600 - 在PIC32MZ器件上使用L1高速缓存2018-03-26 980

-

PIC32MZ EF系列处理器主要特性及开发板框图2018-04-14 5124

-

PIC32MZ嵌入连接MCU主要特性和框图分析2018-05-03 7191

-

PIC32MZ EF——带FPU的嵌入式连接系列2018-06-07 4956

-

PIC32MZ器件系列中使用L1CPU高速缓存实现的风险和解决方法2018-06-15 1220

-

PIC32 FRM带L1CPU高速缓存的器件上的预取模块特性和操作中文概述2018-06-06 1224

-

使用PIC32MZ设计的20msps示波器资料说明2019-03-17 5928

-

在PIC32MZ器件上使用L1高速缓存2021-04-02 879

-

使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题2023-09-19 586

-

如何使用PIC32MX/PIC32MZ/PIC32MM器件上的DMA CRC生成器2023-09-25 758

-

PIC32MZ W1系列Wi-Fi SoC技术解析与应用指南2025-10-09 1059

全部0条评论

快来发表一下你的评论吧 !