如何通过通道总和增加 ADC 动态范围

描述

一种增加音频转换器系统动态范围的常用技术是使用相同的信号和输出总和并行操作两个转换器通道。相关信号的总和使信号电平增加 6 dB,而不相关噪声源的总和仅使噪声电平增加 3 dB。

CS5381 的实施要求

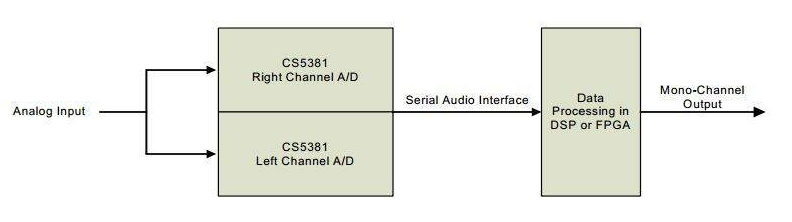

图 1 所示的框图显示了 CS5381 A/D 的实现。请注意,相同的模拟信号应用于 CS5381 内的每个 A/D 转换器。然后在数字信号处理器 (DSP) 或现场可编程门阵列 (FGPA) 中执行所需的数学运算。

需要注意的是,加法(或减法)必须使用同步采样和时间对齐的数据对来执行。在串行音频接口内,左后右声道数据对是同步采样数据。然而,右声道数据对与左声道数据对相对于彼此在时间上偏移一个采样周期,并且这些对的相加或相减将产生错误的结果。

单模框图

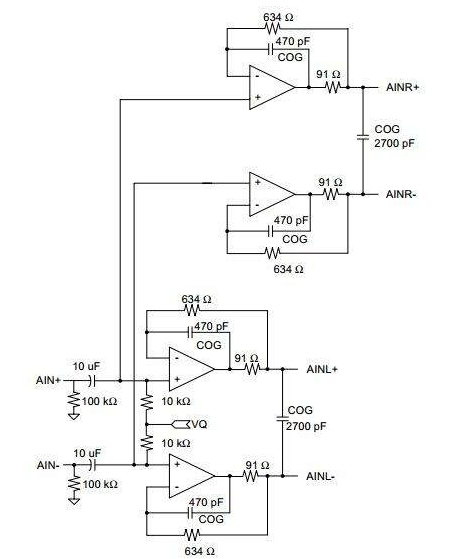

CS5381 在单声道模式下的推荐模拟输入缓冲器 CS5381的实现需要单独的输入缓冲器级用于差分模拟输入。已证明驱动两个差分输入的单个缓冲器会导致不可接受的失真水平。推荐的缓冲器拓扑与 CS5381 评估板 CDB5381 上显示的几乎相同。图 2 中的示意图是方程 eo = A/2 + B/2 的建议缓冲区实现。

CS5381 推荐的同相配置缓冲器实现

演示技术

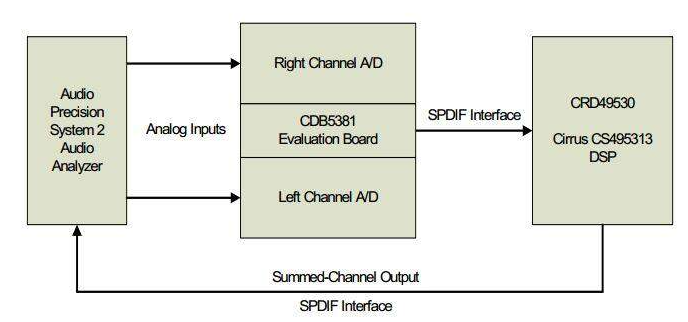

使用标准 Cirrus Logic 评估板和 Audio Precision System 2 组装测试系统来演示该技术是一件相对简单的事情。图 3 中的框图显示了一个测试设置,其中包括 CDB5381 和 CRD43530,评估CS5381 A/D 和 CS495313 音频 DSP 板。Audio Precision System 2 是模拟信号的来源,也是用于生成性能数据和绘图的分析工具。评估板和 Audio Precision System 2 之间的数字互连是标准的 S/PDIF (IEC-60958) 接口。评估是在 48 kHz 采样率下进行的,但性能改进在所有采样率下都有效。

测试系统框图

编辑:hfy

-

PCM1808的通道溢出、动态范围窄是什么原因导致的?怎么解决?2024-11-04 441

-

如何设计才能扩大SDR的动态范围呢?2015-01-29 3022

-

最大程度地扩大SDR的动态范围2018-10-10 1725

-

认识宽带GSPS ADC中的无杂散动态范围2018-11-01 1755

-

如何查询iMXRT1172 ADC输入通道电压范围?2023-03-17 510

-

无杂散动态范围(SFDR)2011-01-01 14449

-

一种多通道ADC采样板系统电路设计2014-10-31 8818

-

过采样ADC与PGA结合,提供127dB动态范围2016-01-07 808

-

采用Δ-Σ和SAR ADC的过采样模式提升ADC动态范围2019-09-14 4783

-

使用过采样增加SAR ADC的动态范围2023-01-08 4407

-

用于高动态范围的ADC,逐次逼近还是Σ-Δ2023-02-17 1958

-

增加电量计动态范围2023-03-13 1912

-

浅谈音视频ADC在动态范围上的应用2023-03-14 1351

-

通过通道求和提高音频ADC的动态范围和SNR2024-08-29 480

-

AD6600:高性能双通道增益范围ADC的技术剖析2026-04-02 121

全部0条评论

快来发表一下你的评论吧 !