低噪声放大器 (LNA) 的设备物理和参数特性

描述

无线接收器可以恢复的最弱信号由其灵敏度定义。顾名思义,低噪声放大器 (LNA) 通过降低级联噪声系数来提高接收器灵敏度。Friis 方程显示接收器链中第一级放大级的噪声系数 (F1)。

介绍

无线接收器可以恢复的最弱信号由其灵敏度定义。

Rx_sen (dBm) = -174 + 10log BW + SNR + F

其中,BW 是以 Hz 为单位的带宽,SNR 是所需的信噪比,F 是系统噪声系数。

顾名思义,低噪声放大器 (LNA) 通过降低级联噪声系数来提高接收器灵敏度。Friis 方程表明,

接收器链中第 1 个放大级(即 LNA)的噪声系数(F1)起主导作用,后续级(即 F2、F3 等)的噪声性能较小重要性。

其中,Gn 是接收链中第 n 级的增益。

蜂窝基站 (BTS) 和微波中继分离了位于天线塔上方的 LNA 级,以减轻预 LNA 电缆损耗导致的 NF 退化。在 BTS 架构中,LNA 级之前是用于双工

共用天线的发射-接收 (Tx-Rx) 双工器和用于防止带外阻塞或减敏的干扰滤波器。然而,双工器和滤波器的损耗必须最小化,因为它们发生在放大之前 [2]。因此,具有额外噪声性能余量的 LNA 将放宽双工器滤波器的损耗要求。

其他关键性能参数包括高增益以克服连接安装在塔上的 LNA 和地面无线电棚的长电缆中的损耗,以及高线性度,因为由于与其他无线设备共享站点,塔附近的 RF 频谱可能非常拥挤

发射器。

设备物理和参数特性

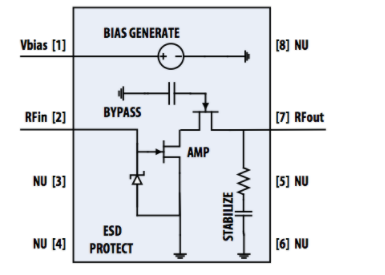

8 引脚四方扁平无引线 (QFN,2 x 2 x 0.75mm) 封装微波单片集成电路 (MMIC) 由一个共源共栅放大器和一个有源偏置稳压器组成。共源共栅拓扑具有高增益、电流重用和更好的反向隔离的优点。0.25 m 特征尺寸 GaAs 增强模式伪晶高电子迁移率晶体管 (ePHEMT) 工艺 [3] 具有高增益积带宽,fT > 30 GHz,允许目标增益(在 1.9 GHz 时 >17 dB ) 在一个级联中实现。通过将金属厚度加倍于之前的工艺迭代,可以最大限度地减少互连中产生的约翰逊噪声。

偏置调节器允许通过改变 RBIAS 或外部施加的电压 VBIAS 来调整 LNA 静态电流 (Ids)(图 1b)。稳压器的低电流驱动要求 (IBIAS ≤ 1 mA) 与大多数 CMOS 系列兼容,并且可以直接从微控制器切换 LNA,用于时域多路复用 (TDM) 应用。在电池供电的应用中,可调偏置也可用于权衡线性度以节省功耗。Ids温度稳定性是由稳压器和LNA经过类似处理实现的;即 VBIAS 和 VGS 相互“镜像”以补偿热漂移 [4] 和晶圆间跨导变化。

性能评估电路和组装

为了评估设备的射频性能,设计并制造了一个代表基站应用的 1.9 GHz LNA。最少数量的外部组件(C1-L1 和 C2-L2)提供了在芯片级集成不可行的匹配和偏置功能(图 2a)。除了 DC 阻断和 RF 扼流功能之外,C1-L1 还会在低于工作频率 (f0) 时降低不需要的增益。应为高于 f0 的自谐振频率 (SRF) 选择 L1 和 L2,以实现有效扼流。

电源去耦电容器 C3-C6 将 AC 信号分流到地,从而防止通过偏置线产生无意的输出-输入反馈。出于低频稳定性的考虑,C3 的尺寸设计为在 f0 处的电抗 (X) 约为 8 欧姆。因此,在低频时,即 f << f0,C3 表现为开路,R1(50 欧姆)直接与 L1 串联,为器件输入(引脚 2)提供低反射终端。当 LNA 在 TDM 应用中通过 VBIAS 切换时,C5 可以更改为较小的值或完全消除以提高响应时间。在 C5 中使用 10 pF 测得的开启时间约为 0.6 uS。

印刷电路板 (PCB) 的尺寸为 21.5 x 18 x 1.4 毫米,在 10 密耳罗杰斯 RO4350 上使用具有共面接地的微带 - 一种中等价位的材料,具有适中的射频性能,与 FR4 工艺兼容 [5] ]。将 1.2 毫米厚的低成本 FR4 材料粘合到 RO4350 地平面上以进行加固。RF 连接通过边缘发射 SMA 到微带转换(Johnson Component P/N 142-0701-856)进行,而直流电源通过 2 针直 PCB 接头连接。除了 C5 和 C6 由于电容大而为 0805 尺寸外,所有其他 RLC 组件均为 0402 尺寸。组件的总面积约为 8 x 10 mm2。

作为 LNA 电路设计的准备工作,MMIC 在定制设计的直通反射线 (TRL) 夹具上进行了表征,该夹具由预期原型 LNA 使用的相同 PCB 材料 (10-mil RO4350) 形成。在去嵌入夹具效应后,器件散射参数 (s2p) 然后被导入到安捷伦科技 ADS2006A 软件中进行电路仿真。创建了两个设计迭代 - 一个标准版本和一个低输入回波损耗 (IRL < -20 dB) 版本,后者在 IRL 中权衡了噪声系数 (F)(图 3)。

在 LNA 电路模型中,RLC 组件使用简化的等效电路而不是制造商提供的 s2p 数据进行建模;主要原因是 s2p 数据缺乏即时更改组件值的便利性,其次,它们的频率限制为 6 GHz(可以模拟带外稳定性)

编辑:hfy

-

LNA-20-01000200-08-10P低噪声放大器2026-01-27 554

-

基于ADS的通信设备低噪声放大器改进设计与仿真2010-04-24 2579

-

宽带低噪声放大器噪声分析2010-05-13 3298

-

低噪声放大器,低噪声放大器型号参数2017-09-11 6251

-

如何设计CDMA射频前端低噪声放大器电路?2019-08-01 2301

-

怎么设计低噪声放大器?2019-08-22 3846

-

低噪声放大器(LNA)主要应用在哪些领域?2021-04-23 4922

-

低噪声放大器介绍2021-07-27 3648

-

射频低噪声放大器电路2021-07-28 1813

-

优化噪声系数的低噪声放大器(LNA)匹配技术2006-05-07 1222

-

利用Cadence设计COMS低噪声放大器2009-07-06 3278

-

低噪声放大器,低噪声放大器是什么意思2010-03-05 4124

-

MAX2666/MAX2668低噪声放大器(LNA)2010-09-29 940

-

解读低噪声放大器的指标参数2023-06-10 6833

-

低噪声放大器的工作原理和主要参数2024-05-28 5608

全部0条评论

快来发表一下你的评论吧 !