74ls74双d触发器引脚图 74ls74双D触发器功能测试

描述

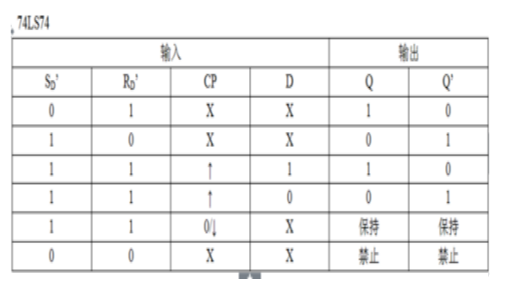

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入(

)复位输入( )、时钟输入(CP)和数据输出(Q)。

)、时钟输入(CP)和数据输出(Q)。 的低电平使输出预置或清除,而与其它输入端的电平无关。当

的低电平使输出预置或清除,而与其它输入端的电平无关。当 均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

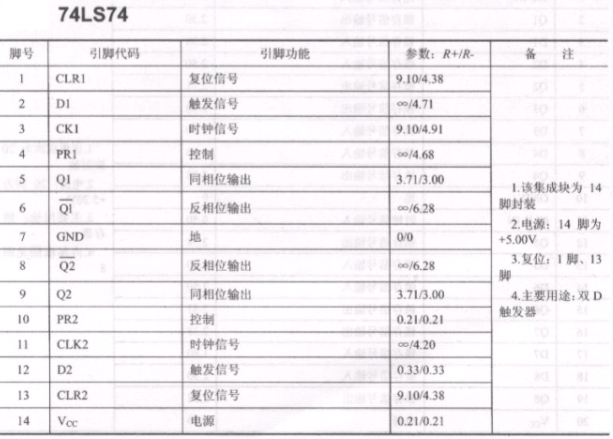

74ls74双d触发器引脚图

在ttl电路中,比较典型的d触发器电路有74ls74。74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路模块。

74ls74双D触发器功能测试

74ls74双D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

(文章内容整合自单片机教程网huqin和百度文库)

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

74LVC74:双D型正边沿触发触发器的深度解析2026-03-13 382

-

具有置位和复位功能的双D型触发器;上升沿触发-74ABT742023-02-17 1303

-

具有置位和复位功能的双D型触发器;上升沿触发-74LV742023-02-16 1078

-

具有置位和复位功能的双D型触发器;上升沿触发-74ALVC742023-02-15 674

-

CD4013或74LS74双D触发器的应用实验2022-05-11 5885

-

74LS74相关资料(中英文手册与应用实验)2018-11-28 13644

-

74ls174是D触发器吗?74ls174引脚图及功能表_逻辑图及特性2018-05-08 41903

-

74ls74中文资料汇总(74ls74引脚图及功能_内部结构及应用电路)2018-04-28 629662

-

NE555延时加74LS74触发器出现问题,求助2016-07-13 7674

-

74LS74输出信号不对2013-04-06 3410

-

D触发器/J-K触发器的功能测试及其应用2009-02-14 5551

-

74LS74中文资料pdf2008-03-22 9521

-

d触发器的芯片介绍(74系列)2008-01-22 51357

-

74ls74芯片引脚图及管脚功能2007-11-19 72880

全部0条评论

快来发表一下你的评论吧 !