A/D 转换器外部支持电路设计方案

描述

该应用笔记介绍了测量和最大化 120 dB、24 位和 96 kHz 模数转换器集成电路性能的技术。它介绍了 ADC 架构、输入缓冲器设计及其噪声要求、噪声计算和噪声分析。它还描述了外部支持电路设计和一些示例结果。

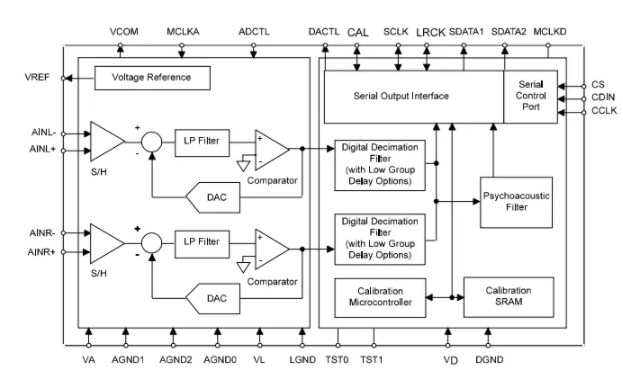

A/D 转换器架构

本次讨论中使用的 A/D 转换器由一个模拟 delta sigma 调制器芯片和一个数字滤波器芯片组成,封装在单个 28 引脚 SOIC 塑料封装中。图 1 显示了该设备的框图。delta-sigma 调制器设计的亮点包括使用三电平调制器,校准后可产生出色的线性度,调制器输出数据的新颖编码方案,可消除数据信号边沿数量和极性的数据相关变化,以及全差分设计,产生低失真和良好的共模抑制。抽取滤波器包括多个字长输出选项,以及可选的心理声学噪声整形。还包括实时使用的低群延迟。

A/D 转换器框图

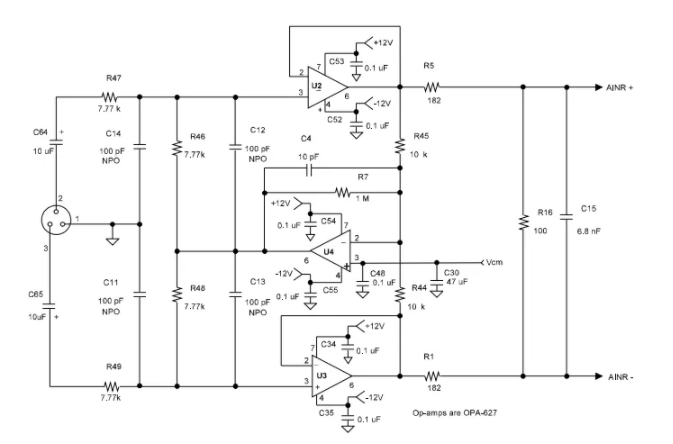

输入缓冲器设计

A/D 转换器的输入缓冲电路必须满足几个严格的要求。这些包括:可忽略的噪声贡献、DC 电平从通常以零伏为中心的输入信号转移到以 A/D 转换器的共模电压为中心的输出信号、将缓冲放大器与开关电容器电流瞬变隔离,同时保持低输出阻抗,以免引起失真,并提供适合调制器采样率的抗混叠滤波。

输入缓冲器电路图

图 2 显示了为此应用选择的伺服平衡差分输入缓冲电路。该电路通过输入端子上任一极性的差分或单端信号提供所需的差分输出。输入缓冲器的增益结构旨在衰减产生 0 dBFS 数字输出所需的 25.5 dBu (1.414 Vrms)。缓冲器输入结构中的 6 dB 衰减之后是 A/S 转换器输入处的电阻网络,它提供额外的 13.3 dB 衰减

外部支持电路设计

A/D 转换器的这种性能可能会因外部环境设计不当而降低。本节介绍 A/D 转换器周围的直接环境,包括接地层推荐、去耦电容器选择、正确的时钟发生器连接和过压保护。

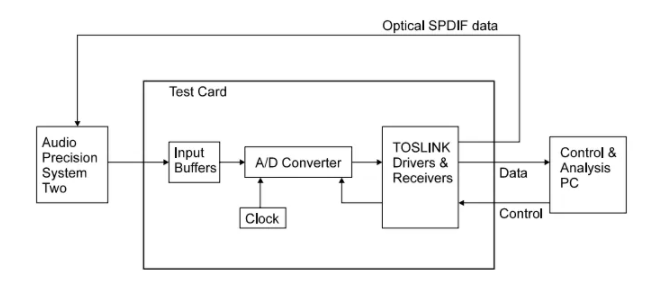

测试设置说明

测试设置信号流

图 3 显示了测试设置的主要组件。这种设置的目标是提供尽可能有利的环境,使 A/D 转换器能够发挥其最佳性能。Audio Precision System 2 用作模拟测试信号发生器,并在 48 kHz 采样率下确认一些测量结果。PC 用于通过其控制端口控制 A/D 转换器,还用于收集 96 kHz 的 A/D 转换器输出数据。在 PC 上运行的定制软件允许控制 A/D 转换器和输出数据的 FET 分析。

编辑:hfy

-

基于UC3842芯片的升压转换电路设计方案2023-07-31 2902

-

分享一款不错的高精度高速A/D转换器时钟稳定电路设计2021-04-14 1713

-

基于高分辨率A/D转换器和DL技术实现时钟稳定电路的设计2020-07-22 1650

-

电子书:DC-DC 转换器的应用与设计方案2019-03-14 7541

-

常用D/A转换器和A/D转换器介绍2012-09-05 4529

-

基于PWM实现D/A转换电路设计2011-08-26 30426

-

不用D-A转换器IC的8位廉价D-A转换电路2010-05-07 1344

-

A/D转换器的输入原理2010-01-12 889

-

电流/电压转换电路设计方案2009-12-17 7993

-

四通道 8位D A转换器AD7226在电路设计中的应用2009-06-12 1425

-

D/A转换器芯片及接口电路2009-01-14 5061

全部0条评论

快来发表一下你的评论吧 !