RL78 系列的注意事项和噪声对策分析

描述

本应用笔记介绍了 RL78 系列的注意事项和噪声对策。它描述了 PCB 上 RESET 引脚和时钟 IO 引脚的最短布线长度、跨 VSS 线和 VDD 线的旁路电容器连接、模拟输入引脚的布线以及振荡器问题,例如大电流信号线和避免电位电平频繁变化的信号线。

最短接线长度

印刷电路板上的布线可以用作天线,将噪声吸引到 MCU 中。总布线长度越短(以 mm 为单位),噪声被吸入 MCU 的可能性就越小。

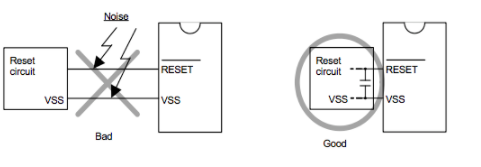

(RESET)‘ 引脚

的接线 使连接到 (RESET)’ 引脚的接线长度尽可能短。在(RESET)‘引脚和VSS引脚之间连接电容时,以及将reset IC与其对应引脚连接时,线长应特别短(20mm以内)。

原因:

输入到 (RESET)’ 引脚的脉冲宽度由时序要求决定。如果脉冲宽度比标准更短的噪声输入到 (RESET)‘ 引脚,则在 MCU 的内部状态完全初始化之前解除复位。这可能会导致程序失控。

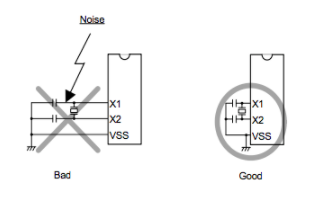

(RESET)’ 引脚的接线时钟输入/输出引脚接线

使连接到时钟 I/O 引脚的接线长度尽可能短

连接振荡器的电容器的接地线和 MCU 的 VSS 引脚之间的接线长度(在 20 mm 内)尽可能短。

时钟输入/输出引脚接线

原因:

如果噪声进入时钟输入/输出引脚,时钟波形可能不稳定。这可能会导致程序失败或程序失控。此外,如果 MCU 的 VSS 电平和振荡器的 VSS 电平之间的噪声引起电位差,则 MCU 中将不会输入正确的时钟。

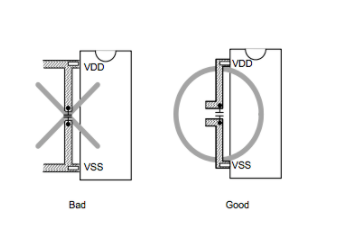

跨 VSS 线和 VDD 线连接旁路电容器

如下所述,在VSS线和VDD线之间连接大约0.1 µF的旁路电容器:

在 VSS 引脚和 VSS 引脚之间连接一个等长的旁路电容

使用尽可能短的接线在 VSS 引脚和 VDD 引脚之间连接一个旁路电容器

VSS和VDD线使用直径大于其他信号线的线

通过旁路电容将电源线连接到 VSS 引脚和 VDD 引脚。

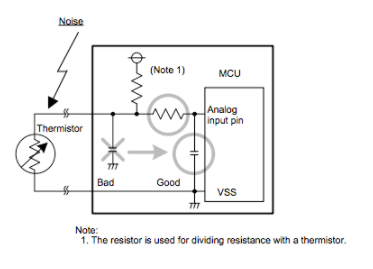

跨 Vss 线和 VDD 线的旁路电容器连接到模拟输入引脚

将大约100Ω至1kΩ的电阻连接到模拟信号线,该信号线串联连接到模拟输入引脚。将电阻尽可能靠近 MCU。

在模拟输入引脚和 VSS 引脚之间插入一个大约 1000 pF 的电容器,使其尽可能靠近 VSS 引脚。模拟输入引脚和电容器之间的导线以及VSS引脚和电容器之间的导线应等长。

模拟信号线、电阻器和电容器

原因:

输入到模拟输入引脚的信号通常是来自传感器的输出信号。大多数检测事件的传感器都远离安装了 MCU 的电路板。模拟输入引脚的接线不可避免地更长。这条长接线起到天线的作用,将噪声吸引到 MCU 中,从而对模拟输入引脚产生噪声。

编辑:hfy

-

使用IAR IDE仿真RL78内置硬件乘法器和除法器注意事项2023-10-30 2199

-

EEPROM 仿真软件 RL78 Type 02RL78/F23 和 RL78/F24 用户手册2023-05-19 520

-

Renesas Flash Driver RL78 Type 02RL78/F23 和 RL78/F24 用户手册2023-05-12 515

-

E1/E20 Emulator, E2Emulator Lite 用户手册附加文件(RL78连接注意事项)(for RL78/G10, RL78/G1M, RL78/G1N)2023-03-13 673

-

RL78族噪声的相关注意事项及对策应用说明2023-02-09 1180

-

RL78系列IECUBE可选产品列表2023-01-11 393

-

RL78/G23 Data flash使用教程2022-09-09 4281

-

RL78 dataflash pfdl库使用教程2021-07-23 2523

-

瑞萨电子推出的RL78/I1x系列微控制器是RL78微控制器系列2018-08-01 6617

-

介绍MCU的新系列RL78产品的特点与应用2018-06-14 4024

-

RL78学***2015-01-04 22289

全部0条评论

快来发表一下你的评论吧 !