开关电容式模数转换器(ADC)的框图介绍

描述

随着消费电子设备尺寸的不断减小和复杂性的增加,强烈要求将越来越多的功能集成到单个芯片上。进行这种集成的原因很多。电路板设计变得更简单,需要放置的设备更少,布线的互连更少。

在纯数字环境中,集成以惊人的速度发展。在过去的十年中,数字集成已从根本上改变了DVD播放器,AVR和MP3播放器等消费类电子产品的系统设计。消费者已经重复了更快,更便宜和更小的消费电子设备的好处。当人们试图合并信号路径的模拟和数字部分时,这种集成路径变得更加困难。在许多消费电子应用中,大型数字片上系统(SoC)IC已开始包含此模拟功能。这里的挑战是极端的。尽管进行了许多工艺改进,例如深n阱技术,该技术将模拟电路与数字核隔离开来,设计人员最终试图将高性能模拟转换器与快速且嘈杂的数字信号处理器(DSP)放置在同一基板上。迄今为止,很少有设备能够将其真正的高性能转换器和高速DSP推向市场。为了解决这一挑战,有必要研究对芯片上数字电路的干扰较不敏感的新型转换器架构。

传统的开关电容架构

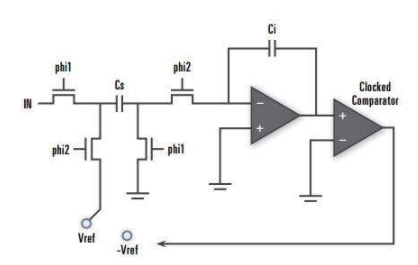

大多数现代音频转换器都采用开关电容架构。图1给出了简化的开关电容式模数转换器(ADC)的框图。

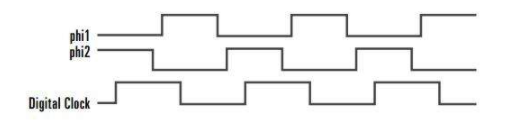

开关电容器DAC的架构相似,尽管随后的讨论将重点放在ADC上,但分析也适用于DAC。在ADC中,将输入音频信号采样到采样电容器tex_C_ {s} [/ tex],然后传输到积分电容器tex(C_ {i})[/ tex]。使用两相时钟,其中输入在phi1上采样,并与phi2上的反馈信号±Vref一起传输到积分电容器。该架构的关键时间是phi1开关断开,而phi2开关闭合。这是采样输入信号并将其提供给积分器的时间点。输入或地面上的任何噪声都将被采样并出现在ADC输出中。转换器设计中的一种常用技术是对数字时钟计时,以使其在采样事件之后发生。

数字时钟的边缘将始终将与信号相关的噪声注入到基板中,该基板将找到通往参考节点或采样电容器接地节点的路径。只要在采样事件之后发生数字边沿,就不会在ADC输入端采样到任何噪声。

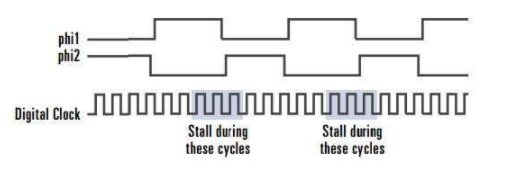

在独立转换器中,这种噪声管理易于实现。所有时钟通常都来自单一来源,因此确保模拟和数字时钟之间的时序关系非常简单。即使数字时钟比模拟时钟快,也很容易找到安全区域来放置这些数字边沿。在一个复杂的DSP上,异步数字内核的运行速度可能比转换器要快得多,这个问题要困难得多。图3显示了问题的性质。

无法保证采样事件的安全时间。在某些解决方案中,DSP只是停顿了多个周期以创建一个安全的采样事件,如图3中的阴影框所示。这可以有效地消除DSP与转换器之间的耦合,但这样做的代价是MIPS。假设典型的6.144 MHz转换器时钟和98.3 MHz DSP时钟(转换器时钟的16倍)。如果选择使处理器停顿3个时钟,以确保采样事件周围有一定余量,那么这将消耗芯片处理能力的近20%。

编辑:hfy

-

直方图测试模数转换器(ADC)介绍2023-10-17 4060

-

ADC模数转换器介绍2023-06-26 5576

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1712

-

模数转换器ADC简介2022-02-17 1702

-

ADC0809模数转换器主要特性2021-12-02 3531

-

STM32之ADC模数转换器介绍2021-11-08 3163

-

介绍STM32的模数转换器(ADC)2021-08-24 1239

-

ADC模数转换器2021-08-06 1973

-

模数转换器(ADC)的基本原理是什么2021-07-26 1680

-

模数转换器(ADC)的配置有哪些流程?2021-07-14 3028

-

ADC模数转换器相关资料下载2021-07-01 1041

-

5962-9581501HXA高端AD模数转换器2020-07-15 2125

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3460

-

数模和模数转换器2009-09-16 7655

全部0条评论

快来发表一下你的评论吧 !