CS556X/7X/8X与SAR转换器的相似性和比较

描述

本应用笔记介绍了CS556x / 7x / 8xΔ-Σ模数转换器及其与SAR(逐次逼近寄存器)转换器的相似性和比较。本文档还描述了对CS556x / 7x / 8进行复用的要求,复用器的选择以及驱动ADC的放大器和用于复用CS556x / 7x / 8x ADC的优化电路。

比较CS556X / 7X / 8X与SAR

过去,通常将SAR ADC用于任何高吞吐量多路复用应用。这是因为大多数delta-sigma转换器需要多次转换才能完全稳定。换句话说,输入上的较大阶跃变化需要花费大量时间才能在数字滤波器的输出中准确反映(确定)。大多数delta-sigma转换器使用单位调制器并以千赫兹速率采样,并且需要许多采样作为数字滤波器的输入,以实现所需的精度。CS556x / 7x / 8x系列转换器的独特之处在于,调制器输出为多位,采样率为8 MSps(每秒兆采样)。结合专门设计的FIR滤波器,该滤波器仅需要几个时钟周期来计算结果,就可以产生一个可以完全实现单次转换的转换器

CS556X / 7X / 8X的复用要求

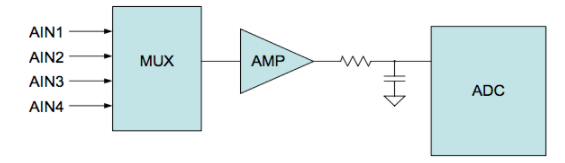

对于多路复用应用中的更高吞吐量,希望转换器完全满足每次转换的要求。换句话说,在转换期间,数字滤波器的输出必须在输入上准确反映模拟值。此外,在采样之前,必须将输入多路复用器和任何缓冲放大器设置为转换器的全部精度。这要求转换器和模拟输入电路都必须快速建立。如图1所示,如果在多路复用器和ADC之间放置任何放大器或抗混叠电阻和电容器,则尤其如此。通过多路复用器,ADC输入有可能看到从一次转换到满量程的满量程变化。下一个。任何放大器,或由于电阻和电容引起的RC时间常数,

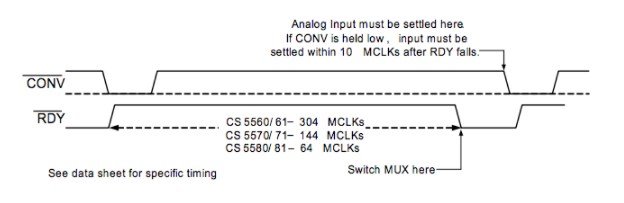

多路复用器与ADC之间的放大器和滤波器使用50 kSps CS5560 / 61、100 kSps CS5570 / 71或200 kSps CS5580 / 81等高吞吐量转换器,电路必须在少于10 MCLK的周期(625纳秒)内稳定下来。由于已经对信号进行了采样,因此可以在转换开始后将SAR转换器之前的多路复用器切换到下一个通道。但是,许多SAR ADC数据手册警告说,应注意一定的“安静”时间段,以防止噪声耦合。CS556x / 7x / 8x要求在转换结束时切换多路复用器,因为在转换过程中它将对输入信号进行多个采样(见图2)。

多路复用器时序要求

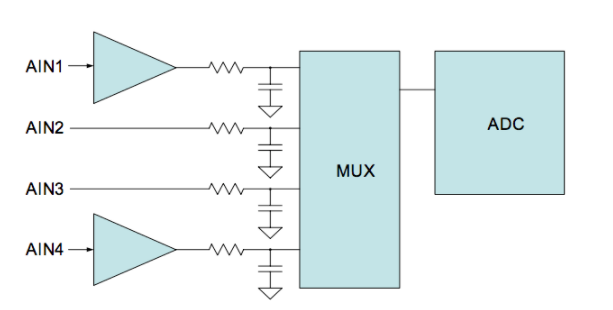

因此,在多路复用器的输入端上有放大器和抗混叠电容器的情况下,应考虑采用另一种方法。这通常需要一个具有非常低“导通”电阻的多路复用器,但是好处是,当多路复用器切换到另一个输入时,放大器和RC网络不必从可能的大阶跃变化中稳定下来。图3示出了这种布置。

放大器和滤波器放置在多路复用器之前

如图所示,并非每个输入都可能需要放大器或缓冲器。这是因为CS556x / 7x / 8x中有一个片上缓冲器。该粗糙的电荷缓冲器通过使用来自电源引脚而非输入引脚的电流将内部采样电容器充电至非常接近输入电压的值,从而将输入端的采样电流降至最低。这样会在模拟输入上产生更高的有效阻抗。需要更改满量程范围的地方,可以使用具有增益或衰减的放大器。

选择一个多路复用器

选择MUX设备时,需要考虑几个关键参数。这些包括“导通”电阻,导通/关断电容和开关速度。导通电阻应尽可能低,以确保ADC的输入完全稳定在每个采样上。现代转换器的输入包括一个模拟开关和一个采样电容器。对于大多数SAR转换器,该采样电容器(或电容器阵列)在70 pF至100 pF的范围内,每次转换必须充电一次。对于CS556x / 7x / 8x,输入采样电容器仅为4 pF,但每125纳秒(8 MHz采样频率)采样一次。CS556x / 7x / 8x还包括一个粗充电缓冲器,该缓冲器可将采样电容器充电至接近其最终值,然后再将采样电容器直接切换到精细采样周期的输入引脚。这大大增加了设备的有效输入阻抗。但是,此精巧采样周期仅是每个125纳秒采样周期中的20纳秒,因此输入路径中的过大电阻可能会导致沉降不足。导通电阻应保持较低的另一个原因是,多路复用器的导通电阻在ADC的整个量程范围内都是非线性的,这可能会导致失真。导通电阻越低,这种非线性将导致失真越小。通常,应使用小于10欧姆的导通电阻,以使对ADC的采样电容充电时的建立延迟最小。因此输入路径中的电阻过大可能会导致沉降不足。导通电阻应保持较低的另一个原因是,多路复用器的导通电阻在ADC的整个量程范围内都是非线性的,这可能会导致失真。导通电阻越低,这种非线性将导致失真越小。通常,应使用小于10欧姆的导通电阻,以使对ADC的采样电容充电时的建立延迟最小。因此输入路径中的电阻过大可能会导致沉降不足。导通电阻应保持较低的另一个原因是,多路复用器的导通电阻在ADC的整个量程范围内都是非线性的,这可能会导致失真。导通电阻越低,这种非线性将导致失真越小。通常,应使用小于10欧姆的导通电阻,以使对ADC的采样电容充电时的建立延迟最小。

选择放大器

如果需要一个放大器来改变满量程范围或缓冲输入,并将其放置在MUX与ADC之间,则最关键的参数之一就是建立时间。但是,如上所述,如果将放大器放置在MUX之前(需要时在MUX的每个输入上放置一个),则可以大大放宽这一要求。在这种情况下,信噪比,失真,DC偏移和整个温度范围内的稳定性成为大多数应用的主要选择标准。每个应用程序都将确定最关键的参数,因此很难指定一种适用于所有情况的运算放大器和电路配置。CS3003和CS3004运算放大器具有出色的DC性能,适中的带宽和低噪声,因此将适合许多应用。

用于多路复用CS556x / 7x / 8x ADC

的优化电路以下是为许多通用应用优化CS556x / 7x / 8x系列高吞吐量ADC性能的电路示例。每个电路后都有简短的电路说明,并注明了关键的选择标准。

编辑:hfy

-

AD9777:16位160 MSPS 2x/4x/8x内插双TxDAC+®D/A转换器数据表2021-04-30 1089

-

AD9773:12位、160 MSPS 2x/4x/8x插值双TxDAC<sup>®</sup>D/A转换器数据表2021-04-15 887

-

荣耀8X和荣耀10青春版哪个好2019-07-19 12741

-

荣耀8XMax和荣耀8X的区别2019-07-18 13740

-

小米6X和荣耀8X哪个好2019-07-01 5896

-

荣耀8X系列评测 无可置疑的口碑2018-11-16 10157

-

荣耀8X和荣耀8X max对比分析2018-10-07 50763

-

荣耀8X与小米6X如何选择2018-09-23 16155

-

国外也玩应用双开,外国媒体送你荣耀7X手机6条小贴士_华为荣耀畅玩7x值得买吗2017-12-17 3646

-

HTC 8X和8S价格_HTC 8X和8S报价_HTC 8X和8S多少钱2012-09-20 7245

全部0条评论

快来发表一下你的评论吧 !