模拟和数字电路交互相互作用的混合信号设计

描述

Mentor的Symphony混合信号仿真平台看起来将成为设计师工具箱中最有价值的工具之一

混合信号设计是指涉及模拟和数字电路交互相互作用以达到设计目的的设计。验证这种设计非常棘手,特别是在采用最新的工艺几何尺寸(例如当今的7纳米技术)的最新,最大型硅芯片(ASIC,ASSP,SoC)的情况下。

这种设计很少在模拟和数字之间平均分配(这种设计称为A / D或“ Big'A,Big'D'”)。取而代之的是,模拟可能会占主导地位,在这种情况下,设计可能被称为A / d(“大A”,“小D”),“模拟为主”或“顶部模拟”。替代地,并且非常普遍地,数字可能占主导地位,在这种情况下,设计可以称为a / D(“小A”,“大D”),“以数字为主导”或“顶部数字”。

除了一个或多个处理器内核之外,现代SoC可能还包含数亿个逻辑门,这些逻辑门必须与拥有大量模拟内容的功能接口并进行验证,例如PLL,ADC,DAC,SerDes,DDR IO等。清单继续。

还有一个事实,就是设计正变得越来越深奥。例如,“顶置数字”芯片可以调用多个模拟IP功能,其中许多本身可以实例化数字子功能以进行控制和校准。

混合信号设计在广泛的应用和细分市场中扮演着关键角色,每个应用和细分市场都具有不同的优先级,例如物联网(低功耗),通信(高速),数据中心(低功耗和高速)以及汽车(可靠性)。

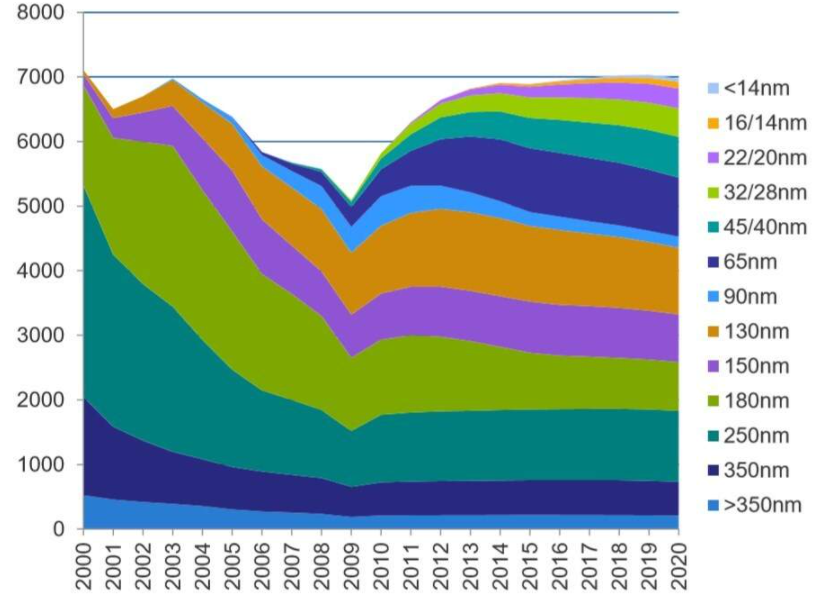

混合信号细分市场(来源:Mentor,西门子业务)

实际上,当今大约80%的芯片设计开始都是混合信号。至少可以这么说,以创新的电路拓扑和复杂的模数交互来验证这种能力的设备具有挑战性,并且现有的混合信号验证解决方案已开始精疲力尽。

混合信号设计从流程节点开始。(来源:IBS)

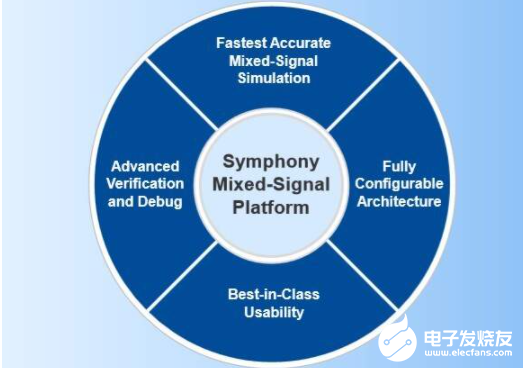

高性能计算,物联网(IoT)和汽车应用中使用的片上系统(SoC)设备具有多个高性能,低噪声混合信号接口。为了满足此类设计的混合信号验证需求,西门子业务部门Mentor宣布推出其Symphony混合信号平台,该平台将其代工厂认证的模拟FastSPICE(AFS)电路仿真器与业界认可的仿真器相结合。标准的HDL仿真器,可以快速,准确地验证复杂的纳米级混合信号集成电路。

Symphony混合信号平台(来源:Mentor,西门子业务)

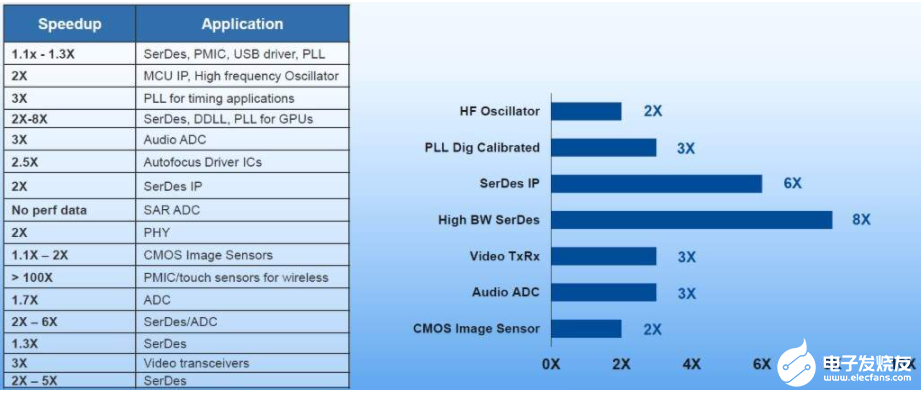

AFS模拟求解器最多可扩展至16个处理器内核,并支持支持布局后仿真所需的高容量,在提供出色性能的同时还提供了纳米SPICE精度。Symphony的完全可配置体系结构可扩展到Mentor的所有模拟求解器,还支持行业领先的数字求解器,从而最大程度地重用了现有的验证基础架构。与传统的混合信号模拟器相比,其结果是可以显着提高性能。

Symphony性能提升与传统混合信号模拟器的对比(来源:Mentor,西门子业务)

Symphony提供了一个简单直观的使用模型,并与Mentor的EZwave Viewer集成在一起,该模型能够处理巨大的波形数据库并在几秒钟内加载千兆字节的数据。EZwave可以分析任何类型的时域或频域波形:模拟,数字,眼图,史密斯圆图,极坐标图或复数图以及直方图。Symphony还提供了多种提高生产力的功能,包括广泛的A / D边界元素支持,以及大量的高级验证和调试功能,包括Hi-Z检测,混合信号瞬态噪声和混合信号IP表征。

当今难以置信的复杂,高容量,高性能混合信号集成电路的创建者需要他们所能获得的所有帮助,而Mentor的Symphony混合信号仿真平台似乎已成为设计师工具箱中最有价值的工具之一。

编辑:hfy

-

模拟电路与数字电路的区别2025-01-24 3266

-

模拟电路和数字电路的概念是什么2024-08-22 3872

-

模拟电路和数字电路到底有什么区别?2024-03-05 3915

-

什么是电磁相互作用2020-01-31 6348

-

数字电路模拟特性的信号完整性2019-08-22 2584

-

什么是模拟电路 什么是数字电路2018-10-16 103862

-

模拟电路和数字电路PCB设计的区别2018-09-26 4240

-

混合信号示波器探测模拟和数字信号的方法2017-10-15 927

-

模拟电路与数字电路的区别详解2017-05-23 8352

-

模拟和数字电路基础知识汇总2016-11-19 3266

-

模拟电路和数字电路PCB设计的区别详解2016-11-08 4083

-

模拟电路和数字电路的学习笔记2016-09-20 896

-

模拟电路和数字电路合集2016-07-25 1154

全部0条评论

快来发表一下你的评论吧 !