IBM全球首款2nm芯片制程 IBM 2纳米芯片制造技术要点

描述

IBM Research在其纽约奥尔巴尼技术中心宣布其突破性的2nm技术的消息。

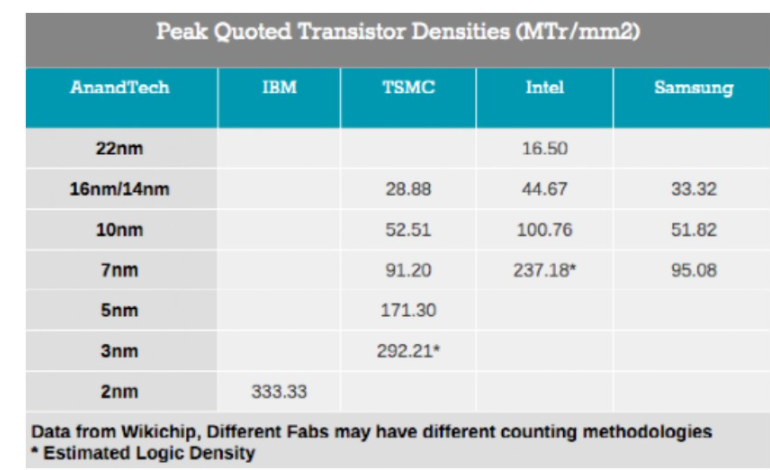

据IBM官方表示,核心指标方面,IBM称该2nm芯片的晶体管密度(MTr/mm2,每平方毫米多少百万颗晶体管)为333.33,几乎是台积电5nm的两倍,也比外界预估台积电3nm工艺的292.21 MTr/mm2要高。

换而言之,这种技术能在指甲盖大小(150mm)的芯片上安装500亿个晶体管。相比于7nm芯片,这种技术预计将提升45%的性能、并降低75%的能耗。

不过,这并不意味着IBM就具备量产2nm芯片的能力,因为这项技术是在它位于纽约州奥尔巴尼(Albany)的芯片制造研究中心做出来的,但量产还涉及许多其他技术。

据报道,目前担任IBM混合云研究副总裁的Mukesh Khare带领其完成了2纳米技术的突破。

资料显示,Khare在1999年到2003年间,从事90纳米SOI工艺的开发,该工艺将Power4和Power4 +推向市场,他随后又负责了65纳米和45纳米SOI的推进,这些技术被Power5和Power6采用;之后他对对用于Power7的32纳米技术进行了研究,然后研究了在Power8上使用的22纳米工艺中使用的高k /金属栅极技术。之后,Khare继续担任奥尔巴尼纳米技术中心的半导体研究总监。

IBM的全球首个2纳米2nm跟传统谈论的线宽不一样

在过去,这个尺寸曾经是芯片上二维特征尺寸的等效度量,如90纳米、65纳米和40纳米。

然而,随着FinFET和其他3D晶体管设计的出现,现在的工艺节点名称是对“等效2D晶体管”设计的解释。一般用晶体管密度可以更准确的衡量,如同英特尔倡导的那样。

例如,英特尔的7纳米工艺将与台积电的5纳米工艺大致相同;台积电的5纳米工艺也甚至没有50%的改进(它比7纳米工艺只提供15%的改进),所以称其为5纳米工艺本身就有点牵强。根据IBM的说法,他们的“2纳米”技术比台积电的7纳米工艺有大约50%的改进,这样以来——即使按照当今最宽松的标准,也顶多是3.5纳米技术。

通过下表可以获得更好的比较:

不同的代工厂有不同的官方名称,有各种密度。值得注意的是,这些密度数字通常被列为峰值密度,用于晶体管库,其中芯片面积是峰值关注点,而不是频率扩展--由于功率和热方面的考虑,通常处理器最快的部分的密度是这些数字的一半

但这不代表IBM的新消息没有技术含量。

IBM 2纳米芯片制造技术要点

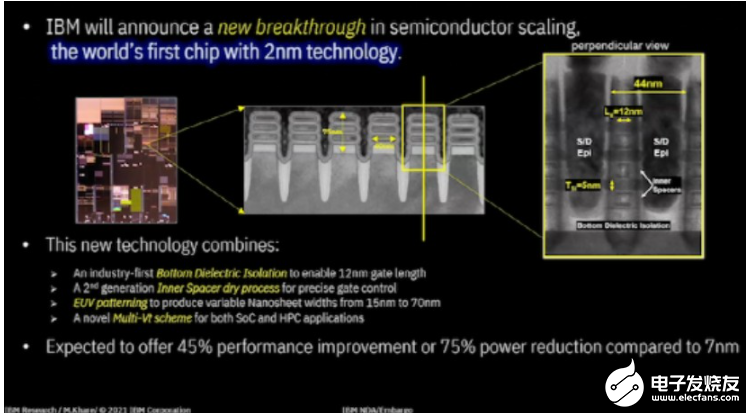

如下图所示,这是IBM掌握的2纳米芯片制造技术的要点。

首先,在这个芯片上,IBM用上了一个被称为纳米片堆叠的晶体管,它将NMOS晶体管堆叠在PMOS晶体管的顶部,而不是让它们并排放置以获取电压信号并将位从1翻转为零或从0翻转为1。这些晶体管有时也称为gate all around或GAA晶体管,这是当前在各大晶圆厂被广泛采用的3D晶体管技术FinFET的接班人。从以往的介绍我们可以看到,FinFET晶体管将晶体管的源极和漏极通道拉入栅极,而纳米片将多个源极和漏极通道嵌入单个栅极以提高密度。

IBM表示,其采用2纳米工艺制造的测试芯片可以在一块指甲大小的芯片中容纳500亿个晶体管。

在IBM的这个实现方案下,纳米片有三层,每片的宽度为40纳米,高度为5纳米。(注意,这里没有测量的特征实际上是在2纳米处。因为这些术语在很大程度上是描述性的,而不是字面意义的,这令人发指。可以将其视为如果栅极仍为平面则必须具有的栅极尺寸,但却不是平面的,我想可能是这样。)如果您在上表的右侧看,那是一张纳米片的侧视图,显示出它的侧视图,其间距为44纳米,栅极长度为12纳米,Khare认为这是其他大多数晶圆代工厂在2纳米工艺所使用的尺寸。

2纳米芯片的制造还包括首次使用所谓的底部电介质隔离(bottom dielectric isolation),它可以减少电流泄漏,因此有助于减少芯片上的功耗。在上图中,那是浅灰色的条,位于中部横截面中的三个堆叠的晶体管板的下面。

IBM为2纳米工艺创建的另一项新技术称为内部空间干燥工艺(inner space dry process),从表面上看,这听起来不舒服,但实际上这个技术使IBM能够进行精确的门控制。

在实施过程中,IBM还广泛地使用EUV技术,并包括在芯片过程的前端进行EUV图案化,而不仅是在中间和后端,后者目前已被广泛应用于7纳米工艺。重要的是,IBM这个芯片上的所有关键功能都将使用EUV光刻技术进行蚀刻,IBM也已经弄清楚了如何使用单次曝光EUV来减少用于蚀刻芯片的光学掩模的数量。

这样的改善带来的最终结果是,制造2纳米芯片所需的步骤要比7纳米芯片少得多,这将促进整个晶圆厂的发展,并可能也降低某些成品晶圆的成本。这是我们能看到的。

最后,2纳米晶体管的阈值电压(上表中的Vt)可以根据需要增大和减小,例如,用于手持设备的电压较低,而用于百亿超级计算机的CPU的电压较高。

IBM并未透露这种2纳米技术是否会采用硅锗通道,但是显然有可能。

与当前将使用在Power10芯片的7纳米制程相比,这种2纳米制程有望将速度提高45%或以相同速度运行,将功耗降低75%。

IBM 2纳米芯片潜在的好处

据IBM称,这项先进技术的潜在好处可能包括:

手机电池寿命翻两番,只要求用户每四天给他们的设备充电一次。

减少数据中心的碳足迹,这些中心占全球能源使用量的1%,即5.8亿兆焦耳。将他们所有的服务器改为基于2纳米的处理器,有可能大大减少这一数字。

大大加快笔记本电脑的功能,从快速处理应用程序,到更容易地协助语言翻译,到更快的互联网访问。

有助于加快自动驾驶汽车等自主车辆的物体检测和反应时间。

另外,这项技术将使数据中心的电源效率、太空探索、人工智能、5G和6G以及量子计算等领域受益。

实验室做出来≠量产

一个工艺从实验室出来,到大规模量产,过程中需要芯片代工厂不断提升晶圆良率。

晶圆良率,指完成所有工艺步骤后,测试合格的芯片的数量与整片晶圆上的有效芯片的比值。

因此,晶圆良率决定了芯片的工艺成本。

要是一个工艺的晶圆良率上不去,量产可能反而会导致芯片亏损。

而目前,IBM的2nm芯片还停留在实验室阶段,只是制造出来而已。

除此之外,也还需要考虑光刻机等工具的进展。

比较有意思的是,IBM现在是没有大规模量产芯片的能力的,更可能将这项工艺交给三星等芯片制造商代工(目前已与英特尔和三星签署联合开发协议)。

IBM虽然曾经也是芯片制造商之一,却在2014年将自己的晶圆厂出售给了格罗方德(据说IBM还向格罗方德交了15亿美元,才把晶圆厂塞给它)。

编辑:hfy

-

IBM首发2nm芯片 采用GAA技术2022-07-05 1872

-

IBM发布全球首个2纳米芯片制造技术2022-07-04 3507

-

IBM发布的2nm芯片都采用了哪些技术2022-07-01 2562

-

全球首款2nm芯片问世 2nm芯片带来的突破2022-06-29 4644

-

美国科技企业IBM发布全球首个2nm制程芯片2022-06-27 2089

-

IBM发布全球首个2nm芯片2022-06-24 1901

-

ibm的2nm芯片究竟有多强 2nm芯片对续航的影响2022-06-23 3208

-

IBM宣布造出全球首颗2nm EUV芯片 精选资料分享2021-07-20 6179

-

IBM重磅发布了全球首个2nm芯片制造技术2021-05-10 3218

全部0条评论

快来发表一下你的评论吧 !