基于微控制器系统的示波器与逻辑分析仪

描述

混合信号示波器(MSO)成为每个人的“工程”瑞士军刀,为什么有人需要额外的逻辑分析仪?现在,采样率在GHz范围内并且有8条或更多条数字线路的MSO的价格远低于3,000美元,有些甚至低于1,000美元。因此,电子行业中的许多人都宣布将逻辑分析仪作为一种独立的设备淘汰。

如今,在大多数电子工程实验室中都可以找到混合信号示波器也就不足为奇了。它们用途广泛,价格合理,并且已成为测试,调试或验证电子系统的任何工程师的基本工具。实际上,这可能是大多数电子工程师将不得不使用的唯一仪器,或者可能要在其90%的实验室时间中使用。因此,明智的做法是将一部分初始工程或测试实验室预算花在MSO上。但这是否意味着不再需要逻辑分析仪(LA)?

示波器与逻辑分析仪

数字示波器和逻辑分析仪基于采样技术。信号(通常是电压)的测量值由高速模数转换器(ADC)转换为数字值,并按仪器的采样时钟定义的固定时间间隔存储到内存中。

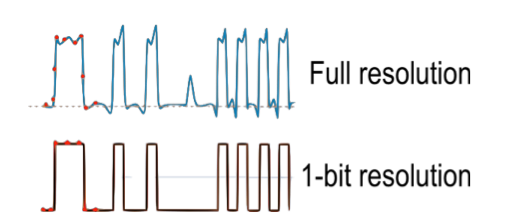

可以将逻辑分析仪视为在所有通道上具有1位垂直分辨率的示波器。根据测得的电压是高于还是低于称为“阈值”的常规电压电平,它将信号显示为逻辑(二进制)值。这是示波器和逻辑分析仪之间的第一个基本区别。

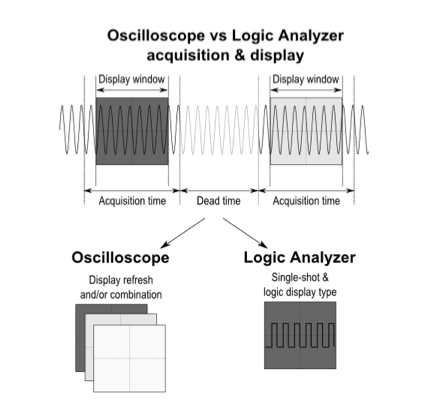

示波器和逻辑分析仪之间的另一个基本区别是采样值的显示方式。在最常见的操作模式下,示波器本质上是一种设备,可以重复捕获给定长度(由其总内存定义)的事件窗口,并刷新其在屏幕上的一部分显示。许多示波器通过在显示器上叠加多个捕获的窗口并调制屏幕像素强度来模拟“持久性”。

逻辑分析仪主要用于单次捕获(不叠加连续捕获),并分析触发事件前后有时超过100个数字信号的事件序列。

基于微控制器的系统的出现要求创建诸如逻辑分析仪之类的工具。首先,需要观察数字总线,因此需要两个或四个以上的通道。其次,需要以二进制值的形式查看逻辑电路的工作方式,即在电路的采样事件时看到的信号。随着时间的流逝,逻辑分析仪已发展成为“纯”仪器,能够执行一些模拟测量,例如用于检查阈值水平,检测毛刺以及验证信号是否符合特定输入输出标准。

“实时”,真的吗?

听到实时显示功能是示波器和逻辑分析仪之间的主要区别是很常见的。实际上,自动显示刷新可能会使用户误以为用户会在数据出现时看到数据。但是,示波器显示的刷新速度并没有眼睛真正看到的快。在大多数情况下,首先通过捕获数据然后对其进行分析来使用逻辑分析仪(LA)。逻辑分析仪的重复触发功能还可以基于重复发生的触发事件来刷新显示。的确,数据在数字示波器和LA中的显示和呈现方式是不同的,但是从根本上说,这两种工具都是通过对信号进行采样并将采样存储到内存中来进行操作的。

MSO =示波器+逻辑分析仪?

好吧,主要是。混合信号示波器具有模拟通道(通常为2至4个)和数字通道(通常为8至16个)。在这两种类型的通道上,数据均以MSO的最大采样率(通常为1GHz)进行采样。采样时钟通常由MSO内部产生。换句话说,用于采样的参考时基与数据不相关。这就是所谓的“时序分析”。当然,对于数字通道,逻辑分析仪的垂直信号分辨率降低到1位。

MSO能够执行传统上保留给LA的某些功能:–对数字信号进行时序分析。–能够观看2个或4个以上频道;在现代MSO上,有16个数字输入可用。–数字信号完整性检查。

在这方面,与分别使用示波器和逻辑分析仪相比,能够在同一屏幕上可视化数字信号的模拟扩展及其数字版本无疑是一项改进。随着电子系统向更加复杂的方向发展,调试通常涉及发现模拟和逻辑问题的混合体。MSO的触发可以通过任何一种信号来定义。也可以使用重复(类似示波器)或单次(类似逻辑分析仪)的显示类型。但是,将模拟和数字记录与时间相关数据显示在同一屏幕上是MSO的最大优势之一。

急需的MSO

当您认为需要逻辑分析仪时,请考虑以下事项:

1.逻辑分析仪具有比MSO多的数字通道。

传统台式逻辑分析仪最多可以计数128个数字通道。在MSO上,通常最多有16个通道。大量洛杉矶用户,专用集成电路(ASIC)和现场可编程门阵列(FPGA)设计工程师通常需要32到64个信号甚至更多信号来解码总线事务或可视化FPGA内部。但是,尽管有80%到90%的时间,但即使您参与IC设计,16个数字通道也足够了。您希望看到100个并行数字信号的罕见的1%到10%的情况可能不足以证明对可能花费超过20,000美元的高端100通道逻辑分析仪进行投资的合理性。

FPGA设计是大型通道数逻辑分析仪曾经用作调试基本设备的领域。在板上添加一个连接器并通过其输入-输出观察芯片,甚至将调试连接器置于芯片到芯片的互连中对于解决设计问题非常有用。但是,由于其可编程的性质,FPGA允许通过简单地将它们路由到连接到LA的输入输出来监视许多内部节点。

事情变了; FPGA世界正变得如此先进,以至于即使您可以并行看到100个,通过外部数字输入输出观察芯片的行为也不再有意义。如今,FPGA的内部运行速度可能超过300 MHz,在板上放置100引脚高速并行连接器会带来过多的板级约束(噪声,层数,串扰等)。此外,芯片输入输出缓冲器有时无法以与芯片内部相同的速度运行。其他方法,例如使用嵌入式逻辑分析仪或基于软件的调试,现在已经变得更加高效和具有成本效益。

必须谨慎考虑逻辑分析仪与MSO相比的“数字通道优势”。对于大多数工程师而言,16到32条数字线路就足够了。在绝对需要并行查看更多数字信号的情况下,具有68至100个甚至更多通道的逻辑分析仪会有所作为。但是,这必须与将所需的调试连接器添加到系统的约束条件进行仔细平衡。在数字复杂度向芯片内部转移的情况下,越来越难以探测高频信号而不产生信号或数据完整性问题。因此,在具有大量通道的逻辑分析仪中通常投资不到20,000美元可能是值得的。

2.逻辑分析仪的内存比MSO大。

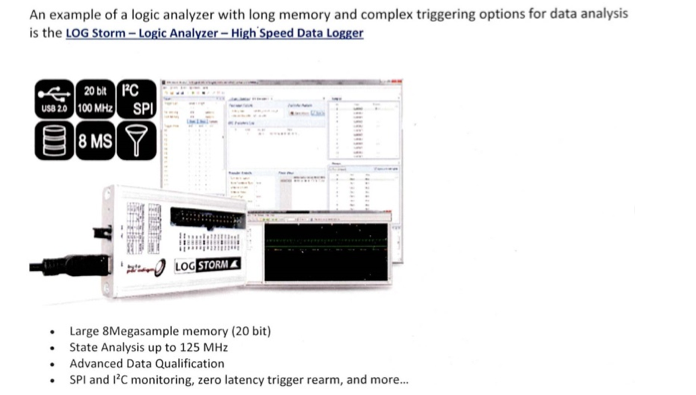

尽管由于MSO设备的不断发展可能会有例外,但是逻辑分析仪的一个潜在优势在于,它可以证明将其添加到现有MSO设置中是合理的,因为它有助于查看触发事件前后更长的时间范围。在调试过程中,看到执行数字系统的时间较长很有价值。它有可能加速对错误发生原因的了解,从而加快错误纠正的速度。它可以很快收回成本!逻辑分析仪中较大的总可用存储器大小,除了MSO之外,还增加了很多价值。大容量存储意味着可以看到更多观察到的信号历史。

3.逻辑分析仪比MSO允许更复杂的触发或数据过滤。

可用内存总量不是要考虑的唯一参数。仪器如何使用存储器存储数据也同样重要。可以观察到多少信号历史记录?这些信息在调试被测系统中有多大用处?考虑一下逻辑分析仪和MSO如何选择数据。

大多数MSO能够在简单事件(例如电压电平或数字值)上触发,或在特定数字线上转换。如果它们还提供简单的串行总线解码(例如I²C或SPI),则MSO还可用于利用串行触发,即在数字线上发生预定义的串行值时停止捕获。

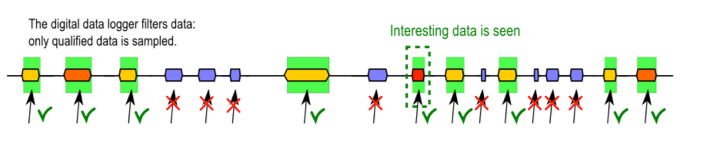

另一方面,所有逻辑分析仪都可以在并行值上触发。他们还能够建立复杂的条件序列,以最终触发数据捕获。许多数字系统总线大多数时候都是安静的。基本逻辑分析仪即使已满载内存,也有可能浪费采样资源,即使什么也没有发生。为了充分利用逻辑分析仪的内存,可以并用多种策略。因此,某些逻辑分析仪仅存储数据转换,从而潜在地压缩收集的数据。这是一种在内存上某种程度不受控制的方式,并且高度依赖于数据本身。另一种经济的存储策略是对记录的数据使用逻辑方程式,以定义逻辑分析仪应在何时存储数据或何时可以丢弃数据的条件。

数据鉴定或数据过滤是逻辑分析仪仅记录符合用户定义条件的数据的能力。在这种情况下,逻辑分析仪也称为数字数据记录仪。该策略基于已调试数字系统的先验知识。可以简单地检测信号电平(例如,输出使能)并在看到该电平时记录总线的值。或者它可能要复杂得多,例如当某些数字线路的布尔方程为真时进行过滤,或者甚至在遇到触发条件时记录预定义的数据量。

可用的总内存固然重要,但是有效的数据存储,数据鉴定和丰富的触发选项会为不同的逻辑分析仪产品带来巨大价值。查看相关数据比查看所有数据更重要。能够进行数据鉴定或数据过滤的逻辑分析仪(有时也称为数据记录器)是MSO的出色辅助工具。

4.逻辑分析仪以硬件的方式看待信号。

与大多数MSO不同,逻辑分析仪能够使用被测系统的参考采样时钟信号。这意味着与您的硬件同步查看采样信号。与“时序分析”相对,这种模式称为“状态分析”,后者是由设备本身生成采样时钟的。在状态分析模式下运行设备可能是一个挑战,因为来自被测系统的干净基准时钟信号可能并不总是可用。不过,状态分析将提供对系统嵌入式软件的深入了解,从而可以将重点放在硬件所看到的信息上,并加快调试速度。

结论

混合信号示波器非常适合各种电子系统上的大多数基本和高级测试与调试任务。因此,必须仔细考虑对额外的外部逻辑分析仪的投资。仅因为逻辑分析仪具有100个通道,所以选择逻辑分析仪可能不值得,因为存在替代的且更具成本效益的调试策略。

但是具有数百万个样本存储器,状态分析功能和数据鉴定功能的逻辑分析仪将为任何常见的MSO增值。选择具有这些功能的逻辑分析仪可以像查看电路一样查看系统,并在较长的时间范围内保存数据。这种逻辑分析仪是传统MSO的理想伴侣,因为它提供了互补的分析,可以加快调试任务的速度,并使任何工程师在调试复杂的数字问题时更加高效,不仅可以为MSO增值,还可以为您的增值服务就业!

编辑:hfy

-

24M的逻辑分析仪怎么用的2024-07-17 2214

-

逻辑分析仪和示波器区别 逻辑分析仪和示波器哪个好2023-09-19 9120

-

kingst虚拟逻辑分析仪使用详解2017-11-17 4451

-

为什么要使用逻辑分析仪2017-10-13 3449

-

逻辑分析仪和示波器的比较2017-09-28 4084

-

逻辑分析仪基础简介2017-08-07 3153

-

逻辑分析仪年初扫盲2016-01-11 2299

-

浅析逻辑分析仪2015-11-05 3834

-

逻辑分析仪介绍2008-11-27 2325

全部0条评论

快来发表一下你的评论吧 !