基于PCI Express 2.0的系统互连交换机设备系统设计

描述

本文档提供了符合IDT的PCI Express 2.0基本规范的系统互连交换机设备系列的系统设计指南。本文档还描述了以下设备接口,并提供了相关的电路板设计建议。

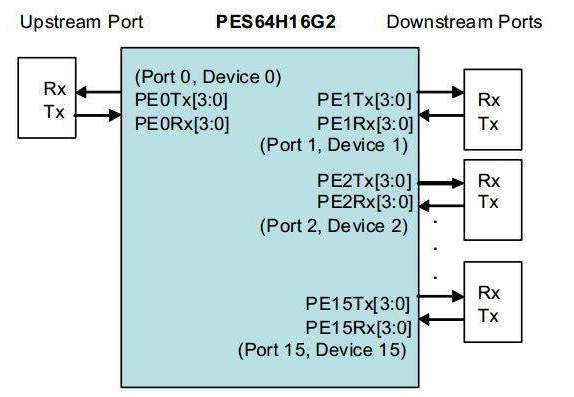

PCI Express接口:端口配置

PES64H16G2的16个端口中的每个端口在统计上分配了4个通道,端口标记为0到15。在默认配置中,SWMODE [3:0] = 0x0,端口0始终是上游端口,其余端口始终是上游端口端口始终是下游端口。在多分区配置SWMOE [3:0] = 0xC或多分区串行EEPROM初始化配置SWMOE [3:0] = 0xD中,所有端口都未连接。通过串行EEPROM或从SMBus接口,可以将任何端口配置为上游端口或下游端口。所有端口均可在最大链路宽度x4(即4条通道)上运行,并支持2.5 GT / S(第一代)和5.0 GT / S(第二代速度)。

参考时钟(REFCLK)电路

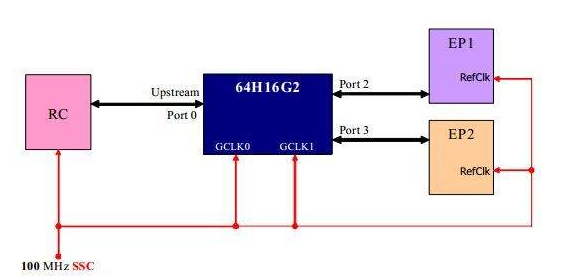

开关具有两个差分全局参考时钟输入(GCLKP [1:0] / GCLKN [1:0]),用于生成内部开关逻辑和SerDes所需的所有时钟。差分时钟输入需要信号源来驱动0V共模,并且REFCLK信号必须满足PCI Express卡机电规范中定义的电气规范。参考输入时钟上不需要交流耦合。

参考时钟输入支持扩频时钟(SSC),以降低EMI。所需的方法是调整扩频技术,使其不允许在标称频率以上进行调制。这种技术通常称为“向下扩展”。如果使用SSC,则所有时钟都必须来自一个时钟源。这包括交换机本身的时钟,连接到交换机下游端口的设备的时钟,以及连接到交换机上游端口的根联合体芯片组或其他设备(交换机或网桥)的时钟。如果不使用SSC,则树中的每个PCI Express设备都允许使用多个时钟源。

交换机和十五个下游设备的差分时钟可以从时钟缓冲器/发生器(例如ICS9DB803)获得。系统设计人员可以使用其他与Gen2兼容的时钟缓冲器/发生器。ICS9DB803器件用于IDT评估板上。

交换机为交换机的每一侧提供两种时钟操作模式:全局时钟和本地端口时钟。系统设计人员必须配置CLKMODE [2:0]引脚,具体取决于为交换机的上游侧和下游侧选择了哪种模式。有关每种模式的详细信息,请参阅《 PES64H16G2,PES48H12G2或PES32H8G2设备用户手册》。当在上游端口或下游端口上使用非公共时钟时,必须禁用扩频时钟。

重置(基本重置)方案

PERSTN引脚用于复位开关内部的所有逻辑,它是施密特触发器输入,可以从系统或上电复位电路连接到PERST#。在系统中,Tpvperi和Tperst-clk的值取决于使用该开关的机械形状因数。例如,PCIe卡机电规范,修订版2.0,规定了Tperst-clk = 100 µs和Tpvperl = 100 ms的最小值。

编辑:hfy

-

交换机网管系统2008-06-07 6951

-

什么是NP+ASIC核心交换机设计技术?2019-07-30 3723

-

路由器和交换机的区别2022-03-17 7743

-

什么是交换机间系统接口(ISSI)2008-11-27 1695

-

IDT宣布推出PCI Express Gen2 系统互连交换2010-02-11 1174

-

千兆比以太网交换机设备技术规范2022-07-11 857

-

PCI Express交换机实测系统数据传输性能2021-05-03 5336

-

基于标准的PCI Express多端口作为系统互连的多对等系统2021-04-22 7693

-

Realtek交换机设计选型参考2022-10-08 1076

-

pcie2.0交换机资料2023-03-27 858

-

GreenPacketTM PCI Express分组交换机–数字视频监控系统2023-07-26 559

-

汇聚交换机和核心交换机区别2024-01-22 8695

-

IDT 89HPES32NT24BG2:高性能PCIe Gen2系统互连交换机深度解析2026-02-09 335

-

探索Renesas 89HPES24NT6AG2:高性能PCIe Gen2系统互连交换机2026-03-02 293

-

PI7C9X2G304EV:PCI Express Gen 2 数据包交换机的深度解析2026-04-16 371

全部0条评论

快来发表一下你的评论吧 !