基于TMS320的高速系统的示例数据集

描述

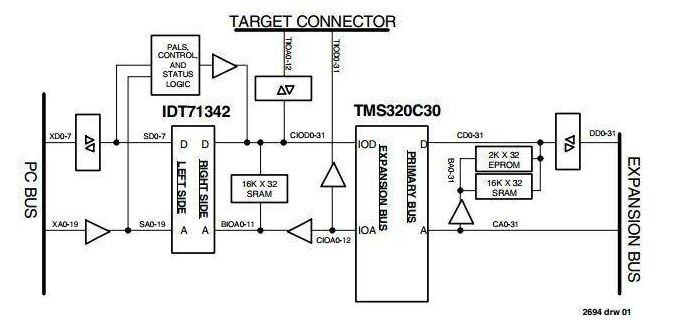

本应用笔记描述了通过IDT双端口静态RAM在IBM PC型背板和TMS320C30 DSP芯片之间的“无麻烦”接口。该接口提供了一种非常简单的方法,可以下载交叉编译的DSP代码以及用于实时调试基于TMS320的高速系统的示例数据集。

系统目标

此处介绍的设计是TMS320C30软件开发板。该评估板是系统的一部分,可帮助TMS320C30程序员从IBM PC或类似计算机下载和调试代码。为了满足TMS320C30编程器的特殊硬件需求,扩展连接器允许将内存添加到DSP芯片的主总线,而目标连接器提供芯片扩展总线的完全缓冲版本,以允许其连接到专用硬件。 。TMS320C30的大多数状态信号也都路由到扩展总线,以使它们可用于正在调试的硬件。

大多数控制软件都驻留在PC上,并在磁性介质上提供。这包括诸如汇编器,编译器以及下载和调试例程之类的工具。TMS320的主总线上的2K x 32 EPROM阵列为主机处理器提供了一组命令,以使其可以加载软件开发板的RAM,设置和清除断点,检查和预设内部状态以及加载或加载。将值存储在各个存储位置中。所有这些都由主机向TMS320发送命令来控制,TMS320会解释该命令并采取适当的措施。

与双端口SRAM接口

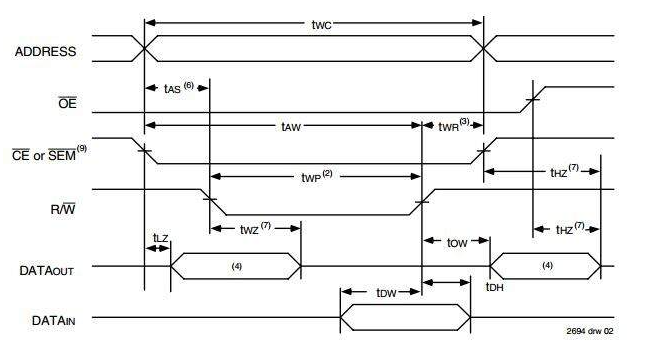

IDT71342双端口RAM使用类似于任何标准单端口字节宽静态RAM的接口。两个端口(左和右)中的每一个都使用单独的一组控制,地址和I / O引脚。地址输入不与数据I / O复用。控制接口的两侧分别包含三个引脚:读/写(R / W),输出使能(OE)和芯片使能(CE)。R / Wand OE引脚还与信号量选择引脚(SEM)结合使用,该引脚模仿芯片使能引脚的功能,但是该引脚将读写控制路由到八个片上信号灯标志。

PC总线接口

在这种设计中,PC总线控制信号几乎直接从背板路由到IDT71342的R / W和OE引脚。背板的信号功能和时序与双端口RAM的信号功能和时序是理想的匹配。但是,决定将内存阵列映射到PC的内存空间中的4K空间,同时将信号量映射到PC的I / O空间,这迫使将IOW和MEMW信号驱动之前必须进行“或”运算。 IDT71342的R / W输入。同样,将IOR和MEMR信号驱动为IDT71342的OE输入之前,它们为O红色。

TMS320C30软件开发板展示了使用IDT71342双端口RAM在TMS320 DSP芯片和IBM PC总线之间设计接口的简便性。双端口RAM用于减少组件数量,增加处理器间的通信吞吐量并简化设计。设计人员应该能够遵循此处给出的示例,以有利地使用双端口SRAM来处理任何类似的双处理器系统中的通信。

编辑:hfy

-

TMS320C6000系统时钟电路示例2024-10-28 538

-

TMS320硬件应用程序(包含扫描的文本)2024-10-26 356

-

MAX187与TMS320C3X评估模块接口2023-01-11 2303

-

瑞盟通用数模转换MS5224D兼容 TMS3202022-12-07 521

-

tms320跑linux操作系统时如何实现多核通讯2018-06-21 2105

-

tms320,c28 x指令集模拟器技术概述2018-04-11 1192

-

TMS320系列DSP在逆变焊机中的应用研究2017-10-20 1303

-

TMS320 F2833x DSP应用开发与实践2017-03-19 40142

-

tms320系列的浮点算法详解2016-06-21 983

-

基于TMS320LF2407的高速数据采集系统2016-05-06 711

-

基于TMS320的高速网络摄像机设计2011-05-30 1388

-

TMS320 DSP算法标准2010-11-25 698

-

TMS320 DSP在数字扫描探针显微镜中的应用2009-10-12 1187

全部0条评论

快来发表一下你的评论吧 !