PCB布局:USB走线的受控阻抗

描述

本应用笔记描述了通用串行总线,并提供了与USB3300的系统应用相关的PCB布局敏感区域的信息。本文档适用于在硬件设计,USB协议和USB 2.0规范方面众所周知的设计人员。

介绍

通用串行总线(USB)能够以480 Mbps的速度运行。为了在高速数据速率下可靠地运行,需要出色的信号完整性。PCB布局是保持信号完整性的关键组成部分。本文档提供有关PCB布局的建议。

USB走线的受控阻抗

USB 2.0规范要求USB DP / DM走线标称保持90欧姆的差分阻抗(有关更多详细信息,请参见USB规范Rev 2.0,第7.1.1.3段)。在这种设计中,迹线为14密耳宽,最小行距为7密耳。这些数字是在距地面参考平面13密耳的距离处得出的。在DP / DM线的正下方需要一个连续的接地平面,并且在DP / DM线的任一侧至少要延伸5倍的间隔宽度。

保持接近90欧姆的差分阻抗。对于不同的电介质厚度,铜重量或电路板堆叠,将需要重新计算走线宽度和间距。

在形状和长度方面保持DP / DM线之间的对称性。

单端阻抗并不像差分阻抗那么重要,可接受的范围是42到78ohms(等效地,共模阻抗必须在21 Ohms和39 Ohms之间)。

图1显示了具有大致相等的走线长度和对称性的DP / DM走线。

保持导体的宽度和间距以提供符合USB规范的差分和共模阻抗非常重要。使用45度转角以最小化阻抗不连续性。

隔离DP / DM迹线

DP / DM走线必须与附近的电路和信号隔离。零件到直线的距离应大于或等于迹线之间7 mil间距的距离的5倍。请勿在零件下方布线差分对。不要将DP / DM线与其他PCB走线交叉,除非走线位于DP / DM的接地层的相反侧。将DP / DM走线布线在实体平面上,而不是在电源平面上。

USB连接器上的隔离屏蔽

图2显示Mini-AB连接器外壳通过交流电耦合到设备接地。

USB3300完全支持USB On-the-Go(OTG)PHY。外壳还通过铁氧体磁珠FB2直流接地。工业惯例是仅将电缆屏蔽层的主机侧接地。这样做是为了提供电缆屏蔽,同时如果主机和设备接地之间存在电位差,则可以防止可能的接地电流流入USB电缆。如果只需要设备操作,则建议切断FB2和连接器外壳之间的走线,以便仅将外壳的AC接地。

晶体振荡器

晶体振荡器对杂散电容和其他信号的噪声敏感。它还会干扰其他信号并引起EMI噪声。负载电容器,晶体电阻和并联电阻应放置得彼此靠近。负载电容器的接地线应短接,并远离USB,VBUS电源线的返回电流。负载电容器的返回路径应为数字逻辑电源。

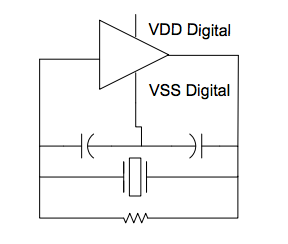

图3示出了晶体振荡器电路的示意图。

图4说明了晶体电路的建议PCB布局。所有组件都离USB线很远。

RBIAS

RBIAS电阻设置内部电流源基准。因此,RBIAS引脚是一个高阻抗节点,因此,在RBIAS走线上产生的任何噪声都会直接影响内部电流基准,并对眼图质量产生负面影响。RBIAS电阻应放置在靠近RBIAS引脚的位置,接地回路应短接RBIAS,其接地方式应与旁路电容器相同。电阻的走线应非常短,并尽可能与附近的走线隔离。

编辑:hfy

-

受控阻抗布线技术确保信号完整性2025-04-25 1487

-

PCB走线的设计细节详解2023-04-13 2578

-

PCB设计走线的阻抗控制简介2023-04-12 1569

-

PCB布局之蛇形走线2022-12-27 1539

-

浅谈PCB布局中的DDR4阻抗变化2020-12-31 9407

-

PCB的受控阻抗走线设计和微带线与带状线的实现说明2020-09-29 1548

-

什么是PCB线路板走线阻抗2020-09-21 14343

-

PCB布局和走线的调整2019-10-17 3558

-

如何控制PCB走线的阻抗2019-10-04 11924

-

印刷电路板布局中 仔细观察PCB走线2019-08-08 3581

-

pcb布局,走线方面2016-10-15 5807

-

开关电源的PCB设计(布局、排版、走线)规范2016-07-26 1029

-

PCB 布局、走线资料2014-08-02 3188

-

PCB Layout零件布局走线原则2012-06-25 6119

全部0条评论

快来发表一下你的评论吧 !