HDI设计在高速中的应用以及仿真方法

描述

HDI设计在高速中的应用以及仿真方法

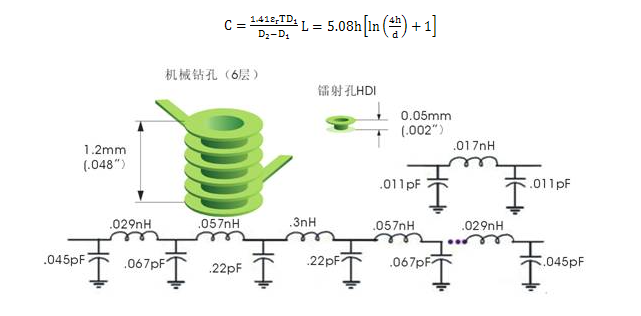

高速串行总线技术的发展,信号传输速率继续提升,过孔寄生参数带来的影响也越来越被重视。高速仿真工程师关注过孔优化,通过各种手段来减小过孔寄生参数带来的影响。HDI由于采用盘中孔的设计要求,可以减少表层器件的寄生参数。同时,微孔的电感和电容大约只是一个标准过孔的十分之一左右。图九是能在很多资料上找到的过孔电感和电容,这是根据以下两个计算公式得到的。

图九 镭射孔和机械孔的寄生参数但是图七还是存在很多问题,寄生电容是对地的电容,机械孔不会6层都连接地平面,计算会远远比公式来得复杂;现在的过孔生产的时候,基本都采用无盘工艺,即去除非连接层的过孔焊盘,这可以有效减小过孔的寄生电容。这种情况下,只用 来简单考虑过孔特征阻抗的影响是远远不够的。

来简单考虑过孔特征阻抗的影响是远远不够的。

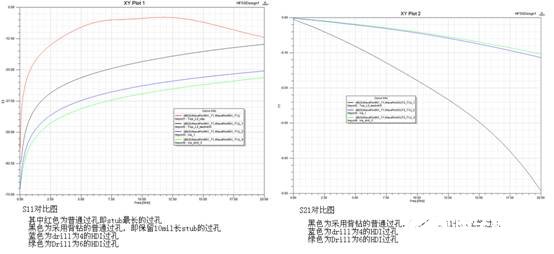

图十是从S参数分析微孔和普通机械孔的插入损耗与回波损耗

图十 S参数分析微孔和普通机械孔的插入损耗

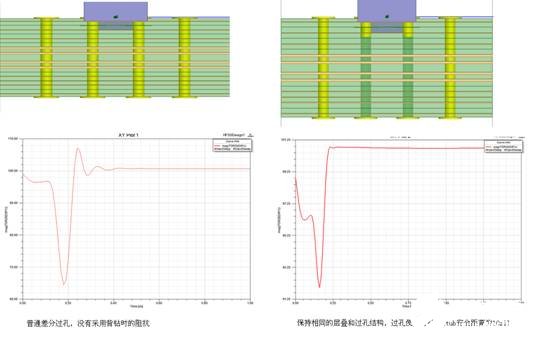

然后通过TDR的公式可以看到过孔的阻抗和回损曲线是密切相关的,S11在全频段的仿真精度,也决定了通过软件仿真看TDR曲线来研究阻抗的准确性,如图十一所示:

TDRZ(t) = Zref*(1+IFFT(S11*input)) / (1-IFFT(S11*input))

能看到背钻对过孔阻抗还是影响很大的

差分HDI微孔的阻抗,和100欧姆比较接近

图十一 差分过孔的优化策略以及TDR仿真结果

微孔的阻抗可以比较容易优化到差分线的100欧姆阻抗值,这样就减少了过孔引起的阻抗不连续带来的高速问题。

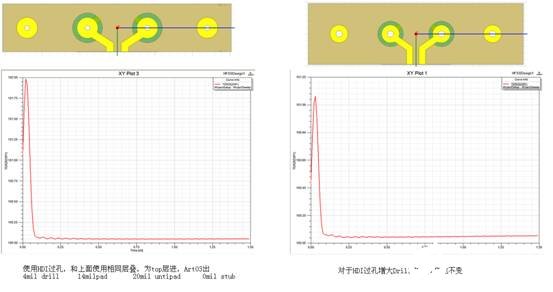

从以上分析可以看出,微孔的高速性能远远优于普通机械孔,并且没有Stub的问题,机械孔就算是采用背钻工艺,也不可避免的要出现一定长度的Stub。而这个Stub,往往是影响高速电路性能的致命杀手。

有如果关心微孔的过电流能力,需要的时候可采用微孔填铜来提高载流能力。

结 论

Cadence的SPB16.X平台提供了出色的小型化设计能力,在HDI多阶过孔设计,任意阶过孔设计,埋入式器件设计以及基于PDN的埋容仿真分析等领域都提供了出色的支持。全面基于HDI进行优化更新的约束管理器,帮助工程师实现在小型化设计领域的约束驱动布局布线,提升设计效率和保证设计成功率。

基于Cadence强大的平台和自身HDI设计上丰富的经验,同时结合自有板厂以及合作伙伴在国内领先的HDI加工能力,一博科技可以提供全方位的小型化设计、仿真、生产、贴片、组装等一站式服务,全面实现客户在小型化领域的各类需求,更多资讯请参见:www.edadoc.com。

一博科技和Cadence合作,强强联手,推出《Cadence印刷电路板设计 – Allegro PCB Editor设计指南》一书,书中也专题介绍了小型化设计的技术,欢迎大家参考交流。

参考文献

[1] 《Cadence印刷电路板设计 – Allegro PCB Editor设计指南》

[2] 《High-Speed Digital Design – A Handbook of Black Magic》

致 谢

本文引用了《Cadence印刷电路板设计 – Allegro PCB Editor设计指南》王辉负责的小型化章节,同时仿真部分和Cadence 钟章明做了很多交流,在此表示感谢!

编辑:hfy

-

xmzykj

2021-04-29

0 回复 举报介绍的很详细 收起回复

xmzykj

2021-04-29

0 回复 举报介绍的很详细 收起回复

-

稳压二极管的实际应用以及仿真验证2022-09-02 4319

-

什么是HDI?PCB设计基础与HDI PCB制造工艺2024-07-22 12960

-

求大神指教CMOS在开关电源中的应用以及作用?2014-07-15 5451

-

高速HDI电路板的设计挑战2019-02-26 3803

-

PCB中什么是HDI2019-11-20 4487

-

什么是HDI PCB2020-06-19 3964

-

C语言在实际中的应用以及补充 精选资料推荐2021-07-22 886

-

OpenHarmony HDF HDI基础能力分析与使用2021-09-02 3265

-

元器件在电路中的作用以及使用方法2022-01-21 1102

-

HDI的CAM制作方法大全2010-03-15 1489

-

开关电源中PLC在应用以及使用时应注意的问题2016-05-18 550

-

基于高速PCB传输线建模的仿真是怎样的2019-10-22 4604

-

HDI板的应用范围介绍2020-10-15 6610

-

HDI板在5G技术中的应用2024-10-11 1365

-

HDI技术在5G通信设备中的信号完整性优化方法2024-12-04 1445

全部0条评论

快来发表一下你的评论吧 !