FPGA电源保养和供电的电源解决方案

描述

现代FPGA是有史以来最复杂的集成电路。他们采用最先进的晶体管技术和尖端的建筑结构,以实现难以置信的灵活性和最高性能。随着时间的推移,随着技术的进步,这种复杂性已决定了在使用FPGA的系统的设计和实现中的某些折衷办法。在电源方面,这比在任何地方都更加明显。对于每一代新的FPGA,电源都必须更加准确,更加敏捷,更加可控,更小,更高效并且对故障有更多的了解。

在本文中,我们专门研究了Altera Arria 10 FPGA的一些约束规范,以及它们对电源设计的意义。然后,我们讨论最佳的电源解决方案,并制定计划以成功满足所有规格,并使用ADI公司的整套电源系统管理(PSM)IC使FPGA以最佳的效率,速度和功率水平运行包括LTC3887,LTC2977和LTM4677。

FPGA功耗要求(解释数据表)

工程师应该将大部分时间花在编程上,而又不想花时间和精力在设计合适的电源上。确实,供电的最佳方法是使用坚固,灵活,经过验证的设计,该设计可以满足要求并随着项目的发展而扩展。这使工程师腾出了重要工作来设计具有背景比特币矿机或类似设备的每秒兆兆比特的加密并行无线光学轨道互联网平台。在这里,我们仔细研究一些重要的电源规格及其含义。

电压精度

内核电源电压是平衡FPGA功率和性能的最重要的关键之一。规格文件给出了可接受的电压范围,但总范围并不完整。与所有事物一样,需要进行权衡和优化。

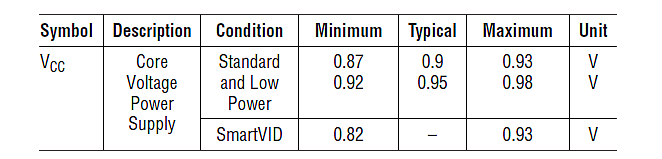

表1是流行的Altera Arria 10 FPGA 1的核心电压规范示例。尽管这些数字特定于Arria 10,但它们代表了其他FPGA内核电压要求。该范围相当于额定电压的±3.3%容差。在此电压范围内,FPGA可以正常工作,但完整的画面更为复杂。

表1 Altera Arria 10核心电压规格

注意标有“ SmartVID”的行,范围为0.82V至0.93V。这代表了广泛的电压范围,当FPGA通过SmartVID接口请求其自身的内核电压时,这是可能的(稍后会有更多介绍)。SmartVID规范表明了FPGA的基本原理:它可以在不同的电压下运行,这取决于其特定的制造公差以及所实现的特定逻辑设计。一个FPGA所需的静态电压可能与另一个FPGA不同。电源必须能够响应和适应。

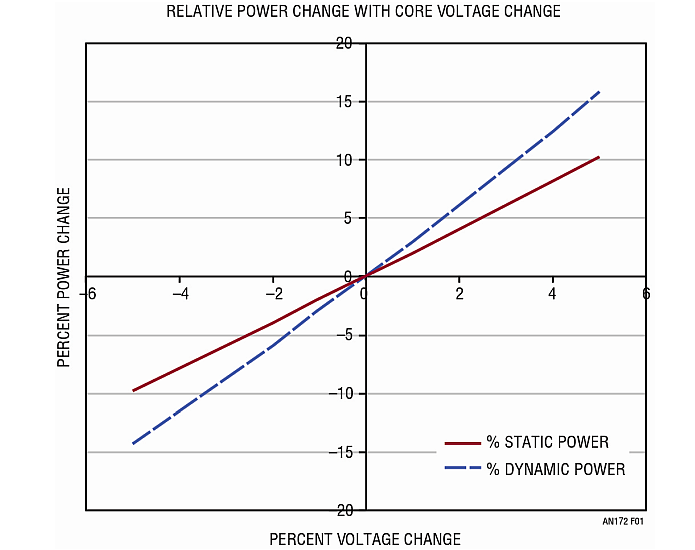

目标是产生恰到好处的性能水平,以操作已编程的功能,而不会消耗不必要的功率。从半导体物理学以及Altera,Xilinx(图1)等发布的数据中我们知道,随着内核V DD的增加,动态和静态功耗都将急剧增加,因此目标是为FPGA提供足够的电压以达到满足其时间要求,但仅此而已。过多的功耗并不能提高性能。实际上,这会使情况变得更糟,因为晶体管泄漏电流会随着温度的升高而增加,从而耗散了更多不必要的功率。由于这些原因,当务之急是针对设计和工作点优化电压。

图1 Xilinx Virtex V电源与Core V CC

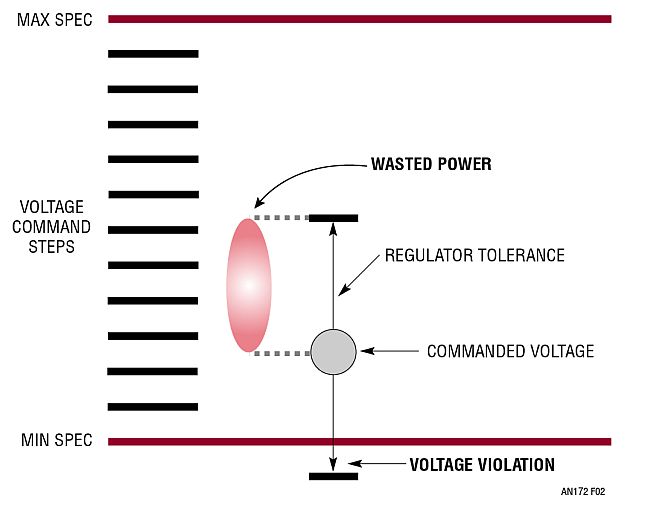

此优化过程需要非常精确的电源才能成功。调节器的不准确性必须纳入误差预算,并从可用于优化的可用电压范围中减去。如果内核电压降至要求以下,则FPGA可能会因时序错误而发生故障。如果内核电压漂移超过最大规格,则可能损坏FPGA,或者可能在逻辑中造成保持时间故障。所有这些情况都必须通过考虑电源容差范围来防止,并且只能保证保证将其保持在规格范围内的指令电压。

问题在于大多数功率调节器不够精确。稳压电压可能在指令电压附近的公差范围内,并且可能随负载条件,温度和使用期限而漂移。保证±2%容差的电源可以在4%电压范围内的任何地方进行调节。为了补偿电压可能过低2%的可能性,必须将命令电压提高2%以上,以满足时序要求。如果调节器随后漂移到高于指令电压的+ 2%,它将在该工作点所需的最低电压之上运行4%。这仍然可以满足FPGA所要求的规定电压,但会浪费很多功率(图2)。

图2电源调节器容差的权衡

解决方案是选择可以在更严格的电压容限下工作的电源稳压器。可以要求公差为±0.5%的稳压器在所需的工作频率下更接近最低要求,并且保证低于所需电压的1%。FPGA将正常工作,并且将在该工作条件下消耗可能的最小功耗。

LTC388X系列电源控制器在一个可配置的宽电压范围内,保证了稳定的输出电压容差优于±0.5%。LTC297X系列电源系统管理器保证稳压器的修整容限优于±0.25%。有了这些精度,就可以为任何FPGA优化功耗与性能之间的权衡取舍。

热管理

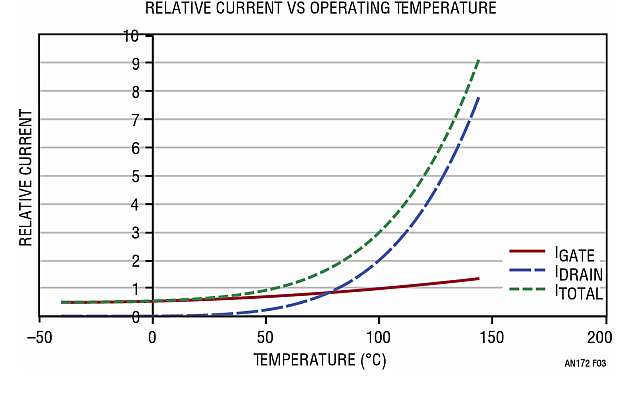

电源精度的微妙含义体现在热预算中。由于静态功耗几乎可以忽略不计,因此即使不执行任何操作,FPGA也会发热。温度升高会导致更多的静态功耗,从而进一步提高工作温度(图3)。)。向电源添加不必要的电压只会使此问题变得更糟。如前所述,不正确的电源需要在工作电压中设置一个保护带,以确保有足够的电压来完成这项工作。由容差,系统组件可变性和工作温度的变化引起的电源电压不确定性会产生明显高于最低要求的电压。当施加到FPGA时,这种额外的电压会导致散热复杂,甚至在高处理负载下也会导致散热失控。

图3 电源电流与工作温度的关系

补救措施是提供一个非常准确的电源,该电源只能产生正确的电压,而不仅仅是产生所需的电压,而这正是ADI电源系统管理设备的出色表现。

SmartVID

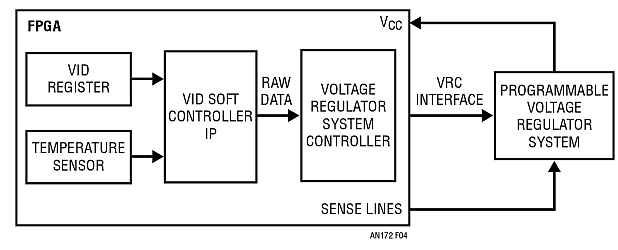

Smart VID 2 是Altera的名称,它是按FPGA本身的要求在最佳电压下运行每个FPGA的技术。FPGA内部有一个寄存器,其中包含一个特定于器件的电压(在工厂编程),可以保证FPGA在该电压下高效运行。FPGA内部的一个已编译IP可以读取该寄存器,并通过外部总线向电源发出请求以提供此精确电压(图4)。达到电压后,在运行期间它将保持静态。

图4 Altera SmartVID结构

SmartVID应用程序对电源的要求包括特定的总线协议,电压精度和速度。总线协议是FPGA用于将其所需电压传送至功率调节器的几种方法之一。在可用的方法中,PMBus是最灵活的,因为它可以处理种类繁多的电源管理IC。SmartVID IP使用两个PMBus命令:VOUT_MODE和VOUT_COMMAND,通过它们可命令兼容PMBus的功率调节器获得正确的电压。

稳压器对电压精度和速度的要求包括:自动启动电压(在PMBus激活之前),每10ms接受新的电压命令的能力,在电压调整阶段每10ms采取10mV步进的能力以及稳定时间。在10ms的步进时间内达到目标电压的30mV(〜3%)以内,最终上升到指令电压并在FPGA操作期间保持静态。

尽管Altera使用SmartVID这个名称,但业界也有其他类似的技术可以实现相同的功能。最简单的方法之一是在工厂测试每块板,然后将精确的电压编程到电源的非易失性存储器中,以优化该特定板的性能。此技术不需要任何其他干预即可使电源在正确的电压下运行。这是具有EEPROM的电源管理器或控制器的优点。

LTC388X系列电源控制器可以满足Altera SmartVID的所有要求。此外,LTM4675 / LTM4676 / LTM4677 µModule稳压器可以轻松满足要求,并以紧凑的形式提供完整的解决方案。

定时关闭

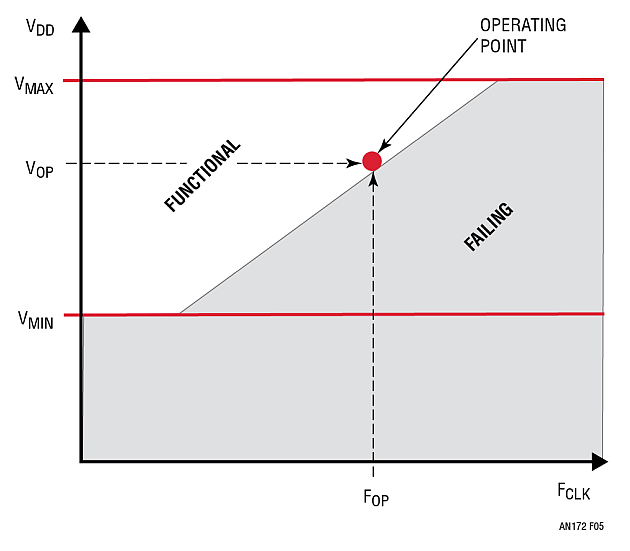

任何逻辑块的计算速度取决于其电源电压。在限制范围内,较高的电压可提供更快的性能。我们已经了解了为什么我们不能简单地在最高电压下工作,从而保证最佳速度。另一方面,如图5所示,我们必须在足够高的电压下工作以进行应用。

图5 FPGA工作频率与V DD 的权衡

图5的重要含义 当特定设计不满足其逻辑时序要求并落入“失败”区域时,该怎么办。在将设计提交给硬件之前,通常无法很好地定义功能与故障之间的界限,并且无法预先确定将通过时序的特定电压。唯一的选择是要么预先承诺一个远远高于最小值的电压,从而浪费功率以保证功能,要么设计一种灵活的电源,以便在测试时甚至在测试时适应硬件的需求。如果是SmartVID,则在开机时。适应未知需求的能力使ADI PSM器件的精度更有价值,因为FPGA设计人员可以在实际设计中以及在开发的任何阶段权衡功率以提高性能。

电源排序101

摩尔定律推动了现代FPGA中晶体管不断缩小的趋势,并迫使人们在使用这些微小的晶体管时进行权衡,这些微小的晶体管非常快,体积很小,但更易碎。包含数亿个晶体管的芯片必须分为可独立设计和管理的内核,模块和分区。这些考虑的实际结果是具有许多电源域的FPGA。最近的一些FPGA具有多达12个以上的电源,需要保持这种电源状态。除了电压,电流,纹波和噪声外,还包括启动,关闭和故障情况下的顺序。

当启动和关闭电源时,最新的FPGA规范对序列顺序提出了具体要求。Xilinx和Altera都建议使用特定的顺序和时序,以确保FPGA正确复位,保持最小的电流消耗并在电源转换期间将其I / O保持在正确的三态配置。给定每个FPGA的电源数量,排序任务的复杂性相当可观。

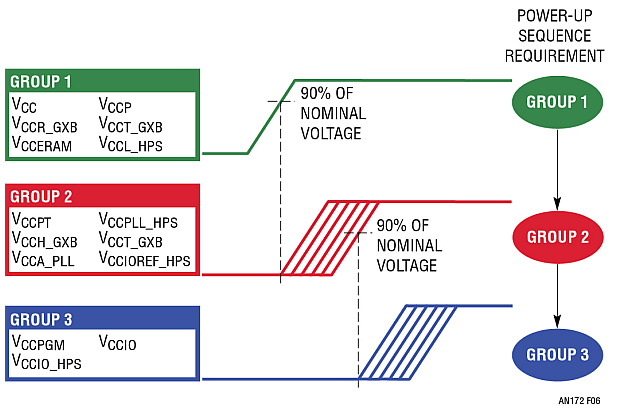

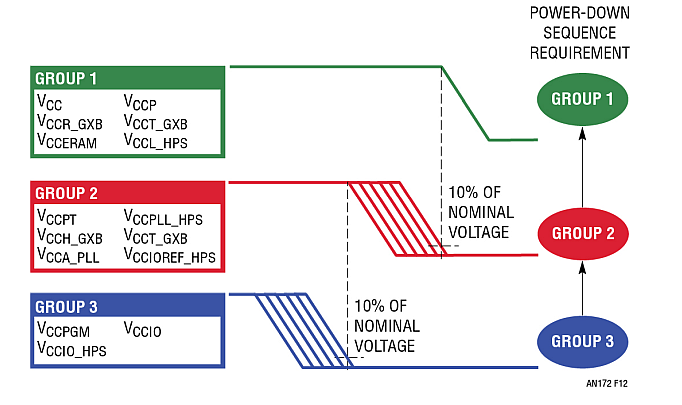

Altera Arria 10处方将电源分为三个顺序组(1、2和3),并要求它们按顺序1、2和3向上排序,并按相反的顺序向下排序:3、2和1 3。

图6 Altera Arria 10升序组顺序

同样,针对Virtex UltraScale FPGA升序的Xilinx建议是:VCCINT / VCCINT_IO,VCCBRAM,VCCAUX / VCCAUX_IO和VCCO。降序是升序顺序4的逆序。

这些只是众多可用FPGA中的两个。几乎每个现代的FPGA系统都有多个电源轨,最明显的问题之一是,它们应按什么顺序打开和关闭?即使没有明确的排序要求,也有充分的理由强制执行确定性的事件序列。以下是一些可用的设计选项。

无需排序-让电源自行上升和下降。可能出什么问题了?

硬件级联排序—每个上升的电源都必须进行硬连线以启用下一个电源。这仅在耗材增加时起作用。

基于CPLD的排序-使用可编程逻辑来创建自定义解决方案。这是灵活的,但是整个挑战都在设计师身上。

基于事件的排序-基于事件的排序类似于级联排序,但是更加灵活,因为它可以上下运行。专用的定序器IC可以进行编程,并处理许多故障情况和特殊情况。

基于时间的排序-基于时间的排序会在指定的时间触发每个事件。结合全面的故障管理,基于时间的定序器可以变得灵活,确定性和安全。

没有排序

完全不用管理就可以打开电源系统。当主电源可用或“ ON”开关被激活时,调节器开始调节。断电或“ ON”开关关闭时,调节器将停止调节。当然,这种方法存在很多问题。有些比其他的更明显。

缺乏时间确定性会在系统中产生各种影响。首先是简单地强调敏感的FPGA。这可能会立即导致灾难性故障,或者可能导致过早老化,从而慢慢降低性能。都不是好事。它也可能导致不可预知的上电复位行为或上电时不确定的逻辑状态,这使系统稳定性令人怀疑且难以调试。故障检测和响应,能量管理和调试支持的问题在此方案中完全没有解决。通常,避免电源时序控制会引发灾难。

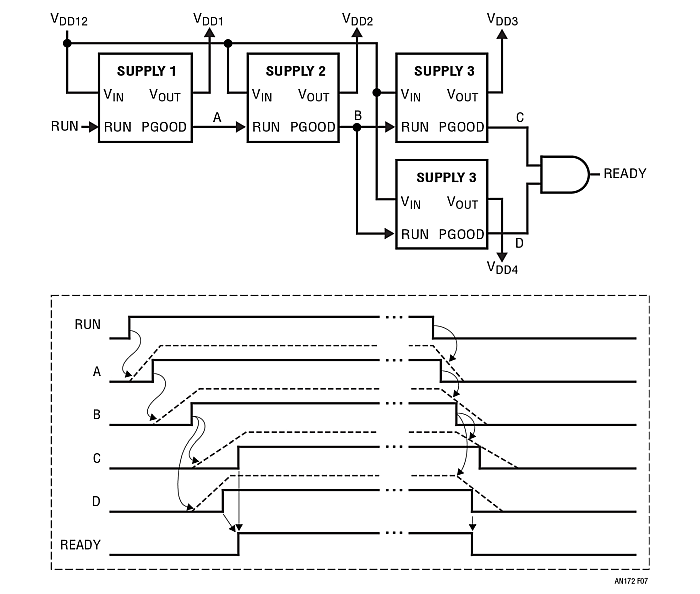

级联测序

图7所示为经典的PGOOD-to-RUN硬接线级联,它是一种更有条理的排序方法。。这就像多米诺骨牌掉落:每个人都点击序列中的下一个,这保证了进度。该技术具有简单性的优点。不幸的是,它也有缺点。尽管它通常可以正常地用于对电源系统进行排序,但它不能反向(或以任何其他顺序)进行向下排序。只能有一个序列顺序。另外,该方案不能在不确定的操作条件下适当地处理故障或管理能量。做任何决定还不够聪明。如果序列的一个阶段失败,接下来会发生什么?如果一个工作电源用尽,会发生什么?答案是不确定的,调试这些问题并不容易。

图7 PGOOD至RUN级联测序

FPGA或CPLD排序

许多设计人员选择在板上使用辅助CPLD或FPGA来对电源进行排序。在由数字设计师和为数字设计师设计的系统中,它具有一定的吸引力。设计数字控制模块是很自然的事情,可以将其编程到FPGA中以控制另一个FPGA的电源。这里的决定可能具有欺骗性,因为电源系统并不像从数字控制的角度看那样简单。

如果设计人员希望从头到尾解决电源排序,控制和管理问题,那么他必须首先彻底了解其复杂性。我们已经讨论了许多这样的内容,还有更多内容,例如检测和响应微秒级时可能发生的过压和欠压情况,检测危险电流和温度,记录遥测和状态以及提供启动信息。和调试服务,使硬件人员的工作更轻松。所有这些考虑因素除了数字算法外,还需要专用的模拟硬件。

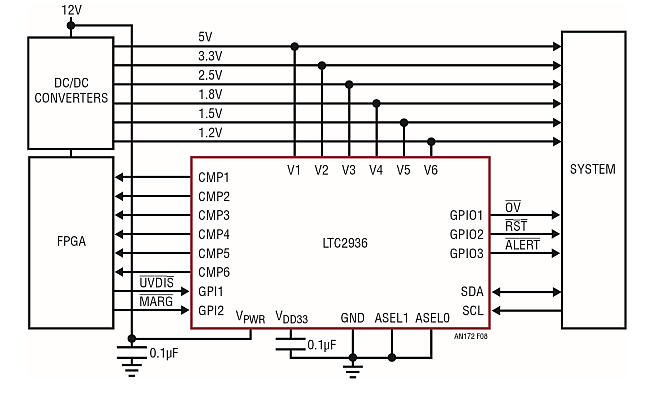

对于希望走这条路的勇敢的设计师,ADI公司提供了几种模拟前端IC来帮助完成这项任务。在数字位和模拟电源之间的接口,LTC2936提供了六个坚固的,高精度可编程阈值模拟比较器,以检测快速事件并将数字状态发送至逻辑。它还具有三个可编程的GPIO引脚,用于其他功能。该可编程IC具有一个EEPROM,用于在启动时提供几乎即时的功能,并能够存储故障遥测信息以通过其I 2 C / SMBus接口进行调试。图8显示了使用LTC2936的便捷方法。

图8 LTC2936可编程电压监控器

除了快速比较器功能外,还必须有一个模数转换器(ADC)来收集遥测数据。LTC2418是一个经过验证的选择,它可以通过其快速建立的24位delta-sigma ADC和4线SPI接口监视多达16个通道的模拟信号。板控制器可以轻松地传输测量结果并监视系统中的许多兴趣点。

通常,使用FPGA或CPLD控制电源排序有很多选择。这种方法可行,但必须有人拥有数字和模拟设计,包括所有不可避免的设计错误,出现难以想象的极端情况和故障的机会以及令人不快的支持问题。当然,有更简单的方法来构建电源系统。

简单的音序器/监督器

解决强大的排序和错误处理难题是简单的排序器/管理程序的领域。这些功能对电源轨进行排序,并确保它们在运行(监控)期间保持在其指定的限制内,这一重要工作很重要。的LTC2928是一种易于使用的引脚带配置序器配置的序列的定时(下是向上的反向),和可配置的监督员电压阈值。它具有满足要求的潜力,但没有多余的装饰,并且不提供数字可编程性或遥测功能。

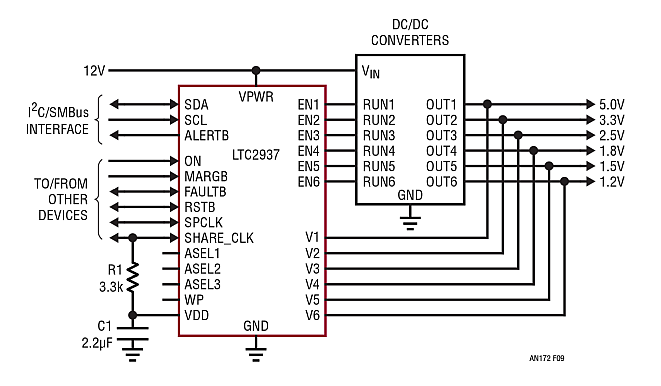

图9 LTC2937电源管理器和排序器

LTC2937是具有EEROM的可编程定序器和监控器的类别。它具有完整的数字可编程性,基于时间和基于事件的排序功能,并且可以对任何数量的电源进行排序和监督,处理故障并将故障状态记录到EEPROM黑盒中。对于不需要电压管理和遥测的情况,这是一个有价值的解决方案。

电力系统管理

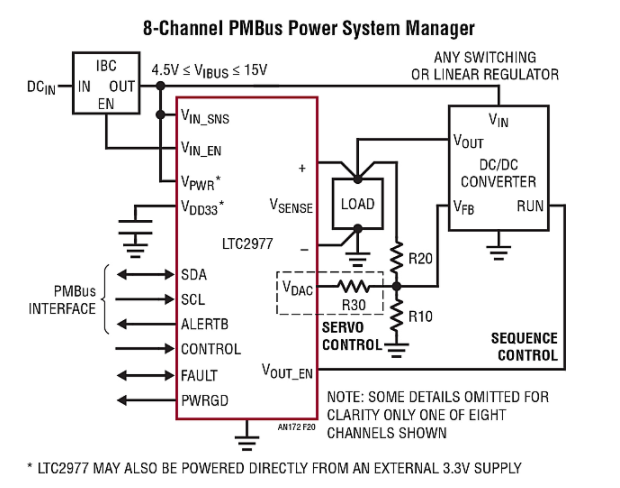

为了充分利用完整的电源系统管理(PSM)的所有优势,请使用ADI公司的PSM IC之一。这些功能可以自动对任意数量的电源轨进行升序和降序排序,将电压精确控制在0.5%以上(在某些情况下为0.25%),可以测量和报告电压,电流,温度和状态遥测,从而协同处理复杂的信号。故障场景,并将详细的故障信息记录到EEPROM。

排序是通过定时握手系统完成的,所有IC均同意“零时间”和时基,所有序列事件均发生在预编程的时间(基于时间的排序)。这允许任意数量的导轨自动进行升序和降序。

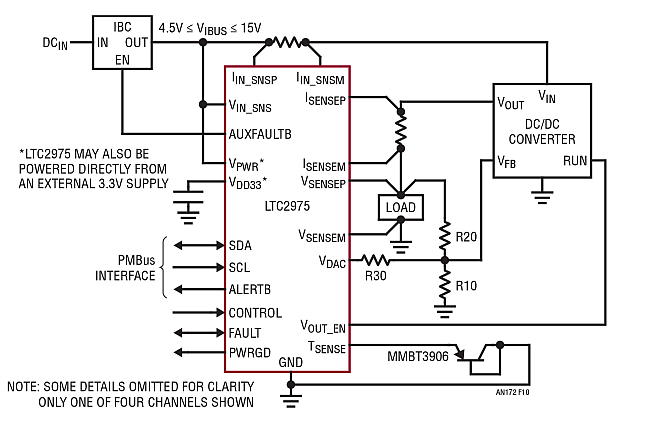

PSM IC系列包括“控制器”,这些控制器具有自己的开关驱动器和模拟环路控制,以在各个方面处理开关电源。或者,电源“管理器”包含环绕外部电源的伺服环路,从而将电源管理的所有功能(包括定序,监控和监视)添加到从开关电源稳压器到LDO的任何电源轨上。电源管理器的一个示例是LTC2975,如图10所示。

图10 LTC2975 4通道电源系统管理器

µModules

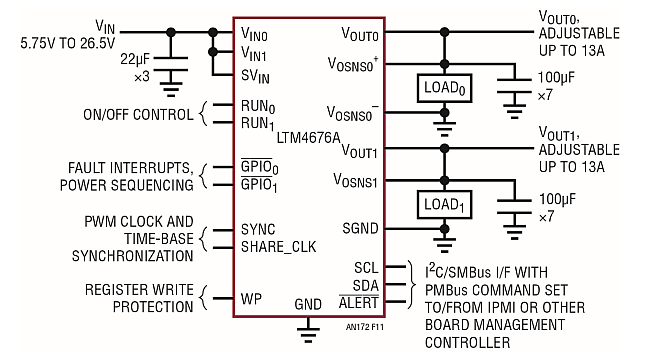

PSM µModules是最紧密集成的解决方案,在BGA或LGA占地面积中每平方厘米提供最多的功能。这些是完整的电源系统,位于一个封装中,包括控制器IC,电感器,开关和电容器。某些µModule稳压器(例如LTM4650)不包含数字功能,因此它们可以受益于LTC2975的额外排序和管理。某些µModule,例如LTM4676A,具有其自己的PSM功能,并且可以轻松地与系统中的其他PSM IC集成。

图11 LTM4676A PSM µmodule双路13A稳压器

共享测序

PSM微模块,管理器IC和控制器IC都通过称为SHARE_CLK的简单单线总线共享时序信息,从而在升序和降序方面共同协作。所有PSM IC都通过这条单线共享有关何时应该开始排序(时间为零),何时发生时钟的每个“滴答”以及有关影响排序的其他状态信息的信息。只需将系统中的所有SHARE_CLK引脚连接在一起就足以实现这种协调。每个IC都有自己的时序控制程序,可以使用共享的时基来准确,可靠地计时事件,例如在发生故障时启用和禁用,斜坡上升和超时。

在最基本的水平上,SHARE_CLK引脚是一个漏极开路的100kHz时钟引脚。漏极开路特性意味着IC可以主动下拉或放开并允许总线浮动。当总线上的所有设备松开时,上拉电阻会将电压拉至3.3V。这样一台设备就可以通过拉低直到准备就绪来停止时钟,这意味着所有设备都必须在时钟启动前达成一致:一种有效的机制,用于传达零时间,并通过停止时钟来指示排序状态。

共享故障处理

FAULT总线与SHARE_CLK引脚相似。系统中的每个电源系统管理IC都连接到共享的FAULT导线,可以使用其漏极开路输出将其拉低,或者在另一个设备拉低时作出响应。这为整个PSM设备系列提供了一种简单,快速的方法来进行通信并响应故障。该行为是完全可配置的,并且在排序过程中或在稳定状态下出现问题时,可以进行协调响应。该系统可以配置为在记录有关系统状态和发生故障的原因的黑匣子信息时,根据指定的时序来断开电源并尝试重新排序。该EEPROM黑盒信息可用于以后通过I2C总线进行处理。

降序排序和管理存储的能量

降低电源供应顺序时,还有一个额外的考虑因素:能源管理。越来越重要的是,在电源时序下降时,为电源提供确定的时序非常重要,这需要仔细考虑系统中存储的能量在哪里消散。高功率电源可能具有数十个大型电解电容器作为大容量电荷存储元件,并且这些电容器将被充电至电源电压,从而拥有足够的能量,以在不幸的条件下炸毁保护不当的设备。为了避免这种情况,FPGA制造商指定了保护器件的降序。对于Altera Arria 10,此序列如图12所示。5

图12 Altera Arria 10降序分组顺序

在此降序中隐含的要求是,电容器中所有存储的能量都必须流到某个地方并安全地消散。有几种方法可以做到这一点。最简单的是在电容器两端固定一个电阻。该电阻在电源接通时总是耗散功率,但是可以将其电阻做得足够大,以使相对损耗最小,并且RC放电时间常数可以接受地短。使电源充分放电所需的时间是RC时间常数的倍数(通常为5倍),应进行优化以使电阻器中散发的静态功率可以接受(例如,小于1/4 W)。对于1mF的电容和1.0V的电源,R =4Ω的电阻值将具有t = 4ms的时间常数,并且将在大约13ms的时间内将电源放电至50mV以下。

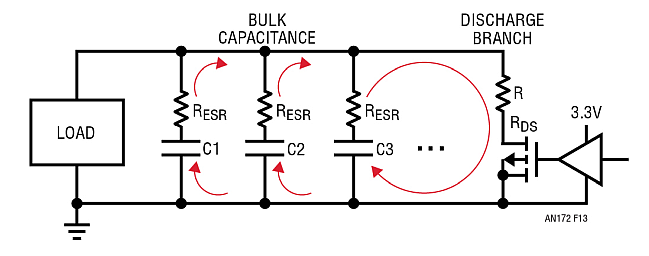

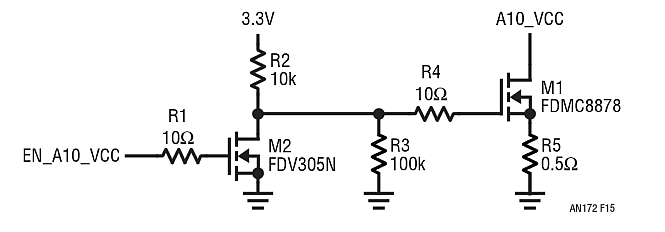

一个更复杂但非常安全的选择是仅在需要对电源放电时才在电容器上切换电阻。这种方法可以在需要时将电荷从大容量电容器中抽出,并安全地将其散逸到开关FET的电阻和辅助串联电阻中,但是避免了固定电阻器持续消耗功率的情况。该电路如图13所示。

图13 用FET释放电源电容

这种方法有几个考虑因素:控制,放电时间和功耗。必须有一个可用的信号来命令放电开关在适当的时间闭合。开关FET是NMOS,因此控制信号必须上升 到FET的V TH以上,足以驱动它达到饱和。对于普通的FET,此栅极驱动电压可能高达3V至5V。

典型的电解电容器将具有数百毫欧的等效串联电阻(ESR),当电容器放电时会消耗一些能量,但是这些电容器有很多并联,因此总并联电容可能总计为10毫法拉,等效电阻将为几十毫欧或更小。一个安全的假设是,电容器的ESR将耗散一小部分存储的能量。

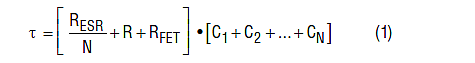

为了在合理的时间内对电容放电,放电RC时间常数必须小于所需放电时间的1/5(以使电压降至几毫伏以下)。这是一个简单的计算(公式1),使用所有电容器的总和以及FET和串联R的总和以及R ESR 电阻的并联组合,其中N是并联电容器的数量。

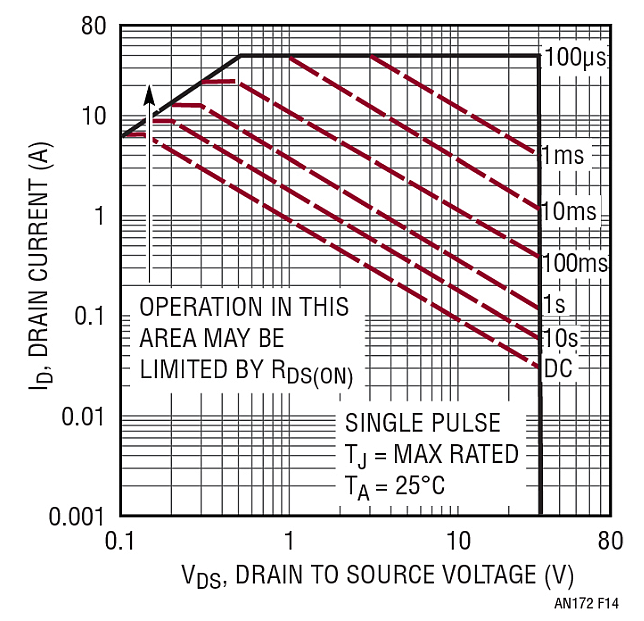

对于具有50mF电容器组且RDS + R =500mΩ之和的大型系统,电压将在约125ms内降至50mV以下。在此期间的峰值电流(和功率)为1V /500mΩ= 2A或2W。由于大部分存储的能量都是在前两个时间常数中燃烧的,因此我们可以通过查看FET的安全工作区域图(例如图14中的示例)来确定是否需要串联电阻。6 在这种情况下,我们的FET将安全地承受超过10s的2W脉冲,因此没有损坏它的危险。但是,该FET的RDS小于20mΩ,因此串联R必须为480mΩ。我们必须确定串联电阻的大小,以处理热量,因为它会耗散大部分功率。通常,脉冲持续时间将比电阻的热时间常数短得多。电阻数据手册提供了更多信息。

图14 NMOS FET安全工作区

最强大的放电电路可以在各种条件下安全地耗散能量。图15 中的电路显示了一种经过实践检验的方法。它使用安森美半导体FDMC8878放电FET和一个物理尺寸较大的SMD 1210尺寸的0.5Ω电阻器。

图15 放电FET电路

通过电源系统管理应对挑战

如我们所见,ADI公司的PSM是管理FPGA电源系统中所有需求的最佳解决方案。好处包括:

一流的电压精度(优于±0.5%)。

具有EEPROM存储器的完全自治的功能。

集成的完全可编程电源时序控制,整个系统的独立上下定时。

集成的,健壮的,系统范围的故障管理。

全面的遥测:电压,电流,温度和状态。

协调的IC系列可满足电源系统的所有领域。

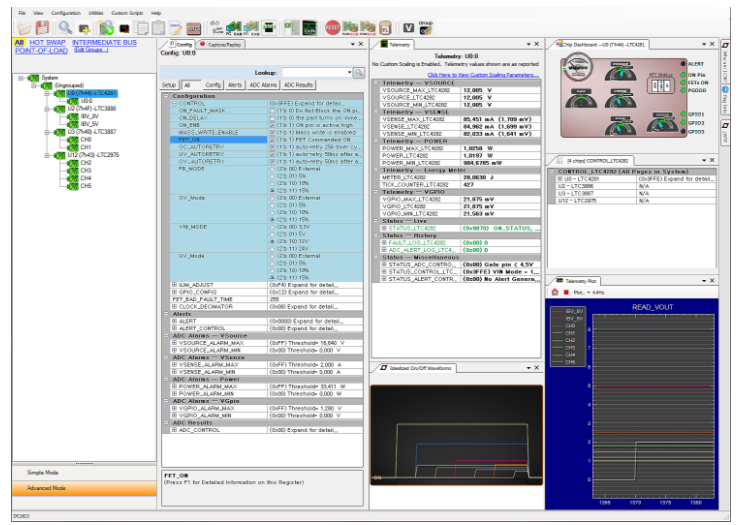

适用于所有产品阶段的功能强大的PC软件(LTpowerPlay):原型设计,设计,编程,启动,测试,调试等。

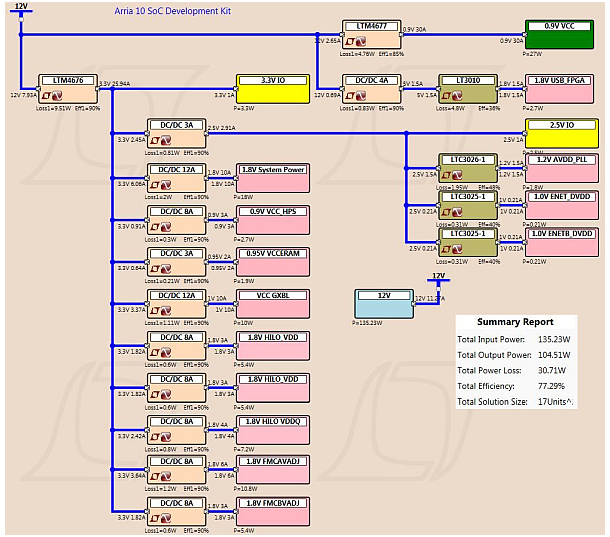

Altera Arria 10 SoC开发套件展示了适用于Altera Arria 10 SoC IC的Analog Devices电源系统管理解决方案(图16)。

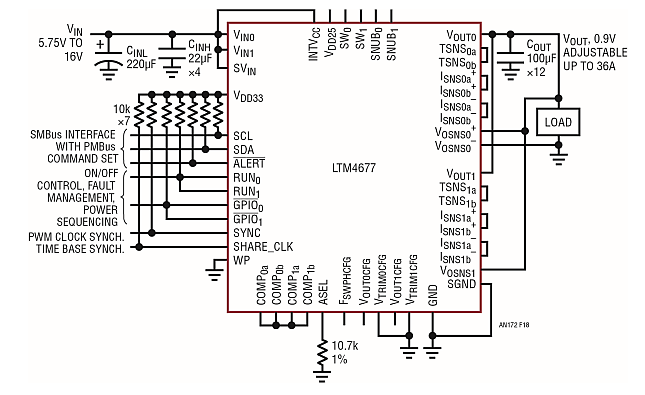

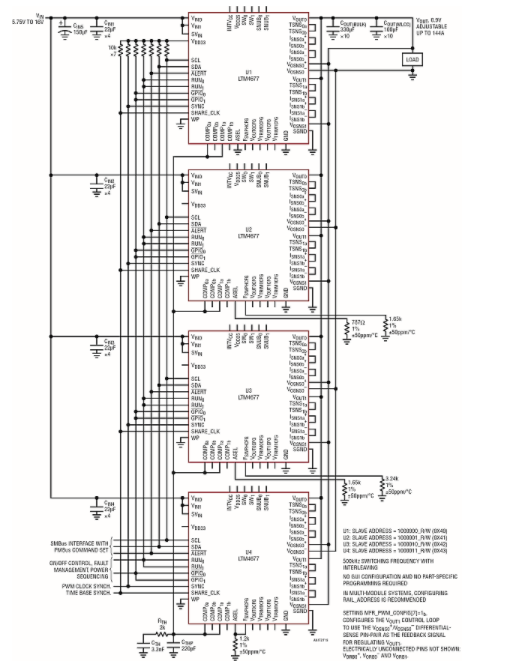

在该设计中(图17),核心电源工作在0.95V和30A的电压下。在这些相对宽松的电源要求下,单个LTM4677模块轻松提供了必要的电流(高达36A),如图18所示。对于需要更多电流的要求更高的应用,最多可以并行运行四个LTM4677模块以提供高达144A的电流,如图19所示。

图16 Altera Arria 10 SoC开发套件

图17 Arria 10 SoC开发套件的电源分配

图18提供高达36A电流的单个LTM4677

该解决方案提供了最佳的电路板空间利用率,因为集成的µModule几乎不需要外部组件,而PMBus接口使它们无需硬件修改即可配置。微型模块提供了最低的复杂度解决方案,因为其中包括许多复杂的模拟考虑因素,例如电源开关,电感器,电流和电压感测元件,环路稳定性和散热。

由于LTM4677模块包括PSM,因此它保证了核心电源将始终在直流电压目标的±0.5%范围内工作。它还允许通过PMBus接口进行电压调整,既可以通过FPGA内部的SmartVID IP进行调整,也可以通过LTpowerPlay图形用户界面进行调整,以提供用户对电源的完全控制权。

为了管理不包含其自身PSM功能的电源稳压器,我们仅包括LTC2977,它是8通道PMBus兼容的电源系统管理器。每个通道“环绕”电源以将电压伺服到编程目标的0.25%以内(图20)。它与LTM4677 µModule无缝协作以实现排序和故障响应,从而使整个电源系统具有连贯性且易于编程。

图19 四颗LTM4677在0.9V电压下提供高达144A的电流

图20 LTC2977管理任何电源电压

系统电源排序由LTM4677内核电源,LTM4676A + 3.3V电源和管理板上所有其他电源稳压器的LTC2977的合作伙伴关系提供。这些IC具有通用的PMBus时序命令(存储在EEPROM中),可轻松以任何顺序和时序配置启动和关闭时序。这些保证了为“ group1”,“ group2”和“ group3”电源指定的事件的适当的自主顺序(图6)。

除了电压精度和排序控制之外,该板上的LTM4677,LTM4676A和LTC2977还提供了完整的故障处理。如果一个或多个电源轨出现过压,欠压,掉电,过流或完全故障,则可以将系统配置为快速自动响应,关闭电源以保护敏感的FPGA,然后重新启动。 -如果可能的话,开始。

系统中的大多数电源轨要求适度的电流(小于13A)和适度的电压容限。这些可以由非PSM设备(例如LTM4620)提供,并由LTC2977进行排序和管理。这在电路板面积,复杂性和成本之间提供了非常有效的平衡。

还有一些电源轨,例如PLL和收发器电源,它们要求的噪声比开关稳压器所能提供的噪声要低,而这些电源轨则需要一个线性稳压器。的LTC3025-1和LTC3026-1提供这些功能良好,除去由它们的输出的开关和负载引起的噪声。LTC2977也可以管理这些信号,以排序,调整和处理故障情况。

LTpowerPlay

全面的LTpowerPlay图形用户界面支持整个PSM设备系列(图21)。由于PSM的许多功能都是通过IC的EEPROM中丰富的配置寄存器集访问的,因此一种工具可以将总线上的PSM IC的整个集合整合到一个易于使用的视图中。LTpowerPlay工具提供了丰富的功能集,可加快设计和开发的各个阶段。它可以离线运行,以在对IC进行编程之前显示它们的视图,或者可以通过I 2 C总线与包含一个由许多PSM设备控制的一个到数百个电源轨的完整系统进行实时通信。

LTpowerPlay通过提供有关寄存器和功能的详细信息来简化和简化复杂的配置。它以图形方式表示系统中可用的所有配置,状态和遥测信息,从而在系统运行时使其清晰易懂。它简化了完整寄存器集的编程和维护,提供了一种在Microsoft Windows PC上创建和保存配置的简单方法。当电源发生故障时,LTpowerPlay可以轻松查看系统中发生故障的位置以及状态,遥测和黑匣子信息指示发生的情况。它还为常见的故障情况提供了详细的调试帮助。如果有人需要帮助,LTpowerPlay也可以要求帮助,

图21 LTpowerPlay图形用户界面

ADI公司为Altera,Xilinx和NXP FPGA提供了一套全面的演示平台。这些功能齐全的电路板是电源系统管理如何为FPGA系统提供最清洁,最灵活和最强大的电源解决方案的有效示例。此外,您当地的ADI公司应用工程师可以为选择和使用完整的电源系统管理IC产品组合提供详细的帮助。阅读更多信息,下载参考资料,并在此处订购FPGA板。

FPGA之旅

既然我们了解了如何最好地为FPGA系统供电,那么我们可以抛开异想天开,看看为什么事情会这样。为了理解为什么今天的情况如此,我们需要简短的历史课。

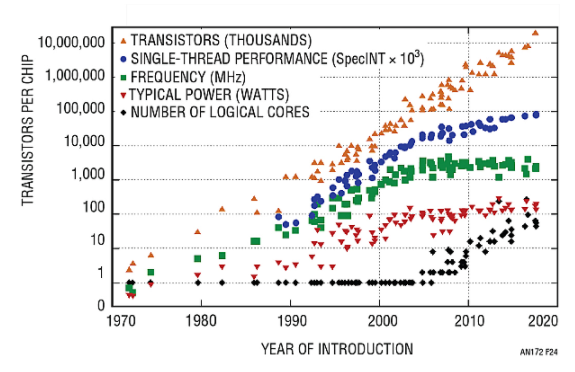

摩尔定律

1965年,戈登·摩尔(Gordon Moore)在《电子杂志》(Electronics Magazine)8中发表了他的著名文章。他指出,他观察到单个芯片上的晶体管数量每年都在增加一倍,并且他预测至少在1975年之前,这种情况应该会持续增加。修改了他的模型,但是芯片上晶体管数量的持续指数增长的基本原理已成为电子行业的一个公理。这是一个奇怪的自我实现的预言,在其他任何行业中都没有,而且在历史上也没有过。实际上,它已经成为全球工程师的主要动力,他们创造了创新,并在戈登·摩尔(Gordon Moore)首次发表他的简单观察结果时进行了难以想象的折衷。

由于这场与自己的技术竞赛,决策过程一直偏向于以成本,功耗,可用性甚至耐用性为代价将更多设备挤入更小的区域的技术。在技术竞赛中,尺寸决定一切。这种轨迹的一些含义是,先进的芯片使用更多的功率,变得更泄漏,更脆弱,更敏感,并且更难于管理和保护。

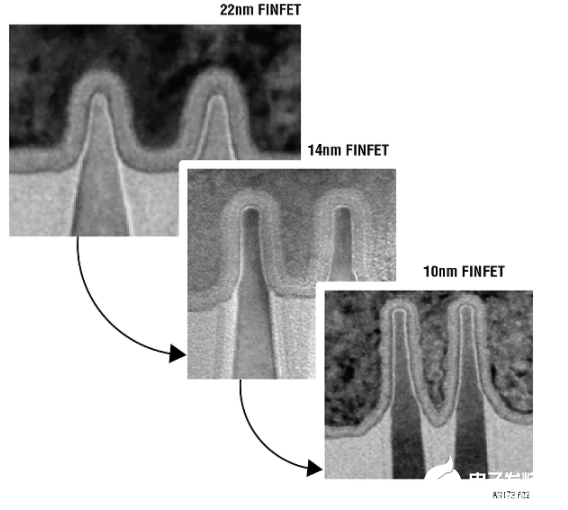

晶体管工程

随着晶体管缩小到纳米尺寸的特征,重要的副作用变得越来越占主导地位。最明显的是电压裕量。几十年前,5伏特曾是晶体管的理想电源,但这种电压会击穿较新的FET晶体管中的所有结和氧化物。随着晶体管特性的缩小,内部电场会变得更强,并且可忍受的工作电压也会缩小以防止损坏。最新的晶体管一代只能承受约1.0V的最大电源电压。此外,绝对电压容限也成比例地缩小:1.0V的2%比5V的2%的范围小得多,因此精度成为越来越迫切的问题。

图22缩小晶体管尺寸1 资料来源:英特尔公司。

随着电压的降低,晶体管电流驱动(I DSAT)也随之增加。提高的驱动强度至少可以实现两个目的。首先,它允许具有较小栅极电压的晶体管驱动很大的电流-使其强度足以切换到有用的频率。其次,它允许使用体积更小的晶体管。较小的晶体管可以更快。不幸的是,晶体管驱动强度的提高有其自身的缺点:泄漏电流。

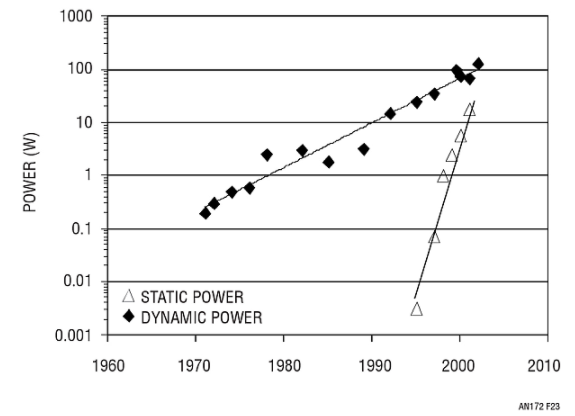

芯片上的晶体管会消耗两种功率。动态功率是在一定频率下在逻辑1和逻辑0之间切换的常见成本,而动态功率是通过对与晶体管本身以及连接器件的芯片上的导线相关的微小寄生电容器进行充电和放电而引起的。动态功率与逻辑转换的频率以及电源电压的平方成正比。

晶体管泄漏所消耗的功率不太明显。无论电路是处于活动状态还是空闲状态,无论是否计时,该电源都会在电路通电时泄漏掉。晶体管驱动强度的增加导致更多的泄漏电流,因为要传导更多电流的结和结构更难关断。较强的晶体管比较弱的晶体管更容易泄漏。随着每一代晶体管的产生,泄漏的影响越来越大。只有英雄级的晶体管工程(化学,冶金,平版印刷和物理)和准确,灵活的电源管理相结合,才能控制泄漏功率。

十年前,戈登·摩尔(Gordon Moore)观察了这些事实,并指出了两个要点。首先,如果动态功率继续以相同的速度上升,则工作芯片上的结温将接近太阳表面的结温。其次,如果不采取其他措施,泄漏功率将超过动态功率,成为主要的能耗模式,从而进一步加剧了功耗问题(图23)。为了解决这些影响,IC业界当时采用了几种新技术。其中之一是时钟管理-减慢或停止时钟以降低动态功耗-另一个是在单个芯片上使用多个处理内核以利用不断增长的晶体管数量。

图23 静态和动态功率增长

来源:“摩尔,戈登。没有指数是永远的:但是“永远”可以延迟!” 2003年国际固态电路会议。

即使使用所有这些高级架构,漏电问题仍然很麻烦。晶体管工程是一种向下弯曲曲线的有效方法,但这还不够。由于每一代较小的晶体管都需要降低电源电压,因此动态功率的问题仍然得到解决,但是随之而来的晶体管强度和漏电流的增加,以及芯片上器件数量的不断增长,对电压管理提出了要求。必须严格控制电源电压,并积极调节电源电压,以满足每个特定设备的需求。

先进的架构

直到世纪之交的体系结构发展主要集中在优化单个计算核心上,以尽可能快地执行尽可能多的计算。这涉及将时钟速率提高到电路故障速度以下的“免费”技术:其最大工作频率。它还涉及架构优化,但是这些优化主要是为了在每个时钟周期内提高性能。

在令人惊讶地意识到功率很重要之后,工程师开始将资源从原始速度重定向到更微妙的优化中。这种新趋势首先出现在计算体系结构中,这是时钟速率不断提高的平稳期,并且每一代中每个晶体管的性能提高速率都趋于平稳(图24)。这是驯服动态功率野兽的最明显方法:停止 如此快地 将电荷从V DD倾斜到V SS。

图24计算硬件指标的增长趋势

来源:M。Horowitz,F。Labonte,O。Shacham,K。Oluktun,l收集并绘制的截至2010年的原始数据。哈蒙德和巴顿。K. Rupp收集了2010-2017年的新地块和数据。

但是,单个芯片上的晶体管数量继续以戈登·摩尔(Gordon Moore)预测的(要求?)的必然速度攀升。所有这些晶体管都必须做一些事情。这就需要进行第二项重大创新:多核体系结构。大约在时钟速度停止增长的同时,单个芯片上的内核数量开始增长。多核的优势包括可通过重复使用来简化芯片设计,使用熟悉的构建模块进行更简单的软件设计,以及能够单独调节每个核以满足计算负载需求的能力。多核革命始于固定计算平台,但有人会说,这一事件是FPGA诞生的那一刻。当世界意识到最大化内核数量是最好的时候。从某种意义上说

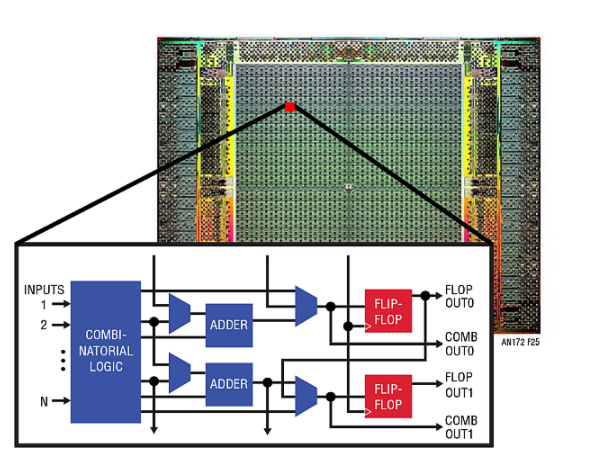

FPGA的剖析

图25 FPGA可配置结构

来源:SemiWiki.com

FPGA在最基本的层次上是通过可配置的互连网格捆绑在一起的原始可配置逻辑单元的集合。它们与编译器一起形成了高度灵活的计算结构,可以转换为几乎任何可以想象的通用数字功能,包括组合和顺序逻辑块。在顶层,该结构被其他功能所围绕,以支持和增强功能。某些模块(例如偏置电路,RAM和PLL)支持芯片内部的功能。各种可配置的GPIO单元,高速通信硬宏(LVDS,DDR,HDMI,SMBus等)以及高速收发器允许芯片内部的逻辑以各种电压,速度和协议与外界通信。其他模块,例如集成的CPU和DSP内核,

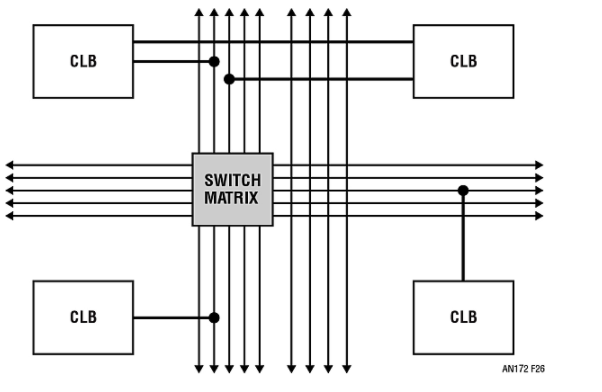

FPGA核心结构由数千个或数百万个称为“可配置逻辑块”(CLB)的基本单元组成。每个CLB是组合逻辑和顺序逻辑元素的集合,这些元素可以共同产生基本计算,并将值保存在一个或多个触发器中。组合逻辑通常采用可编程查找表(LUT)的形式,从而可以将几个输入位转换为几个任意输出位。每个LUT都按照编程执行一个基本逻辑功能,并将结果传递到可配置的互连中以进行后续处理(图26)。)。特定的CLB和LUT设计是使一个FPGA系列与另一个FPGA系列不同的秘诀之一。廉价的FPGA使用更简单的CLB,具有更少的输入,输出和互连以及更少的触发器。最高端的FPGA使用更加复杂的CLB,每个CLB都能够提供更多的输入,更多的逻辑组合和更高的速度。此优化允许每个CLB进行更多计算,并在编译设计中实现更优化的性能。自然,与较简单,互连程度较低的器件相比,在更复杂的FPGA中增加的输入和输出具有不同的动态功耗折衷。

图26 CLB之间的可配置开关矩阵

可配置逻辑功能的基本概念在核心结构本身之外延续到I / O单元,这些I / O单元也可高度配置以满足广泛的电压,驱动强度和逻辑样式(推挽,三态,开路) -排水等)。像可配置的LUT和互连矩阵一样,可编程I / O在启动时会从配置存储器中接收其配置,这对电源顺序有影响。

还有一些功能块不能或不应该使用通用CLB和GPIO来实现。这些就是所谓的“硬宏”。它们是从优化中受益的功能,或者不能简单地制造得足够快或足够小而需要专用电路。其中包括千兆位收发器,算术逻辑和DSP元件,专用控制器,存储器和专用处理器内核。与可以像软件一样编译并加载到可配置结构中的“软”块相比,这些是“硬宏”。硬宏通常具有自己的电源,特定电压和时序要求。

所有这些各种功能块均具有电源系统必须满足的各种电源需求。核心结构通常需要芯片上的最低电压和最高功率。在现代FPGA中,该结构在充分利用时,可能需要以0.85V工作的电源提供超过100A的电流。在CPU内核中可以找到相似的电压,但电压不同,电流顺序也不同。其他片上模拟功能可能由1.8V或3.3V供电,必须先通电。同时,GPIO组可能以3.3V或1.8V工作,并且必须在核心结构的上电复位完成之前才通电。这些电源序列要求中的每一个都必须由系统强制执行。

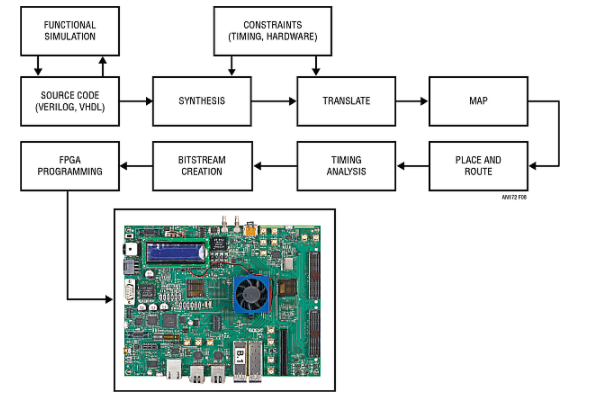

FPGA体系结构的最后一部分是工具链(图27)。为了将可配置逻辑结构的空白板块转换为高性能电路,存在一套全面的工具,可将一组Verilog或VHDL代码转换为逻辑块,分配时钟,复位和可测试性资源,优化功能以实现以下目的:速度,功耗或尺寸限制,然后将结果加载到FPGA的配置EEPROM中。没有这些工具,FPGA将永远无法发挥其全部潜力。实际上,这些工具和编程语言是如此重要,以至于它们常常使使FPGA起作用的基本电路设计蒙上阴影。

工程师将大部分时间都花在编程上,而又不想花费时间和精力来考虑提供合适的电源。但是,这些工具隐含的电源要求经常被忽略。由于数字化设计投入了大量精力,因此只有在编译后的设计融为一体时,才能知道电源需求,并且可以发现电源问题。在数字设计和软件工具中,就像在硬件设计中一样,灵活的电源架构对于成功至关重要。

历史,经济和人为因素继续推动创建FPGA的晶体管和架构的发展趋势。在FPGA的成功中,电源在每个级别和每个设计阶段都扮演着至关重要的,看不见的角色。电源的最佳选择是准确,坚固,灵活,紧凑且易于使用的电源。在所有这些品质中,ADI公司的PSM产品系列为行业树立了标准。

图27 FPGA设计流程(最后使用硬件)

附录A:护理和喂养?

可能会有一些读者对本应用笔记的标题提出疑问,尤其是那些不熟悉英语的读者。最初,似乎完全不适合提及FPGA的维护和供电。但是,针对此异议的答案非常简单:英语是一种有趣的语言。尽管没有人就“护理和喂养”一词在历史上的确切时刻达成一致,但众所周知,该术语起源于更简单的时代的农业根源,并已被广泛使用(滥用)以指代几乎所有可能会变得脆弱或气质的东西。在这种情况下,我们已经碰到头了。尽管人们是否必须“馈送” FPGA是有争议的,但肯定有人必须“照料”它!

虽然“护理和喂养”一词在现代互联网时代已广泛应用于婴儿,儿童,丈夫,老板,外籍人士,科学数据甚至数字脉冲整形滤波器等事物,但它是最早的,也许也是最奇怪的一种,可以在此经典文本中找到参考文献,这不仅对其标题感兴趣,而且对于它可以在Internet上立即获得的事实也很有趣。

参考

[1]英特尔。“英特尔Arria 10设备数据表”。6

[2]英特尔。“ AN 711:英特尔Arria 10器件的节能功能。”

[3]英特尔。“ Intel Arria 10核心结构和通用I / O手册”,图10-15和10-16。

[4] Xilinx。“ Virtex UltraScale FPGA数据表:直流和交流开关特性。”

[5]英特尔。“ AN 692:Arria 10和Stratix 10器件的电源排序注意事项。”

[6] Diodes Incorporated DMN1032UCB4数据表,图12。

[7]冯·奥赫,约阿希姆。“应用笔记:SMD电阻上的脉冲负载:处于极限。”

[8]摩尔,戈登。《电子杂志》第1卷,“将更多的组件装填到集成电路上”。》,第38卷,第8期,1965年4月19日。

[9]摩尔,戈登。“没有指数是永远的:但是'永远'可以被延迟!” 2003年国际固态电路会议。

[10] Fullers,S。和Millett,L。Ed。第55页,“计算性能的未来:是超越游戏还是更高层次?” 华盛顿特区国家科学院

Nathan Enger是Analog Devices的混合信号应用工程师。

编辑:hfy

-

FPGA的电源管理解决方案2023-11-24 620

-

简化FPGA的电源解决方案2022-11-23 801

-

如何测试FPGA的供电电源2022-09-23 3342

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案2022-09-21 1831

-

Altera Stratix V FPGA的电源解决方案2021-04-29 1052

-

为FPGA供电的最佳解决方案2019-12-11 3738

-

基于FPGA的电源解决方案太复杂?你需要学习这两种简化方法2019-06-03 2578

-

Xilinx Spartan 6 FPGA集成式电源解决方案2018-11-09 3004

-

Xilinx FPGA电源TI解决方案(1)2018-08-22 4668

-

Xilinx FPGA电源TI解决方案(2)2018-08-21 3570

-

适用于Xilinx新型FPGA的电源解决方案(3)2018-08-20 3839

-

如何选择合适的FPGA电源解决方案2018-08-13 3295

-

基于FPGA应用设计优秀电源管理解决方案2018-05-07 6967

-

简化 FPGA 电源设计解决方案2017-04-18 1251

全部0条评论

快来发表一下你的评论吧 !