串行系列:并行信号变成串行信号过程

描述

做过layout的朋友一定会有一种这样的感觉,串行通道恐怕是最容易设计的部分了。通道就一对差分线,芯片端串行部分信号pin的密度都相对低,出线也十分简单,最多在通道上有一对AC耦合电容,有些厂商甚至已经将电容集成在芯片中了。

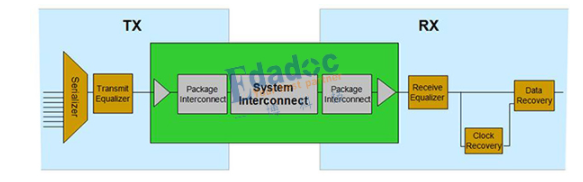

和所有的互联结构一样,SERDES无非也就是输出,输入,与互连通道。

不过,SERDES在芯片端比一般的信号要多出一些东西。首先,需要在TX端完成将并行信号变成串行信号过程,该过程通过串行器来实现,将n个速率为x的并行信号,变成一个速率为n*x的串行信号,这样在1/x的时间内,串行信号就包含了n个信息。在这个过程中,参考时钟的质量就至关重要了,我想,谁都不愿意看到在并行信号中地位相同的两个信号,变成串行信号之后一个占150ps一个却只有50ps了吧。

当然,为了保证信号的直流平衡(不要有长0长1的出现)等性能,在将数据进行串并转换之前,会将信号进行编码。在数据串化之后,会经过预加重模块,再出芯片,来到我们的信道上。

简单来说TX就是一个编码》》串化》》预加重》》输出的过程。

而通道上,就是我们熟悉走线,过孔,连接器了。这些在之后的文章中做具体说明。

这里还有一个容易被大家忽略的东西,就是器件的封装。虽然很多协议对通道的要求是并不包含芯片封装的,但是一个好的芯片封装可以为通道增加非常多的裕量,这也是为什么很多通道性能并不是很好但是芯片工作起来非常顺畅的原因之一。同样是BGA封装,flip chip的寄生电感是wire bonding的30%。当然,更好的性能自然意味着更高的成本,just you know。

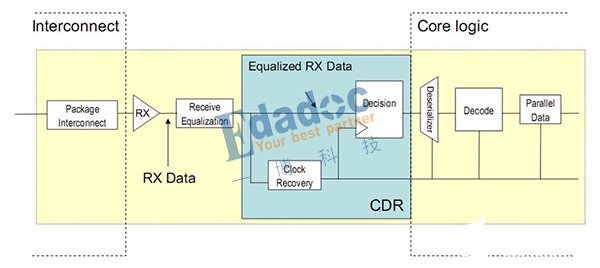

在串行通道的RX端,进行着与TX相反的过程。首先经过一个均衡器,将信号进行均衡处理。再通过CDR(clock data recovery)将串行信号解串为并行信号。

大道至简。可是在这至简的大道背后,各位工程师们可是在编码,均衡,封装等地方做了非常多的努力呢。

编辑:hfy

-

串行通讯与并行通讯介绍2025-12-11 111

-

解析常用串行总线——UART协议(上)2023-01-21 2833

-

常用串行总线(一)——UART协议(Verilog实现)2023-01-05 5004

-

串行传输和并行传输你了解多少?#信号jf_49445761 2022-08-28

-

串行口通信原理及操作2021-12-08 894

-

串行通讯与并行通信数字信号的相关资料分享2021-11-19 1214

-

什么是串行总线和并行总线?2021-06-11 20891

-

我们该“串行”还是“并行”?2021-04-04 4037

-

串行信号和并行信号有什么优缺点?2019-08-12 4825

-

并行与串行有什么区别2019-07-23 2679

-

请问2.8寸LCD屏能改成串行的吗?2019-05-21 1173

-

串行和并行的区别2017-11-24 18427

-

串行lvds数据转并行TTL数据2013-04-28 3680

全部0条评论

快来发表一下你的评论吧 !