基于CS61575和CS61574A的抖动衰减设计

描述

本应用笔记介绍了CS61575和CS61574A的抖动衰减性能。它介绍了抖动衰减器电路的描述以及衰减器设计的性能含义。

抖动衰减器电路说明

本节介绍CS61575和CS61574A的抖动衰减器电路。这为更详细地讨论两个IC的性能差异提供了基础。

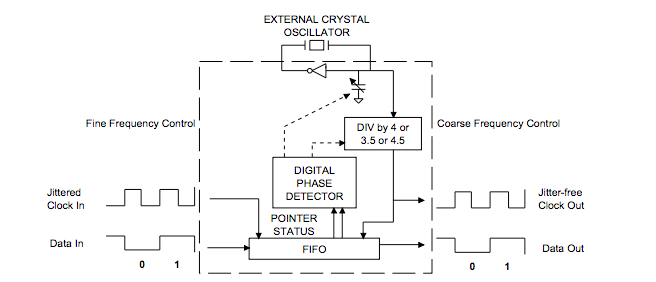

图1显示了衰减器电路。抖动衰减器可减少恢复的时钟信号中的抖动。它由一个FIFO,一个晶体振荡器,一组用于晶体的负载电容器和控制逻辑组成。恢复的时钟和数据输入到FIFO,恢复的时钟控制FIFO的写指针。晶体振荡器控制FIFO的读取指针,该指针从FIFO中读取数据。通过改变IC呈现给晶体的负载电容,可以将振荡频率精细地调整到恢复信号的平均频率。逻辑确定读写指针之间的相位关系,并决定如何调整晶体的负载电容。因此,抖动衰减器表现为一阶锁相环。信号抖动被FIFO吸收。

抖动衰减器中的FIFO设计为既不上溢也不下溢。如果抖动幅度变得非常大,则读指针和写指针可能会变得非常靠近。如果它们试图交叉,则振荡器的四分频电路会通过执行3.5分频或4.5分频来进行调整,以防止FIFO上溢或下溢。这是对输出时钟的粗略调整。在此活动期间,数据将永远不会丢失,但会发生抖动增益。

衰减器设计的性能含义

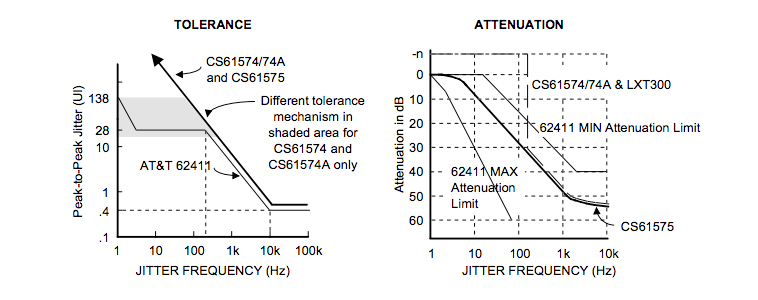

如图2所示,CS61575,CS61574A和CS61574都可以忍受AT&T 62411定义的输入抖动。(请注意,所有其他最近的标准都要求10 UI的最大容限)。但是,当输入幅度超过23 UI时,CS61575继续提供连续的抖动传递功能。如图2所示,当将超过23个UI输入到CS61574A,CS61574或类似设备(例如LXT300)时,除以3.5或4.5的机制将产生抖动增益。

AT&T 62411要求的变更

1990年12月,AT&T更改了在62411上使用的高频抖动传递测试程序,该程序正式要求60 dB的衰减(任何供应商的任何线路接口IC在所有操作条件下都无法达到的性能水平),最新的62411规范仅要求40 dB衰减。

编辑:hfy

-

CS3302A 与 CS3302 的操作差异2021-06-17 7916

-

介绍CS61575和CS61574A PCM线接口电路振动衰2009-06-16 855

-

介绍CS5521 CS5523 CS5522 CS5524 CS5528和CS5525 CS5526中放大器的性能以及如何用在大直流电压测量方面2009-06-11 1501

-

CS5521 CS5522 CS5523 CS5524 CS5528 AD转换器与PIC16C84微控制器接口2009-06-10 1317

-

CS4923 CS4924 CS4925 CS4926 CS2009-05-13 818

-

CS51023A, CS51024A pdf datashe2008-10-22 921

-

cs54111/cs54112/cs54113/cs54112008-07-20 1019

-

CS51411/CS51412/CS51413/CS51412008-07-19 1164

全部0条评论

快来发表一下你的评论吧 !