如何提高信号完整性,降低噪声或降低功耗

描述

EDN文章中介绍的一些技术向您展示了如何提高信号完整性,降低噪声或降低功耗。我们作为工程师最大限度地提高性能的方法之一就是坚持建立设计规则。但是,如果遵守这些规则会增加成本并使您的产品无法销售?这是低成本嵌入式和消费产品设计人员经常面临的困境。

为了深入了解这种产品,我们在Mentor Graphics对BeagleBone Black进行了分析,BeagleBone Black是许多面向制造商和业余爱好者的低成本微控制器板之一。我们的分析表明,“黑色”的设计师是如何做出许多工业产品设计师不需要进行折衷的。由于BeagleBone系列的无畏设计师发布了他们的设计,原理图,布局和代码,供我们其他人进行审查和改进,因此我们可以从信号完整性的角度对其进行分析和仿真。我们的分析揭示了有关设计师在保持性能,降低成本的同时进行权衡取舍的故事,我们可以将这些经验教训应用到我们自己的设计中。

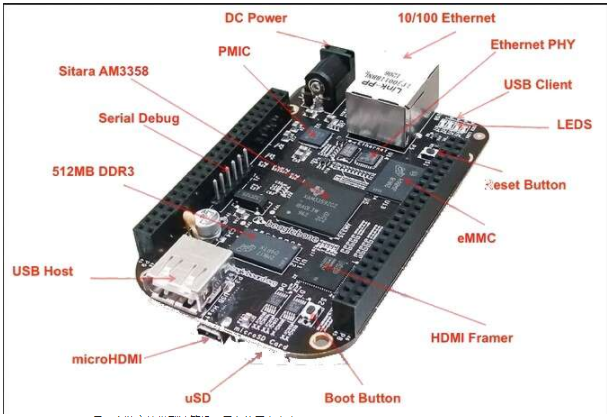

Black最初于2013年发布,是开放源代码爱好者计算机家族的一部分。它围绕德州仪器AM355x “ Sitara”处理器构建,具有512 MB的板载RAM,2 GB的板载闪存以及以太网和HDMI端口。Black(图1)随Debian Linux一起提供在板载闪存中,带有micro-SD卡插槽可用于重新刷新板载内存或直接托管操作系统。黑色已被较新的型号取代,不再是最先进的设备。它仍然可以在亚马逊上以65美元的价格购买。

图1. BeagleBone Black是一台独立的微型计算机,只有信用卡大小。

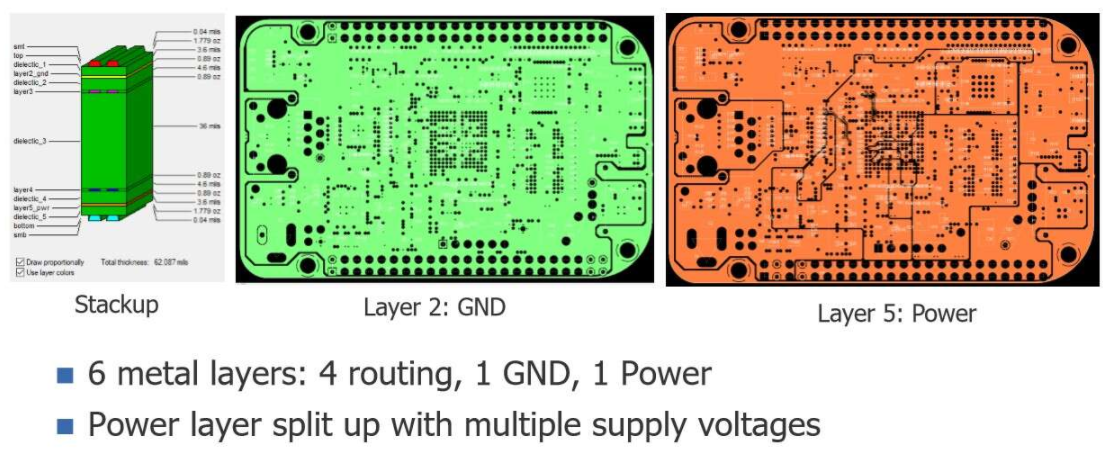

一旦我们了解了Black的堆栈,设计低成本系统的挑战就变得显而易见(图2)。该电路板只有四个布线层和两个平面层,电源平面层被切成小块,以适应运行该电路板所需的不同电压。“最佳实践”高速设计告诉我们,信号在芯片之间传播时,我们应保持恒定的参考电压,并在可能的情况下将其接地。双倍数据速率(DDR)存储器已长期使用电源参考信号来适应双列直插式内存模块(DIMM)设备上的有限层数;显然,我们在这里会遇到同样的问题,我们必须与在其上切成小块的参考平面抗衡。

图2.黑色的电源层分为多个部分以适应不同的电压。

注意中间电介质在叠层中的厚度。顶部和底部(电气)相距较远。原因很明显:为了使板具有足够的机械刚度,必须将其确定为一定的厚度,而较大的中心芯线是实现此目的的最佳方法。这意味着我们不能依靠嵌入式电容来对电源层和接地层进行解耦,因此任何从上到下穿越的信号过孔都需要附近的去耦电容器来承载其返回电流,并且这些电容器的有效性受到以下因素的限制:电容器环路电感。

黑色上的DDR3接口(图3)非常简单。处理器直接与单个DRAM芯片对话。从原理图和布线的角度来看,没有比这更简单的了。事实证明,简单不一定意味着容易。Black的DDR3接口有一些有趣的故事,以讲述创建低成本设计的含义。我们将从最佳实践/设计指南的角度来解决这一问题-DDR3定义了一些物理和电气设计目标,这些目标必须满足才能使设计正常工作。

图3.黑色DDR3接口直接与单个DDR存储器芯片对话。

DDR3设计规则

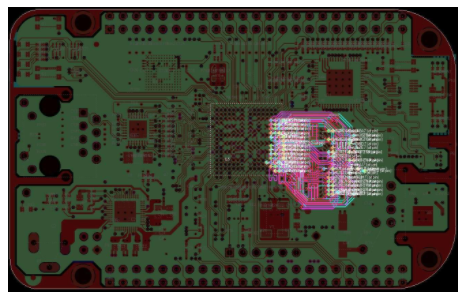

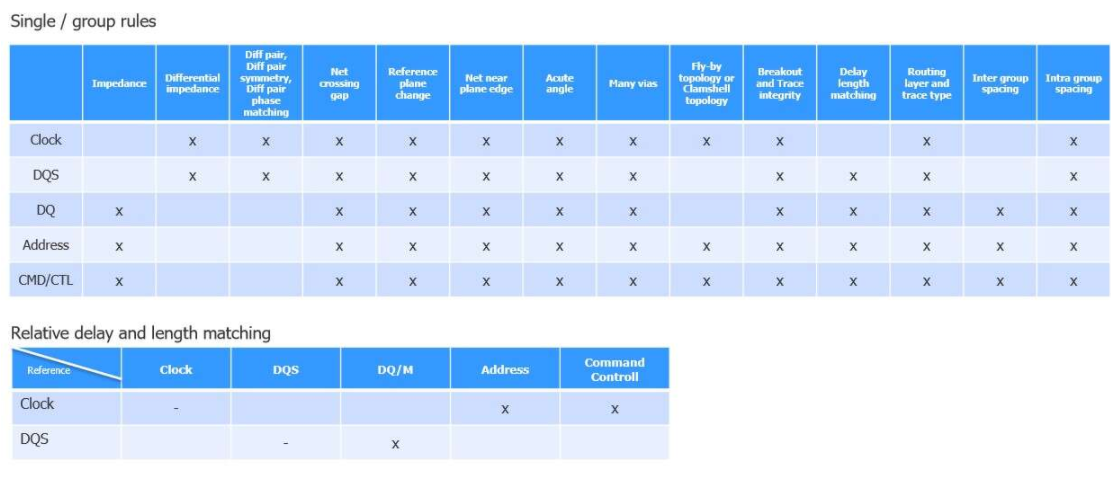

下面显示了DDR3接口的一些常见物理布局设计规则(图4)。不同的团队对矩阵的定义会有所不同-尤其如此,因为DDR3的JEDEC规范仅定义了接口的DRAM端。不同的控制器将具有不同的电气和时序要求,这可能会影响设计的放置和布线方式……但是基本思想仍然是相同的。

图4.常见DDR3设计规则示例。

这些构成了“最佳实践”设计规则的主体,可以用作放置和布线DDR3设计的起点。然后应使用布线后信号完整性和时序分析来分析布线设计板,以识别和解决任何潜在问题。但是,通常情况下,会根据最佳实践规则放置和布线设计,并且在制作过程中不会进行信号完整性仿真。为什么?因为详细的信号完整性和时序分析是大多数设计人员无法企及的。

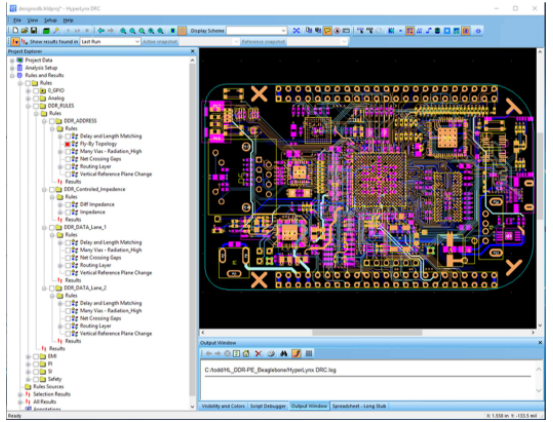

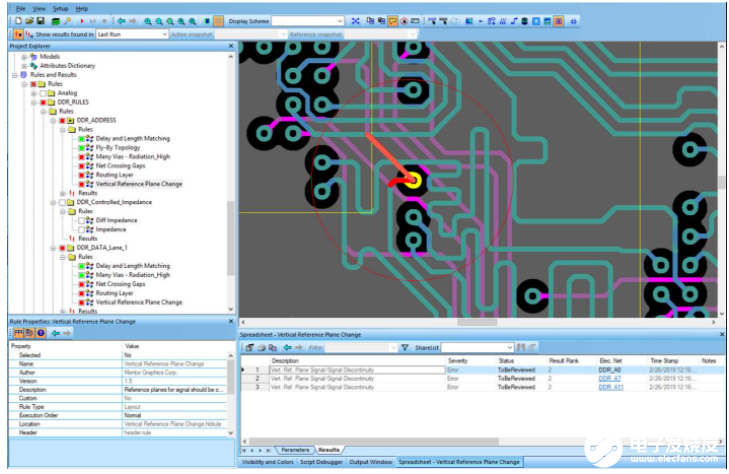

图4中的物理和电气规则足够具体,我们可以从设计布局中自动检查它们(图5)。在这种情况下,我们为DDR3数据网,地址网等定义了特定的规则集。根据设计是否通过相应的检查,每个特定规则旁边的框将以红色或绿色突出显示。

图5.自动检查DDR3设计规则。

请注意,我们正在完成的Black设计上运行这些检查。如果准则规则如此重要,那么黑方将如何无法通过所有这些检查,并且仍然可以很好地工作以成为运输产品?好吧,事实证明,指导方针就是:指导方针。违反准则并不意味着设计就行不通,而只是意味着存在一个问题,需要更仔细地调查和理解。如果分析表明该设计仍然可以运行,则可以免除违规并继续进行。如果违规是一个真正的问题,那么您可以纠正问题并重复该过程。

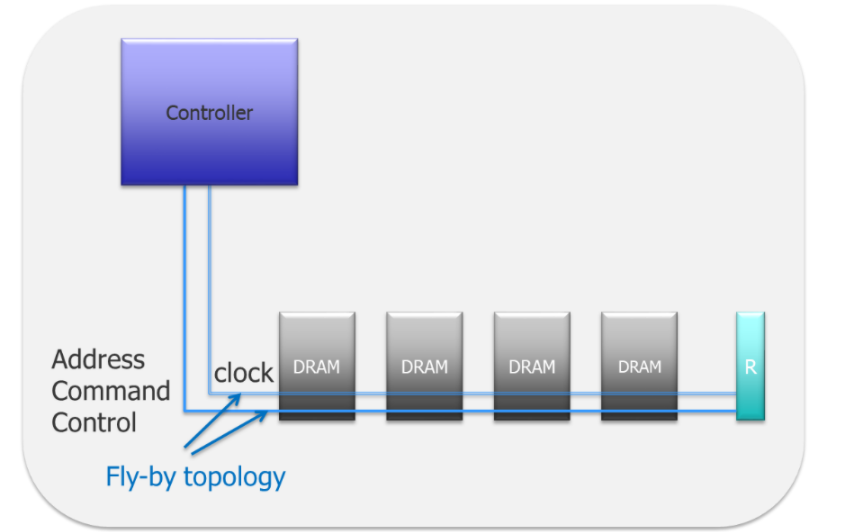

DDR3使用“飞越”拓扑来路由地址,命令/控制和时钟信号(图6)。信号由控制器驱动,并以菊花链的方式通过不同的DRAM路由,并在线路末端并联一个终端。这种方案以到达每个设备的时钟的时滞为代价,使每个DRAM的时钟信号质量最大化。这与用于DDR2和更早技术的“时钟树”方案形成鲜明对比,后者试图在每个设备上同步时钟的到达。时钟树方法必然涉及分叉轨迹,这会导致反射,从而降低信号质量。这些反射在DDR2速度下是可以容忍的,但在DDR3及以后的速度下是不能容忍的。

图6.连接多个DRAM设备时,DDR3使用“ Fly-by”拓扑进行地址和时钟路由。

对于DDR3及更高版本,这些网络在线的末端并联端接,以最大程度地减少反射,否则会影响信号质量。时钟到达不同DRAM的时滞表示DRAM将在稍有不同的时间将数据发送回控制器(读取)。这也意味着控制器将需要在稍有不同的时间将数据发送到DRAM(写),以确保符合DRAM上的DQ / DQS / CLK关系。控制器处理这些时序偏移的过程称为读取均衡和写入均衡。

第一个问题是我们需要调查与地址网的关系。网络上的并联终端电阻丢失。黑人设计师为什么要这样做?答案非常简单-成本。并联终端电阻要花钱并占用PCB面积,这两者在像Black这样的设计中都是很宝贵的。在像这样的大批量,低成本应用中,设计师可能不想添加不必要的东西,即使它是“标准”设计指南的一部分。哪个提出了问题–我们如何确定没有这些电阻的设计就能工作?我们将如何进行需要证明的设计分析?

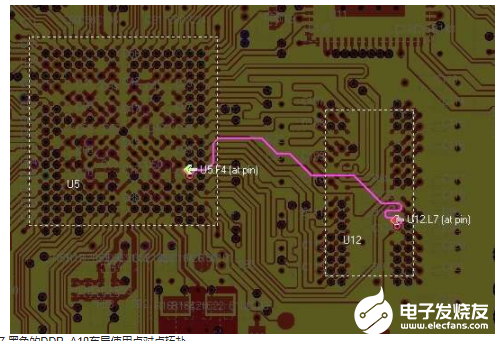

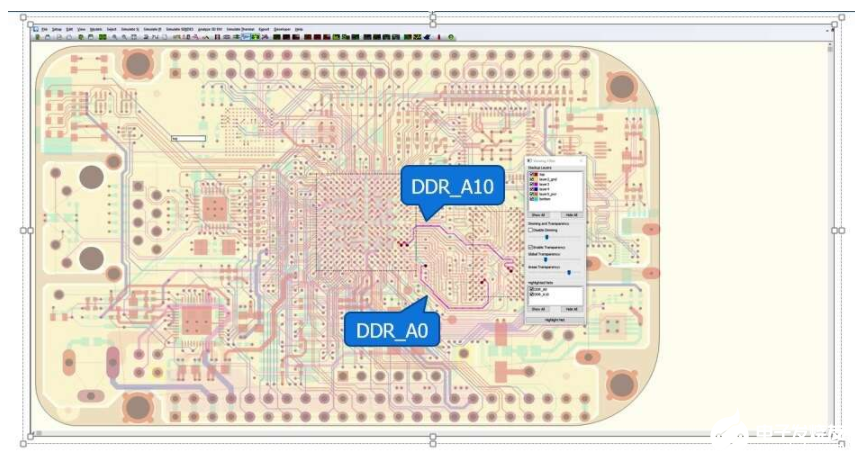

DDR地址线10(DDR_A10)显示在图7的PCB布局中(如果您想知道为什么我们不选择DDR_A0,我们将在后面进行介绍)。处理器在左侧,单个DRAM在右侧。现在,图片开始成为焦点-Black的地址总线不是点对点的多点拓扑。请记住,在存在多个负载时,DDR3中并行终止的目的是管理地址/命令/控制网络的信号质量。考虑到这一点,让我们集中讨论Black上的地址线实际上需要提供什么样的信号质量,而不是在更一般的情况下DDR3准则告诉我们的。

图7.黑色的DDR_A10布局使用点对点拓扑。

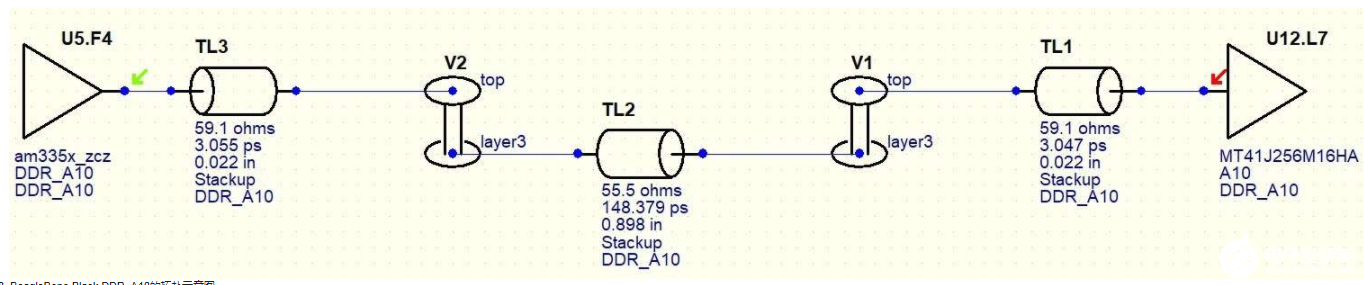

图8显示了该网络的布局前示意图。这种表示形式特别有用,因为它使我们能够对网络进行快速的“假设分析”更改,以探讨它们对信号行为的影响。Black的最大DDR3数据速率为1600 MT / s,因此让我们从运行模拟开始,看看信号质量如何。

图8. BeagleBone Black DDR_A10的拓扑示意图。

知道会发生什么

让我们先退后一步。信号完整性专家Eric Bogatin提供了高速设计的经验法则,其中第9条法则指出:“切勿在没有预测您首先看到的情况下运行仿真。” 那是非常好的建议。如果您不知道期望得到什么结果,您如何知道模拟是否正确运行?

仿真通常会运行到完成并产生结果,但是建模或设置问题有很多方法会影响结果的有效性。考虑到这一点,您应该验证基本假设,简单地开始并以受控的方式增加模拟的复杂性,以便可以预测任何模拟实验的结果。这与说仿真总是可以预测预期的结果不同,但是它确实表示可以解释和解决意外的结果。

您在这里应如何应用该原则?在点对点拓扑和未端接的接收器中,您可能希望入射波形的电压加倍,并反射回驱动器。如果驱动器的输出阻抗与传输线的阻抗相匹配,则驱动器将吸收反射信号。驱动器的输出是否与线路阻抗匹配,或者是否使用串联电阻将驱动器的(较低)输出阻抗与线路阻抗匹配,就是这种情况。该技术被称为“串行端接”,是一种使用点对点拓扑结构控制信号质量的有用方法。它具有减少开关期间输出驱动器所需功率的额外好处,这是一项额外好处。

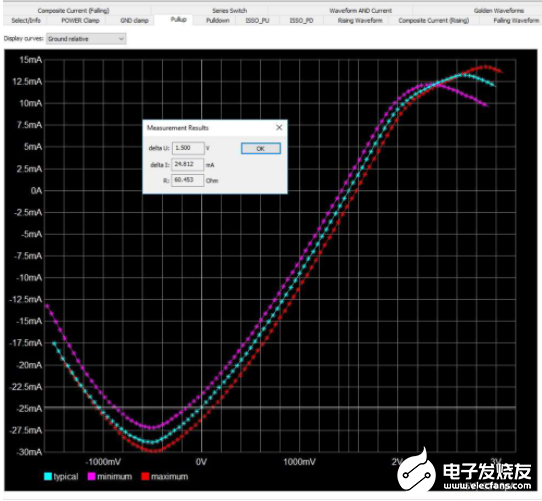

那么,我们如何弄清楚如何为Black设置串联终端?好吧,您需要找到一个驱动器设置,其中驱动器阻抗与板上走线的传输线阻抗匹配,我们知道大约为60Ω。我们在IBIS模型中查看了处理器的驱动器电压与电流(V / I)曲线,以了解是否可以找到合适的设置。

我们绘制了处理器地址线输出缓冲器的上拉/下拉曲线,并使用该曲线的斜率来计算驱动器的有效输出电阻。黑色的地址输出驱动器是可配置的,具有以下设置:5 mA,6 mA,7 mA,8 mA,9 mA,10 mA,11 mA和12 mA。当我们在输出阻抗上绘制不同的设置时,我们发现7 mA的输出提供了与我们要寻找的阻抗的良好匹配(图9)。

图9.使用处理器模型的地址线V / I曲线的斜率来计算输出阻抗。

接下来,我们对7 mA左右的设置进行了仿真,并查看我们的预测如何与结果匹配。

并非总是需要额外的余量

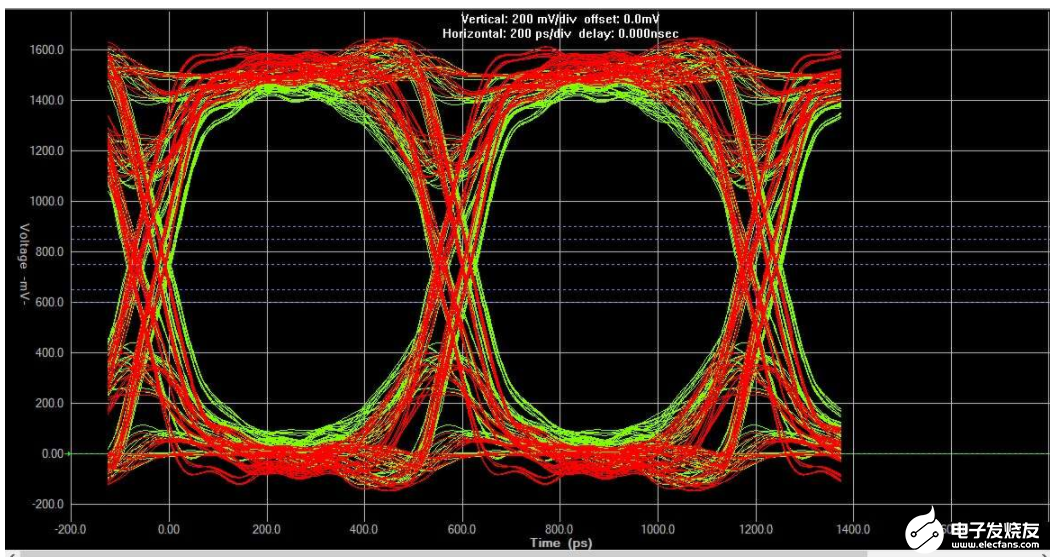

正如预期的那样,7 mA(图10眼图的绿色区域)设置工作得很好。但是,我们注意到8mA设置提供了额外的设计余量。为什么?因为当我们仅考虑使驱动器阻抗与线路阻抗匹配时,我们并未考虑接收器输入端的电容性负载,因为电容性负载需要额外的电流才能充电。这是通过仿真进行受控实验的一个很好的例子–我们没有无法获得我们期望的结果,但是我们解释了原因并因此获得了见识。

图10. 1600 MT / sec时7 mA和8 mA驱动器的眼图。显示7 mA可产生更宽的眼图张开度。

我们还运行了其他驱动器强度,未在图10中显示。我们注意到,驱动器设置高于8mA会增加波形的峰峰值电压,但这并没有进一步扩大视野。换句话说,更强地驱动信号只会给系统增加噪声。

说实话,由于DDR3地址网络是设计为端接的,因此无论选择哪种设置,我们都有很多眼图余量–我们甚至可以将驱动器的强度降低到5 mA,但仍然有足够的余量。网络末端的并联端接通常将峰峰值信号摆幅减小一半,因此我们有足够的余量来处理。

DDR3设计的另一个标准经验法则是,信号在芯片之间传输时应保持恒定的参考电压。参考电压可以是GND或DDR I / O的电压轨,但是无论信号以哪个参考电压启动,该参考电压在信号的整个路径上都应保持一致。在信号改变层的情况下,相关的参考平面需要在附近具有缝合过孔,以减轻返回路径的影响(图11)。

图11.当信号改变层时,信号参考平面通常需要缝合通孔以保持参考一致性。

信号可以更改包含两个不同参考电压的参考平面,只要两个参考平面在信号过孔附近充分解耦即可。这样做的问题是,去耦电容器所涉及的电感必然比通孔拼接策略要大,因此通常可以避免这种情况。

当我们在黑色(图12)上运行DDR设计规则检查时,我们发现几个地址网违反了该准则,并同时参考了接地层和电源层进行了布线。为什么?因为黑方只有两个参考平面,所以设计人员没有足够的空间在上两层存储DDR信号。他们将所有数据信号路由到上层微带线和带状线层(参考GND)。这是有道理的,因为DQ信号以地址信号频率的两倍运行。但是,某些地址信号是同时参考GND和DDR电源进行路由的,这意味着返回电流必须在路由中间找到这两个平面之间的路径。

这就引出了一个问题:这对信号质量有多大影响?黑人设计师如何知道他们负担得起?我们来看两个地址信号(图12)。

图12.黑色上的地址线。

地址线更改平面

地址线10(图13)从顶层(微带)启动,在其大部分长度上向下过渡到layer3,然后切换回顶层以连接到设备引脚。由于顶层和第3层位于第2层的任一侧(接地平面),因此返回路径接近理想状态。返回电流不受干扰,因为它永远不会改变层数。

图13.地址线10穿过BeagleBone Black PCB的路线。

地址行0是另一个故事(图14)。它从顶部微带层(参考接地)启动,切换到底部带状线层(参考电源),切换回第3层(参考接地),然后在顶层(参考接地)结束。这意味着A0在大约1英寸的范围内两次切换其参考电压。从控制器到DRAM所需的时间。有什么影响?

图14.地址线0沿着黑色的四个PCB层中的三个层移动。

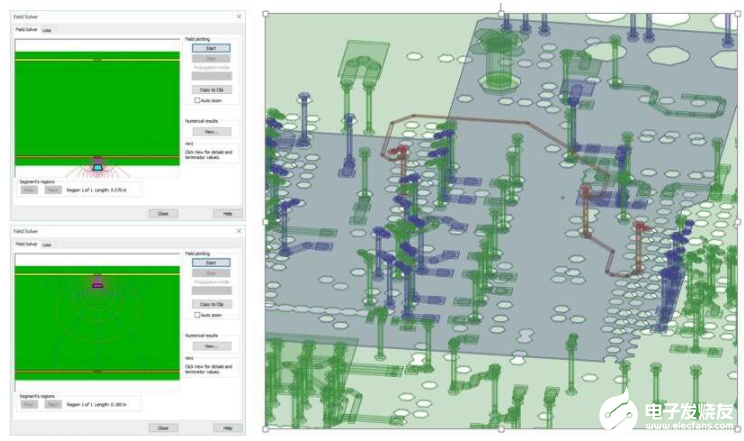

基本的信号完整性分析始终假设信号的返回路径是理想的。自IBIS于1993年问世以来,所有信号完整性工具均是如此。高速信号与系统的配电网络(PDN)相互作用,而这些相互作用只会使信号降级。对这些交互进行建模和仿真的仿真工具被称为“ Power-Aware”仿真工具。对于黑色,这是我们需要量化A0信号更改参考电压的影响的分析类型。Power-Aware仿真是信号完整性方面的一个相对较新的发展-早在2012年,Black设计师肯定还没有使用它,但是我们今天可以使用它来量化其决策的影响。

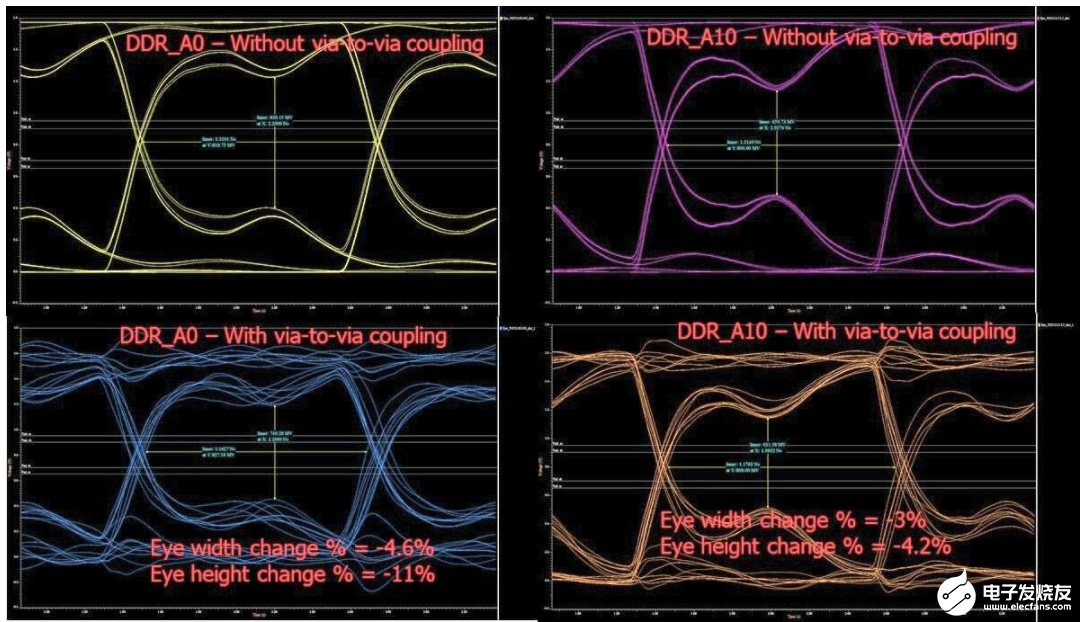

图15中图的左侧显示了A0信号,而右侧显示了A10。顶部的图显示了具有理想返回路径的网络仿真,而底部的图显示了当考虑信号的实际返回路径时眼图裕量如何受到影响。对返回路径进行建模时,A0信号的眼高降低了A10的眼高的两倍。由于信号开始时有很大的余量,因此这仍然是可接受的信号质量。如果我们不是点对点运行信号,并且与并行端接相关联的眼高降低,情况可能会有所不同。

图15.功耗感知的仿真结果表明,即使眼睛高度显着下降,仍然有足够的睁眼余量供Black使用。

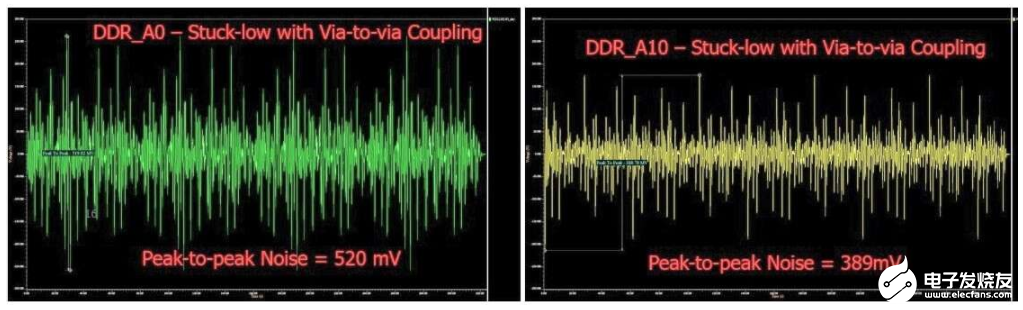

我们还可以评估由它们的邻居的开关活动在这些信号上引起的噪声。为此,我们通过将利息净额稳定在高或低状态来将其视为受害净额。我们在总线上的其他网络上放置一个随机模式,并测量耦合到目标信号上的噪声。我们在受害网上看到的任何波动都是耦合噪声的结果。不出所料,图16中A0上的噪声大于A10上的噪声。

图16.建模返回路径时的地址线噪声耦合

即使在接近理想的返回路径的情况下,耦合噪声似乎也很高–接近390 mV!请记住,幅度和时间是耦合噪声的重要考虑因素,而不仅仅是幅度本身。如果在采样(定时)信号时没有发生耦合噪声,则不会产生任何影响。对于这样的并行总线,在信号切换时由于串扰会产生大量噪声是很常见的,因为所有信号都一起切换。重要的一点是,在采样信号时,噪声已经消失了,图16并未对此进行描述。

切换信号基准电压对A0的影响还不算太坏-设计具有足够的裕度,这很重要。如果设计人员严格遵守DDR3设计的既定经验法则,他们可能会增加额外的电阻器,并可能增加一个平面对(以提供额外的接地层)。这些更改实际上不是必需的,只会使产品成本增加而没有任何实际好处。设计师如何知道他们可以做到这一点?我们不知道–也许他们使用了原型和实验室特性,并对其进行了仔细的测试。具有功耗意识的建模和仿真表明,即使违反了既定的DDR设计指南,该设计也可以有足够的余量。

当然,我们知道,黑人从几年前就开始工作了。但是,当今的大批量,低成本设计存在相同的问题-制造成本至关重要,仅遵循传统的经验法则通常会导致设计过于昂贵而无法实现。因此,我们一直在努力展示现代分析工具如何帮助您确定在何处“违反规则”,何时何地以及如何进行。

— Todd Westerhoff是MentorGraphics的电子板系统部分的高速和模拟/混合信号系统设计产品营销经理。

编辑:hfy

-

什么是走线的拓扑架构?怎样调整走线的拓扑架构来提高信号的完整性?2023-11-24 1663

-

如何利用全新互连系统提高电源完整性和信号完整性?2023-08-30 2133

-

如何最大程度地降低地弹噪声对单板信号完整性影响?2023-06-26 1892

-

如何在汽车设计中降低功耗2022-11-04 827

-

【信号完整性】地弹噪声对信号完整性的影响2022-10-25 3566

-

如何降低地弹噪声对单板信号完整性影响2022-07-27 2840

-

电源和信号完整性的分析与测试2022-01-07 1391

-

什么是电源和信号完整性?2021-12-30 2116

-

如何实现低噪声和高精度的增强电源和信号完整性2021-04-21 4847

-

信号完整性对EMC的影响有哪些2020-07-09 4452

-

PCB信号完整性2018-11-27 2734

-

提高信号完整性的PCB材料2018-02-05 1970

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

降低噪声与干扰2010-02-26 4280

全部0条评论

快来发表一下你的评论吧 !