pcb等长设计为什么会出现时延差异?

描述

下面我们来看看,为什么会出现此类时延差异?

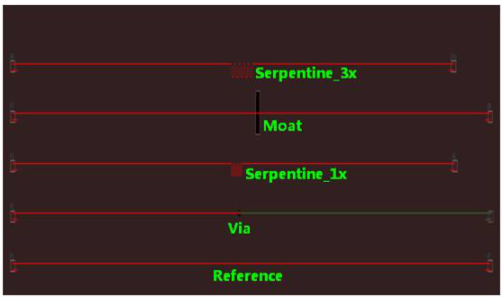

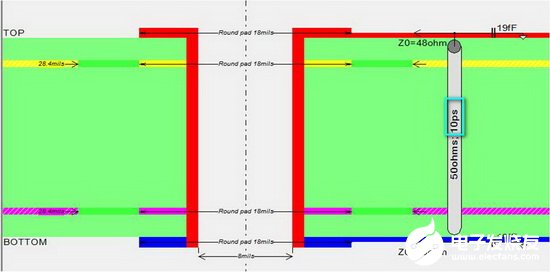

Case1:过孔带来的时延差值为11ps,这个就很好理解了,过孔有一定的物理长度,该过孔长1mm,过孔本身还具有寄生电容和寄生电感,所以实际带给信号的传输线延会比普通传输线要大,本例中是11ps,而且这个延时跟频率有一定关系。使用软件单独提取该过孔的模型,如下图,过孔的延时为10ps,与仿真得到的11ps差不多。

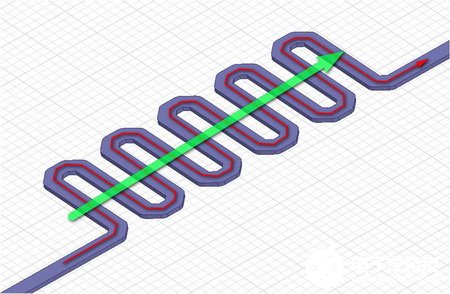

Case2:1倍线宽的蛇形绕线带来的延时差异是-10ps,比参考线快了10ps,造成延时差异的主要原因是信号的自耦合现象。在绕蛇形线的时候,期望的信号传输路径是沿着下图红色箭头传输,可是由于蛇形线之间的距离太近,导致信号实际传输路径是下图绿色箭头所指示的那样(当然,实际上信号也不会以绿色箭头那样传输,在这里这么标注只为了大家更形象的理解记忆,后期会有详细解释)。所以就导致了信号提前到达接收端。

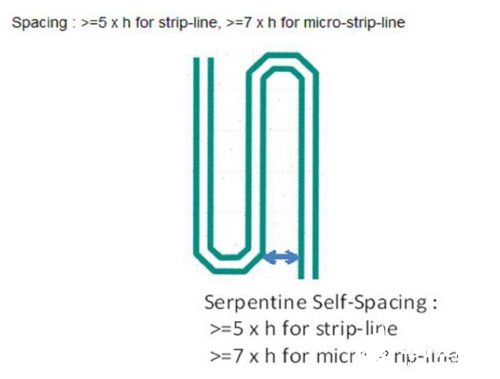

如果把蛇形线之间的间距拉开,比如从1倍线宽拉到3倍线宽,信号的延时差异立刻缩小到-2ps,差异就没有那么大了。所以在使用蛇形线匹配长度时,要注意蛇形线之间的间距一定要拉开,拉开多远可参考下图

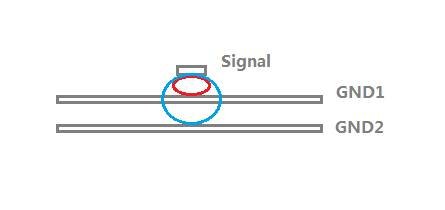

Case3:当参考线跨过50mil的分割线时,带来的延时为14ps。在PCB设计中,同一层的平面常常会因为不同的用途而分割开来,由此就会导致很多分割线。众所周知,传输线由信号路径和返回路径组成,信号的返回路径通常在距离信号路径最近的参考层上,且在信号路径正下方(如下图红色圆圈)。如果跨过分割线,信号的返回路径被切断,信号就要寻找其他的返回路径回流,因此信号的回路面积就增大(如下图蓝色圆圈),传输线延时就会增大。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AD设计DDR3时等长设计技巧2025-07-28 695

-

PCB设计中常见的走线等长要求2023-11-24 7025

-

PCB设计工程师浅谈绕等长的概念2021-01-20 7175

-

PCB设计中如何实现等长走线2020-11-22 21264

-

PCB设计做等长走线的目的是什么2020-10-24 11218

-

PCB技术:如何解决蛇形等长直角锐角2020-10-18 4461

-

PCB设计中上锡为什么会出现不良2020-04-09 5502

-

PCB设计中绕等长线的方法和技巧2019-04-26 12220

-

Altium designer 等长布线2018-03-09 25323

-

DDR布线等长问题2016-01-09 4099

-

pcb editor里面调地址等长线的时候右下角出现的提示条是什么意思?有红色的绿色的?2015-07-27 11051

-

信号在PCB走线中关于串扰 , 奇偶模式的传输时延2015-01-05 6353

-

PCB设计规则——等长 的体会2014-12-01 8053

-

信号在PCB走线中传输时延(下)2014-10-21 3049

全部0条评论

快来发表一下你的评论吧 !