全面描述SADP / SAQP流程的工作方式

描述

作者: JAE UK LEE和IMEC RYOUNG-HAN KIM博士,DAVID ABERCROMBIE,REHAB KOTB ALI和MENTOR的AHMED HAMED-FATEHY

自对准多图案化工艺已成为最先进节点的必要条件,在传统节点上,无论使用何种光刻技术,传统的光刻蚀刻多图案化工艺都开始遇到对准控制问题。由于自对准流程与传统流程相比有很大不同,并且更为复杂,因此Mentor与IMEC合作,为两个铸造厂和设计公司的工程师提供了内部了解三个生产自对准流程(SADP,SAQP和SALELE)的信息。通过分步说明,我们向您解释并显示了确保在当今最先进的节点中确保布局保真度所需的自对准模式创建的复杂性。

当半导体行业达到20 nm工艺节点时,他们面临着新的制造挑战。极紫外(EUV)光刻技术仍未投入生产,并且使用的193i光刻技术无法准确解析如此小的布局。解决方案是引入多图案化,该过程是在几个掩模之间划分布局,从而在要素之间提供足够的光刻间距,以实现可行的良率解决方案。最初,双图案(DP)光刻-平版蚀刻(LELE)工艺提供了足够的可制造性。随着行业转移到较小的节点,DP LELE不再适合某些层,因此需要三重或四重图案化(TP / QP)光刻法(LE n)工艺来确保可制造性。

但是,所有LE n多图案化工艺的主要关注点是对齐控制。在这些工艺节点上,实际上不可能在多个掩模之间实现精确对准,这使得难以获得所需的产量。EUV光刻技术的出现最终提供了新的分辨率功能,因此许多使用TP或QP和深紫外(DUV)光刻技术的工艺层都经过重新设计,以使用单个EUV掩模,但是即使在最小的节点上,该工艺也面临着分辨率难题。面对这些挑战,整个行业的趋势是朝着采用自对准多图案工艺的方向发展,其中使用制造工艺本身来创建所需的布局。

最常见的自对准多重图案化技术称为自对准双重图案(SADP)。SADP中使用的技术也可以很容易地扩展到自对准四重图案(SAQP)。我们将描述SADP / SAQP流程的工作方式,并解释这些流程所需的块遮罩(有时称为剪切)遮罩的一些选项。然后,我们将介绍另一个过程,称为自对准LELE(SALELE),该过程结合了自对准多图案和LELE过程的各个方面。IMEC和Mentor一直在共同努力,以创建,优化和设计使能SALELE流程,与SADP / SAQP流程相比,它具有一些可观的优势。

自对准多图案

一般而言,所有自对准多图案化过程均包含以下步骤:

- 打印心轴轨道。

- 在印刷的心轴图案的侧面上增加侧壁。

- 移除心轴图案。

- 在侧壁之间开发最终制造的图案。

- 添加电介质块以在最终目标中创建所需的尖端到尖端的间距。

自对准双图案

SADP工艺背后的基本思想与DP LELE的基本思想相同-每隔一行以所需间距的两倍打印一次,以适应光刻限制。但是,SADP工艺不是使用另一个掩模来印刷第二组交错线,而是使用沉积和蚀刻工艺来创建它们,这些沉积和蚀刻工艺不仅可以创建第二条线,而且还可以自动对齐这些第二条线,而无需借助光刻技术[1,2]。虽然还有第二个光刻操作,但它用于对块/切割蒙版进行成像,以定义线条中尖端到尖端的间隙,从而形成最终形状。让我们来看一下基本的SADP流程。

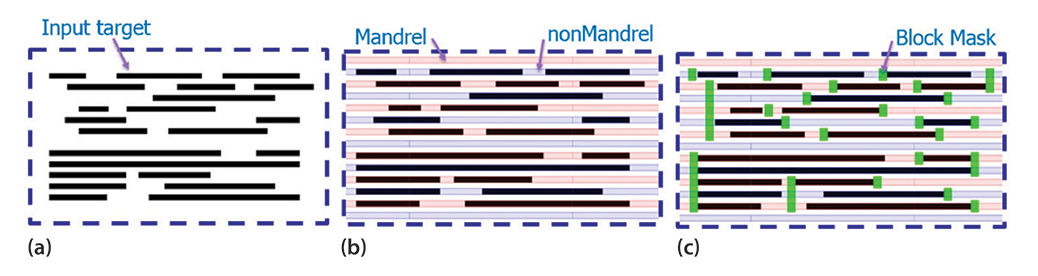

任何多图案化过程的第一阶段是分解或划分布局。如图1所示,SADP分解过程开始于将目标多边形(a)转换为心轴轨迹和非心轴轨迹(b)。所有目标形状都必须具有对称的光栅(轨道之间的间距相等),并且与轨道完全对齐。在SADP制造过程中,将虚拟金属添加到所需的目标,以将所有目标线延伸到边界。在创建轨迹之后,屏蔽(c)形状将在目标形状和虚拟金属之间创建所需的隔离(注意:必须仍然提取此非活性填充物以测量其对最终设计的电容影响)。

图1 SADP分解:(a)输入目标,(b)将输入目标分解为心轴和非心轴轨道,(c)添加块遮罩。

可以使用单个掩膜或多个掩膜(即,一个用于心轴轨道的块掩膜,另一个用于非心轴轨道的掩膜)印刷介电块,以定义轨道的活性金属部分(1c)的线端。SADP分解过程和获得干净的可制造布局的推荐程序已在行业文献中进行了广泛的讨论[3,4]。

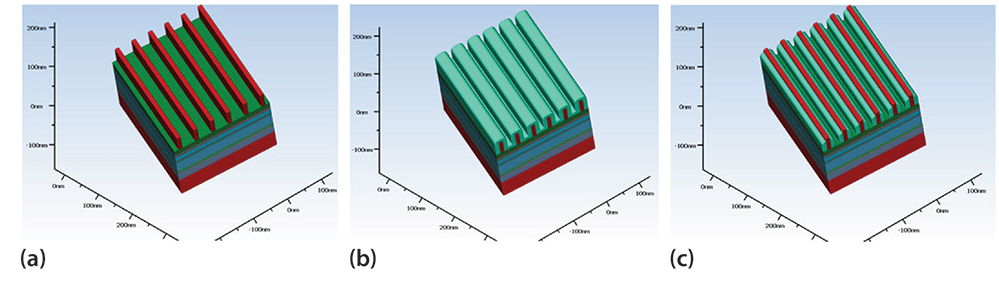

下一阶段是制造。如图2所示,SADP的制造过程包括三个步骤:

- 打印心轴轨迹并将其转移到硬掩模上。

- 在心轴磁道上共形沉积电介质垫片。

自顶向下蚀刻电介质间隔物以打开心轴轨道和下层,将剩余的电介质间隔物作为侧壁抵靠在心轴形状上。

图2 SADP的制造过程:(a)硬掩模上的心轴线,(b)电介质间隔物沉积,(c)蚀刻以打开心轴和底层的电介质间隔物。使用SEMulator3D生成的图像[10]

侧壁之间的空间成为非心轴轨道。由于心轴轨道的间距是所需间距的两倍,因此无需光刻即可在所有轨道之间实现最终的正确间距。该制造过程使光刻过程放松,并使铸造厂能够以高分辨率印刷掩模。下一步是添加块蒙版形状以在目标形状之间创建所需的隔离。但是,在进行此步骤之前,让我们先了解一下SAQP流程,并了解它与SADP流程的相似之处和不同之处。

自对准四重图案

要打印更小的间距,请使用SAQP。在此过程中,以四倍的间距打印心轴芯轨道,并执行两次连续的侧壁操作以获得最终间距。图3展示了SAQP流程的主要步骤:

- 打印心轴芯线并将其转移到硬掩模上。

- 使用原子层沉积(ALD)保形地沉积第一介电间隔物(侧壁)。

- 自上而下蚀刻介电垫片,以去除除芯棒芯线周围残留的介电垫片侧壁以外的所有材料。

- 蚀刻掉芯棒芯线和底层的硬掩膜,在未被电介质垫片覆盖的位置上形成第二根芯棒线。

- 使用ALD保形地沉积第二介电间隔物。

自顶向下蚀刻第二电介质间隔物以打开第二心轴和底层。第二介电间隔物侧壁之间的线为最终金属线产生正确的间距。

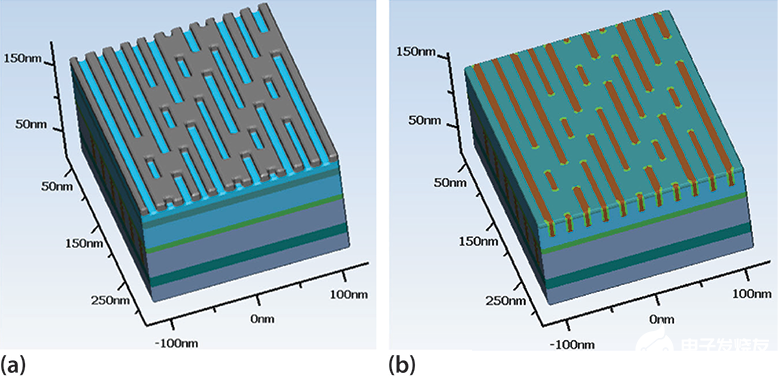

图3 SAQP的制造过程:(a)硬掩模上的心轴线,(b)第一电介质间隔物沉积,(c)蚀刻电介质间隔物以打开心轴和底层,(d)蚀刻心轴并将第一间隔物图案转移到底层中,是第二心轴,(e)在去除第一电介质间隔物之后在第二硬掩模周围沉积第二电介质间隔物,(f)蚀刻电介质间隔物以打开第二心轴和底层。使用SEMulator3D生成的图像[10]

自对准块

现在已经创建了自动对齐的轨道,我们可以开始使用一个或多个块蒙版创建最终布局的任务。用块掩膜创建的介电块(有时称为切口,视过程而定)将连续的走线分成独立的部分。使用单个块掩模的挑战在于光刻工艺限制了块形状之间的最小间距,这限制了合法的线端位置。一种解决方案是使用LELE或LE 3创建块遮罩(或多个遮罩)的过程,以在块形状之间留出更紧密的空间。但是,一个更密集,更可制造的解决方案是使用两个选择性块蒙版-一个用于剪切心轴线,另一个用于剪切非心轴线[8,9]。通过在侧壁之间使用两种不同的材料,该选择性阻挡掩模方法起作用。如图3(f)所示,我们已经有了第二种心轴材料,并且存在可以用另一种材料填充的间隙。结果,这些材料中的每一种都可以充当另一种材料的蚀刻停止层。

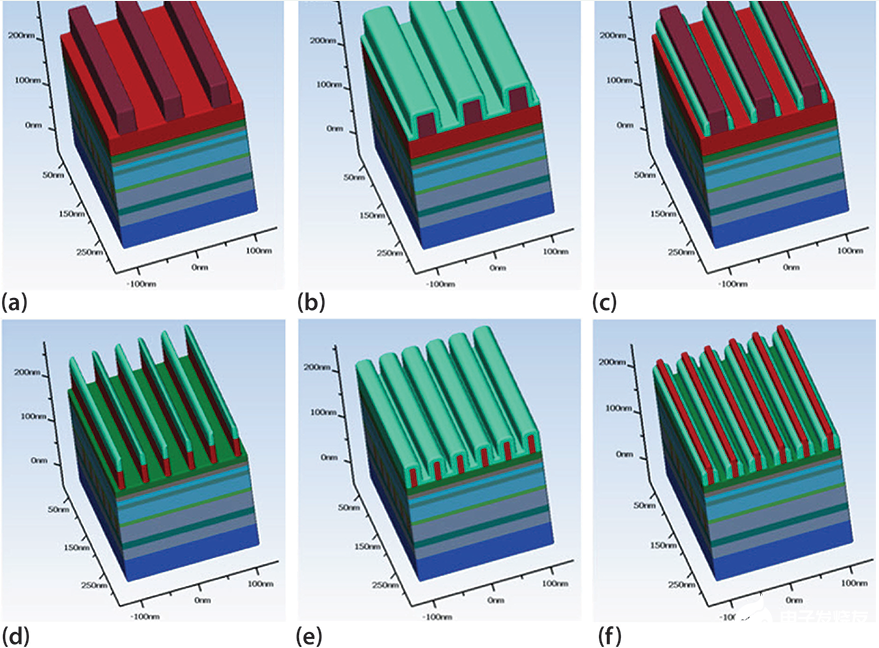

如图4所示,自对准块(SAB)过程从SADP / SAQP制造步骤的结果开始,并包括以下步骤:

- 分别用硬掩模和光致抗蚀剂涂覆晶片。

- 打印第一个遮罩并将其转移到硬遮罩上。图4(b)示出了去除光致抗蚀剂之后的图案。在此步骤中,使用带有EUV暗场掩模的正色调显影(PTD)工艺来生成孔图案。此过程是选择性的,因为它仅在非心轴磁道上添加了块。

- 用另一个硬掩膜涂覆晶片,以填充块的位置(孔)。

- 将硬掩模蚀刻回芯轴线的顶部。

- 去除硬掩模(仅保留块形状)。

- 分别用硬掩模和光致抗蚀剂涂覆晶片。

- 将光致抗蚀剂暴露在第二块掩模上。

- 打印第二个遮罩并将其转移到硬遮罩上。这次,负色显影(NTD)与EUV暗场掩模一起使用以创建柱子而不是孔。

- 在第二个遮罩未覆盖的位置蚀刻心轴线。

在去除光致抗蚀剂和硬掩模之后剩余的图案代表第二块掩模。现在,两个掩模完全转移到晶圆上。打开下面的层以形成沟槽,该沟槽将被金属填充以用于互连,除非存在块形状(蓝色或红色形状)。

图4 SAB的制造过程:(a)用硬掩模和光致抗蚀剂涂覆晶片,(b)将图案转印到硬掩模上,(c)用另一种硬掩模材料涂覆晶片,(d)回蚀硬掩模材料,(e)剥离第一硬掩模,(f)用硬掩模和光致抗蚀剂涂覆晶片,(g)将图案转移到光致抗蚀剂和硬掩模,(h)晶片上的最终块图案。使用SEMulator3D生成的图像[10]

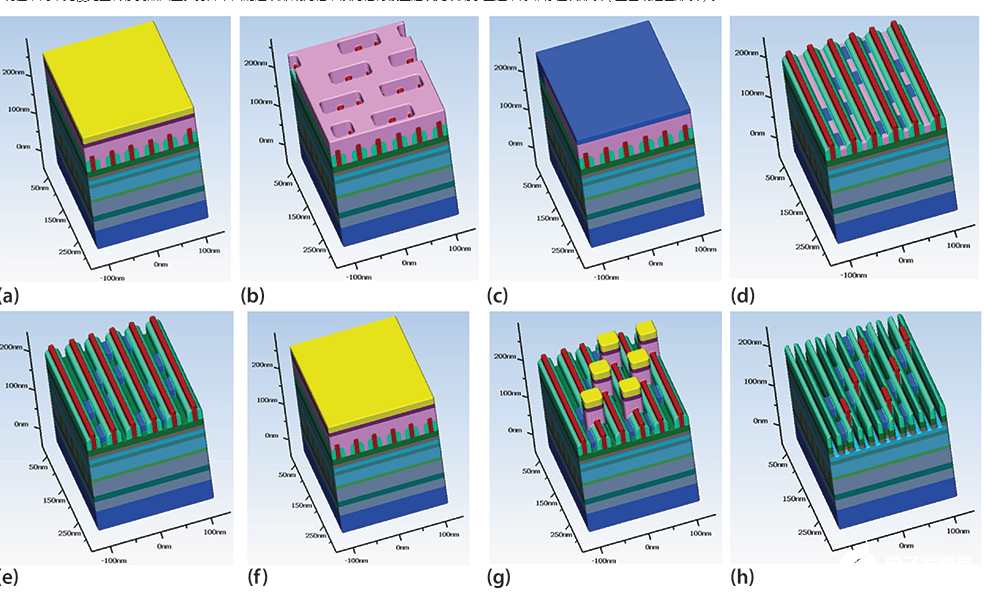

图5a显示了最后一层中的转移图案,其中包含由阻隔掩模和侧壁(电介质)创建的位置。该层中的开口是最终的金属位置(目标形状和添加的虚拟金属)。为了形成互连金属,在最后一层的开口处形成沟槽,并用金属填充(图5b)。

图5(a)最终层中的转移图案,(b)最终制造的形状。使用SEMulator3D生成的图像[10]

对于新节点,缩小到更紧密的间距通常会增加过程变化,这增加了对块可打印性的限制(块到块的距离受到限制,并且需要最小的块空间规则)。块形状的放置必须使用不同的技术进行优化,例如滑动,合并和放置某些块蒙版形状[3,4]。但是,我们仍然必须考虑由于虚设金属而导致的额外电容。

本系列的第2部分介绍了SALELE流程,并比较了本系列涵盖的三个流程中每个流程的相对优点。

参考

- S. Natarajan等人,“具有第二代FinFET,气隙互连,自对准双图案和0.0588 µm2 SRAM单元尺寸的14nm逻辑技术”,IEEE国际电子设备会议(IEDM),旧金山,加利福尼亚,2014年,第3.7.1-3.7.3页。

- Christopher Bencher,陈永美,戴慧雄,沃伦·蒙哥马利,胡尔·胡里,“通过CVD间隔物自对准双图案(SADP)进行22纳米半间距图案”,Proc.Natl.Acad.Sci。SPIE 6924,光学微光刻XXI,69244E(2008年3月7日)。

- David Abercrombie,Rehab Kotb Ali,Shetha Nolke,Ahmed Hamed-Fatehy,Ahmed。“使用口径多模式填充/剪切SADP ”,西门子业务部Mentor,2017年4月。

- Jeanne-Tania Sucharitaves,Sam Nakagawa,Robert Yarnell,David Abercrombie,Shetha Nolke,Rehab Kotb Ali,“ SADP设计完成:使用DRC自动修复改善结果”,西门子业务部Mentor,2018年10月。

- Joost Bekaert等人,“在IMEC的iN7上对BEOL金属层进行SAQP和EUV块构图”,Proc。SPIE 10143,极紫外(EUV)光刻VIII,101430H(2017年3月24日)。

- Rehab Kotb Ali,Ahmed Hamed-Fatehy,James Word,“选择性蚀刻SADP / SAQP的集成制造流程”,Proc。SPIE 10588,《可制造性XII的设计-过程-技术共同优化》 105880Q(2018年3月20日)。

- Jongsu Lee等人,“器件结构上具有光学CD计量学的间隔器多图案控制策略”,Proc.Natl.Acad.Sci.USA,88,3593-2,1993。SPIE 9778,《微光刻XXX的计量学,检查和过程控制》,97782B(2016年3月8日)。

- AngéliqueRaley等人,“具有EUV自对准双图案的关键低于30nm间距Mx电平图案的自对准阻挡集成演示,” J。Micro / Nanolith。MEMS MOEMS 18(1)011002(2018年7月31日)。

- Benjamin Vincent,Joern-Holger Franke,Aurelie Juncker,Frederic Lazzarino,Gayle Murdoch,Sandip Halder,Joseph Ervin,“用于iN5金属2自对准四重图案的自对准块和完全自对准通孔,” SPIE 10583,极紫外(EUV)光刻IX,105830W(2018年3月19日。

- 半导体解决方案概述,Coventor,Inc.

Jae Uk Lee是计算光刻领域的高级研发工程师,包括源掩模优化/光学接近度校正以及IMEC的可制造性设计。

Ryoung-han Kim博士是IMEC物理设计/设计自动化,OPC / RET和测试现场/卷带的主管。

David Abercrombie是西门子公司Mentor的高级物理验证方法的程序经理。

Rehab Kotb Ali是西门子Mentor的高级产品工程师,致力于先进的物理验证技术。

Ahmed Hamed-Fatehy是西门子公司Mentor的RET产品的首席产品工程师。

编辑:hfy

-

GPIO基本结构和工作方式介绍2022-01-11 1103

-

SPI总线的工作方式是什么?2022-01-25 1133

-

α调制工作方式原理2009-07-27 727

-

MAX714工作方式及其转换2009-10-27 829

-

鼠标的工作方式2009-12-28 1089

-

Wifi模块的工作方式功能是什么?2012-06-12 6225

-

步进电机及驱动电路工作原理及工作方式介绍2016-05-11 1276

-

8255a有哪几种工作方式?8251a的工作方式及工作原理2018-05-23 67390

-

ups不间断电源工作方式2019-06-26 8742

-

AD级联的工作方式配置和AD双排序的工作方式配置详细说明2019-12-23 1424

-

UPS电源有哪些工作方式?2021-11-09 1938

-

最常见的直流负载工作方式2024-01-18 1806

-

DC电源模块的原理及工作方式2024-04-24 2619

-

斩波器的定频调宽工作方式?2024-05-24 2138

-

PLC的CPU工作方式详解2024-06-13 4044

全部0条评论

快来发表一下你的评论吧 !