浅谈有关电迁移潜在机理及其预防的新见解

描述

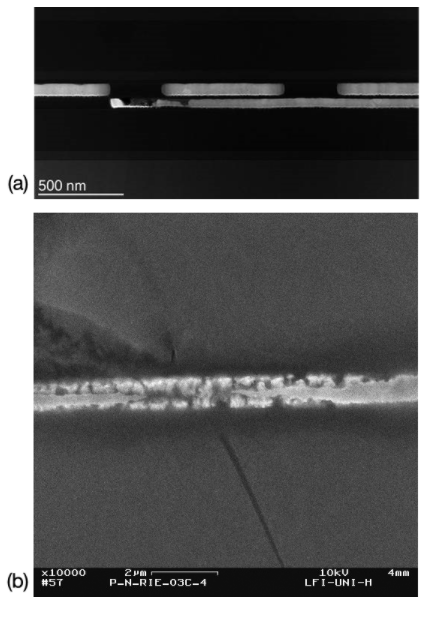

一项创新的测量技术正在为电迁移提供新的见解,电迁移是微电路过早死亡的主要原因。直到最近,这种现象会导致致命的短路并在形成集成电路(IC)晶体管之间电连接的亚微米金属走线内断开连接,只能通过使用破坏性的加速老化过程来导致设备故障来研究这种现象。然后将其切开并对其互连进行目视检查(图1)。

这项新技术有时被称为功率谱密度特征分析,它可以分析流经设备的电流中的细微变化,从而为研究人员提供有关电迁移潜在机理及其预防的新见解。这些见解已经开始帮助IC制造商设计不易过早出现故障的芯片。

图1 a)由于电迁移,两层铜互连的横向SEM图像,下部线条上有空隙。图片由imec提供。b)由铜互连中的电迁移引起的故障的SEM图像。图片由Wikimedia用户Patrick-EmilZörner提供。

深度监听还可用于快速识别刚制造出来的IC,而这些IC在实际发生故障之前会遭受电迁移的困扰。这项新功能为芯片制造商提供了一种比传统老化测试更快,更具成本效益的替代方法,传统老化测试通过在高温下运行多个小时甚至几天来加速新制造IC的缺陷的出现。

电迁移:一个日益严重的问题

电迁移是由于导电电子与扩散金属原子1之间的动量转移而在导体内发生的质量传输。迁移水平与许多因素有关,包括导体内的电流和环境温度。

曾经是100多年前科学家最初观察到的一种实验室好奇心2因此,这种现象已成为半导体工业中越来越具有挑战性的问题。在集成电路的早期,人们对电迁移的了解还不够,甚至在短短的三周运行后就导致一些早期的商用芯片出现故障。那时,制造商通过在芯片顶部生长二氧化硅(即玻璃)薄层,在玻璃顶部沉积一薄层铝,然后对其进行蚀刻以形成电路,从而将IC上的晶体管连接起来。对发生故障的芯片的分析表明,在正确的条件下,铝原子会离开其原始位置,从而在电路走线之间形成空隙或积聚在其他走线上,从而导致开路和短路,从而导致器件发生故障。

对这些故障的进一步研究表明,电迁移活动随温度和电流密度的增加而增加,并受互连迹线的几何形状的影响。这也导致了黑色的方程式,发展3 用于预测IC的寿命公式,和其他工具,允许制造商模式的故障模式,并采用设计实践取得了芯片的金属互连电迁移更容易。

根据他们所学到的知识,该行业开发了一些简单的测试,可以通过使它们经受加速的老化过程来在发货之前对设备进行过早故障筛查,我们将在下一部分中对其进行详细介绍。由于这些发展,电子工业能够制造出使用寿命长达数十年的复杂半导体器件。

尽管如此,电迁移并没有被击败,只是受到了良好的工程实践的控制。随着不断缩小的工艺几何尺寸开始接近纳米区域,IC互连层内的电流密度开始上升,而导电迹线之间的距离缩小,从而为金属迁移创造了更加有利的条件。另外,越来越多地使用铜作为互连材料也增加了挑战。尽管铜的优异电性能使设计人员可以制造更小,更快的芯片,但它也更容易受到导致金属原子从IC内指定位置漂移的作用力的影响。

结果,制造商发现自己试图用一些过时的工具来应对新的挑战。在过去的三十多年中,用于电迁移的标准可靠性测试一直是通过在升高的温度(> 150°C)和电流密度(j> 1MA / cm 2)下运行设备直至其失效来加速老化过程的过程。然后可以使用布莱克方程将芯片在压力条件下失效所需的时间转换为正常条件下的预期寿命。较不严重的加速老化形式(通常称为“老化”)用于筛选在高可靠性应用中使用的IC,以查找导致在装运前造成婴儿死亡的缺陷。

这些加速测试为制造商提供了宝贵的指导,但它们也有许多缺点和盲点。例如,它们的结果有些不可靠,因为它们使用升高的电流和温度,这可能会导致芯片中发生其他类型的过程,而不是正常情况下所经历的过程。这些测试还需要大量时间,并且会对芯片造成破坏。尽管可以对发生故障的IC进行物理检查,以了解发生问题的各种线索(见图1),但再也无法进行可能产生其他类型有价值信息的有源电气测试。此外,越来越多地使用会阻碍电迁移的新材料(例如钴),可能需要对设备进行几个月的测试,甚至还要在更高的温度和电流密度下进行测试。

一种新方法

作为KU Leuven的一名学生,与imec合作为我的博士进行半导体研究,很明显,20世纪测试技术的局限性已成为生产21世纪IC的障碍。从那时起,我和我的同事就开始探索其他测试和分析技术,这些技术可能会提供有关电迁移的新见解。在考虑了几种选择之后,我们开始研究由其输出电流波动产生的IC的电子签名,即使在稳定状态下运行,这些波动也会出现。

聆听芯片内的瀑布

当直流电流流过金属时,由于电子散射,会出现较小的电流波动。这些微小的波动可以作为时间的函数进行测量,并且可以使用傅立叶变换在频域中表示。将该波动描述为频率与幅度的函数的变换,可用于导出波动的功率谱密度(PSD)。

由于尚未完全理解的原因,流经金属的电流似乎会产生PSD签名,该签名在低频范围内遵循1 / f频谱。这种噪声,也称为“粉红色噪声”,通常发生在自然现象中,例如瀑布的轰鸣声。遵循1 / f和1 / f 2 频谱的噪声称为低频噪声,因为与这种噪声相比,低频听起来要比高频听起来更大(与白噪声相反,白噪声中所有频率都是相同的)。

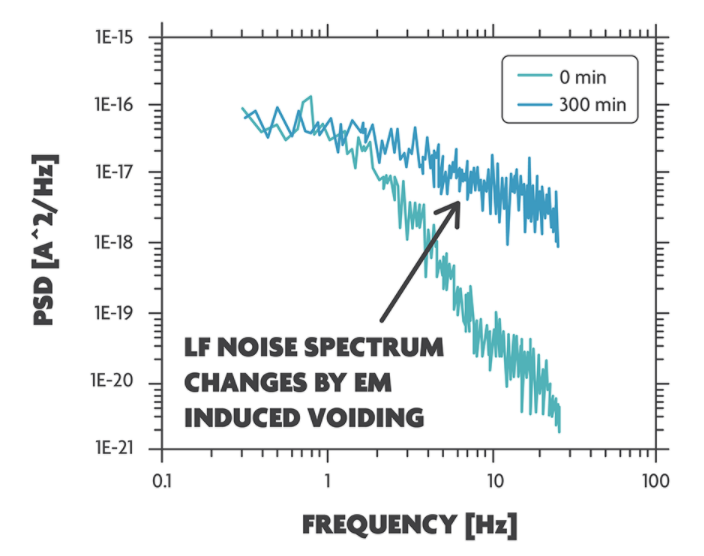

测量芯片中的低频噪声很有趣,因为当发生诸如电迁移的现象时,频率似乎会突然改变(图2)。

图2 经过仅300分钟的热和电应力(旨在刺激电迁移),此处测试的设备的低频噪声特征发生了明显变化。这些变化是由于电迁移在金属通道中产生新的空隙时发生的电流变化而引起的。

新技术产生新见解

尽管imec研究人员已经在相对较短的时间内使用了这项新技术,但他们已经得出了许多令人惊讶的见解,可将其应用于商业半导体设计和制造实践。例如,他们发现,随着金属通道的宽度变小,刺激电迁移所需的活化能阈值也降低,并且当宽度降至30nm以下时显着降低。在对铜互连的研究中,研究人员了解到,这在很大程度上是由于晶粒更紧密的金属结构中多晶的百分比不断增加,从而为电迁移的进行提供了更多的扩散位置。

到目前为止,IC的设计规则一直基于以下假设:由相同材料制成的所有线路后端(BEOL)互连都具有单一激活能量。由于有了这一新见识,未来的设计规则可能将基于针对不同路径宽度的较低的不同能量。

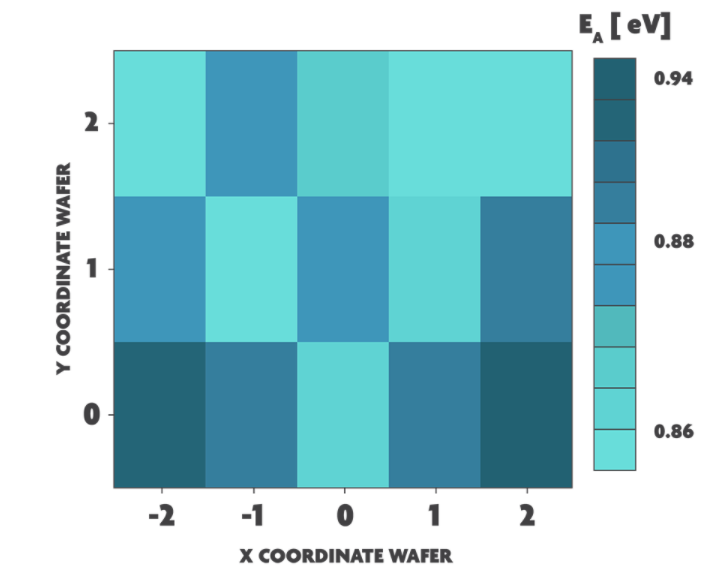

研究人员还了解到,可以在晶圆上的不同芯片之间观察到PSD签名的变化。可以预计,在不久的将来,制造商将能够在生产测试期间使用PSD签名分析来创建晶圆图,以显示每个芯片的预期寿命-这是标准方法无法实现的。

图3 晶片图显示了晶片上每个芯片的激活能量(通过测量低频噪声定义)的变化。图片由imec提供。

使用新测试的第三项研究领域是测试钌的电迁移可靠性,该材料被认为是BEOL中铜通道的替代材料。由于钌具有抗电迁移的能力,因此常规测试将花费很长时间,并且需要更高的温度和电流密度。相反,PSD分析可以相当快地确定新材料的活化能。这项研究还产生了许多有关不同类型的势垒如何有效减少或消除电迁移的新信息。例如,钌衬里似乎对铜互连的耐电迁移性具有积极作用,向籽晶层中添加锰也是如此。

除了可以在故障发生之前进行预测外,该技术是非破坏性的,并且比传统测试花费的时间要少得多。此外,测试产生的数据可提供对电迁移的性质和发生情况的更深入的了解。由于PSD签名分析是在设备的额定温度范围内进行的,因此观察到的现象也很有可能与实际使用中的芯片所产生的现象相同。

准备服务

PSD签名分析已证明其作为半导体研究工具的价值,并有望成为制造商的宝贵工具。Imec的合作伙伴公司和大学研究小组已经在探索如何使用它来更深入地了解电迁移的潜在机制,这些机制可用来更好地防止新材料和现有材料的故障。

对于芯片制造商而言,该方法对于研究和生产都非常重要。在生产中,它通过对单个芯片的电迁移电阻提供更深的基础见解和预测,对现有方法进行了补充。例如,上一节中讨论的晶片图可用于查明晶片中每个器件中电迁移活化能和缺陷浓度的变化。这将有可能根据更高的活化能和/或更低的缺陷集中度,根据成品的可靠性对成品进行分类,而不是传统老化测试所提供的简单合格测试。使用寿命更长的设备可以针对航空航天,医疗或汽车系统等关键应用以高价出售。

Sofie Beyne是imec和KU Leuven的博士学位学生,研究作为REMO团队一部分的纳米互连中的电迁移。

编辑:hfy

-

浅谈电气火灾的分析和预防2024-03-12 1531

-

浅谈因电迁移引发的半导体失效2024-02-28 2582

-

关于连接的问答:有关亚洲更快、更好地部署 Wi-Fi 的见解2022-12-26 3878

-

变频器损伤电机的机理及预防方法2022-09-09 1193

-

什么是静电放电?什么是电迁移?2021-06-17 1490

-

离子迁移对印刷线路板绝缘性能的影响2018-08-23 3266

-

浅谈认知无线电关键技术及其在煤矿通信中的应用2013-03-16 2990

-

有关MTF的深刻见解!!!(含附件)2013-01-08 3565

-

虚焊现象的发生及其预防2012-08-08 2624

-

电容的失效模式和失效机理2011-12-03 9285

-

电子封装微互连中的电迁移2011-10-26 1037

-

浅谈我国光伏产业快速发展潜在的问题2010-04-19 908

-

浅谈WiMax技术及其应用前景2009-05-21 1182

-

数字电视及其测量浅谈2008-11-27 1579

全部0条评论

快来发表一下你的评论吧 !