接地共面波导射频馈线的优化方案解析

描述

Arira Design的信号完整性小组被要求重新设计现有的5GHz接地共面波导RF馈线,以提高客户板上Wi-Fi子系统的性能。测量表明,馈线阻抗的阻抗约为38欧姆。

在进行仿真之前,原始设计发现了几个问题,包括:

- 无法考虑阻焊层对走线阻抗的影响

- 在走线阻抗计算中未考虑PCB回蚀

- 附近的非参考地平面中的切口不正确

对现有的馈线进行了仿真,然后根据仿真结果改进了共面几何形状,以满足50欧姆的阻抗要求。结果,该客户报告说,使用新的PCB可以大大改善Wi-Fi性能。

本文讨论了初始PCB设计的共面几何形状,上述三项的影响以及最终的共面几何形状。显示了不同共面配置的电场图,以说明接地共面设计可能发生的有意和无意耦合(假设读者熟悉共面波导或CPW和接地共面波导的基本结构,或者GCPW)。

接地共面波导

由于现代电路板上Wi-Fi和蓝牙集成的普遍性,接地共面波导在PCB设计中正变得越来越普遍。与传统的微带传输线相比,GCPW的一些优势如下:

更低的损耗:更多的电场线穿过空气,而不是流过有损的PCB材料。这样可以在运行于5GHz的PCB设计中使用价格更便宜的FR-4。

隔离:与微带相比,GCPW线提供了更多的隔离,因为磁场线的约束更加严格。

灵活的几何形状:GCPW阻抗主要由走线和共面接地结构之间的间隙控制。与微带传输线相比,这在走线宽度上具有更大的灵活性。

较低的铜表面粗糙度损失:微带线中的电流倾向于沿着走线的底部集中,走线的底部是最粗糙的铜(以增强与电介质的附着力)。正确设计的GCPW传输线倾向于使电流集中在走线的边缘,在走线的表面较光滑。

出色的匹配组件放置:大多数蓝牙或Wi-Fi RF馈线需要串联和/或并联匹配组件。由于GCPW的接地线紧邻走线,因此可以将并联组件直接安装在走线和共面接地之间,从而消除了与过孔相关的寄生现象。

可使用许多工具来计算GCPW结构的阻抗,但是Internet上可用的免费工具通常会限制可分析结构的类型。通常可以计算出基本结构,但近乎铜结构的效果通常需要进行EM仿真才能正确建模。

PCB说明

所考虑的PCB是使用FR4电介质,标称Dk(介电常数)为4.2的消费类产品的高容量四层板。板的厚度约为45密耳。GCPW位于第1层,而接地参考岛位于第3层。第2层是接地平面层。第3层是电源平面层,也具有GCPW的接地参考岛,第4层是信号层。直径为8密耳的通孔将第1层接地层与第3层参考平面和第2层上的主接地层连接起来。

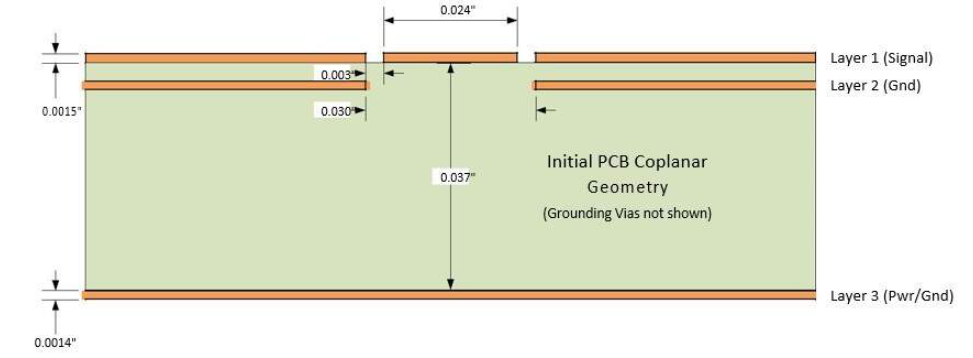

初始PCB上的接地共面波导几何形状是使用Internet上提供的免费软件传输线计算工具设计的。GCPW的走线宽度约为24密耳。选择该走线宽度以匹配Wi-Fi模块和天线连接器的引脚尺寸。电镀后的迹线厚度约为1.5密耳。共面走线位于地面参考平面上方约37密耳处。

(资料来源:Arira Design)

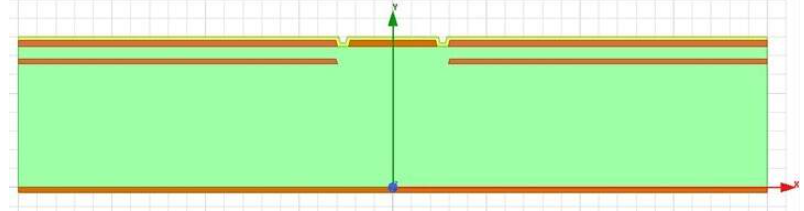

通过此输入,我们的客户最初使用的传输线计算工具确定共面间隙为3密耳。第2层接地平面上有一个切口。PCB设计人员将此切口的宽度与第1层上共面接地浮雕的宽度相匹配,以使第2层平面上的切口的宽度为30密耳,如上图所示。

初步分析与模拟

当检查用于在初始板上设计共面几何形状的传输线计算器时,发现该工具并未解决板上存在阻焊层的问题。同样,它也没有考虑到PCB回蚀。对于位于PCB外层的边缘耦合结构,阻焊层和PCB回蚀会极大地影响走线阻抗,尤其是在结构表现出强耦合的情况下。显然,如果这些因素未包括在共面阻抗分析中,那么计算的准确性就会受到影响。同样清楚的是,靠近共面走线的第2层接地平面的存在也会影响走线阻抗。

考虑到这一点,进行了一系列模拟,以量化阻焊层,回蚀以及第2层接地平面与共面走线的紧密距离的影响。Ansoft的Q2D场求解器工具用于此建模。仿真及其结果如下所示:

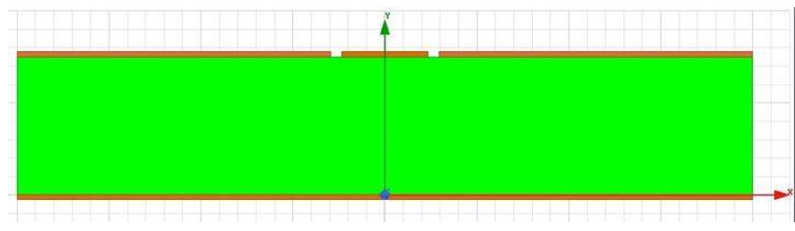

没有阻焊层,没有回蚀,没有L2接地层:Q2D仿真报告的阻抗为43.0欧姆。另一款商用2D场求解器LINPAR报告的阻抗为42.7欧姆,与Q2D模拟显示出极好的一致性。这是免费软件阻抗计算器分析并错误地报告阻抗为50欧姆的结构。

没有阻焊层,没有蚀刻层,没有L2接地层(来源:Arira Design)

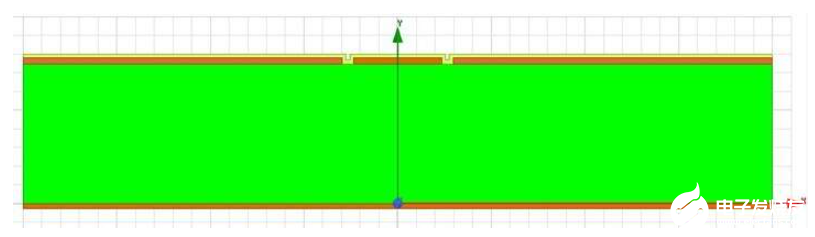

存在阻焊层,无回蚀,无L2接地平面:对于此仿真,将阻焊层添加到了模型中。Q2D仿真报告的阻抗为37.9欧姆。阻焊层的存在增加了共面走线和共面接地层之间的耦合,从而大大降低了阻抗。

存在阻焊层,无蚀刻,无L2接地层(来源:Arira Design)

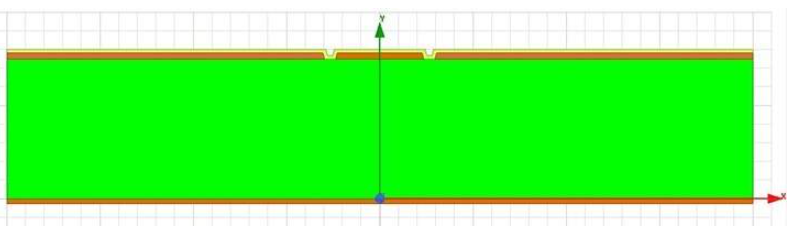

存在阻焊层,存在回蚀层,不存在L2接地平面:此模拟将回蚀添加到了共面走线和共面地上。Q2D仿真报告的阻抗为39.9欧姆。回蚀减少了共面走线和共面接地层之间的耦合,与以前的情况相比,这稍微增加了阻抗。

存在阻焊层,存在回蚀层,无L2接地平面(来源:Arira Design)

存在阻焊层,存在Etchback层,存在L2接地层:这是在原始PCB设计中实现的结构。Q2D仿真报告的阻抗为36.5欧姆。靠近共面走线的接地层的存在会增加对地的耦合,从而降低阻抗。36.5欧姆的仿真结果与38欧姆的初始PCB设计上的走线阻抗测量值接近。

存在阻焊层,存在回蚀层,存在L2地平面(来源:Arira Design)

阻抗优化

为了将GCPW结构的阻抗优化为50欧姆,策略是首先确定(使用模拟)满足50欧姆要求的共面几何形状。然后,一旦确定了几何形状,就将第2层的接地平面添加到模拟中,并使用模拟对第2层接地平面切口的宽度进行优化。

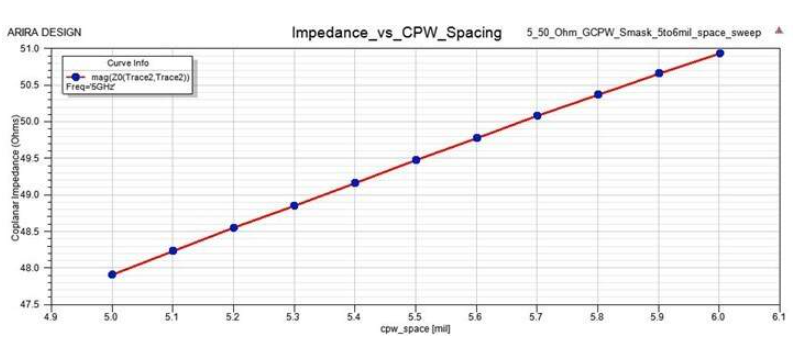

步骤1:在阻抗优化过程的第一步中,通过连续进行共面间隙的模拟扫描,将第1层上共面间隙的宽度优化为50欧姆。发现最佳间隙为5.7密耳,这导致模拟阻抗为50.07欧姆。通过仿真确定的最佳间隙几乎是原始PCB设计间隙宽度的两倍。模拟的共面阻抗与共面间隙的关系图如下所示。

阻抗与CPW间距(来源:Arira Design)

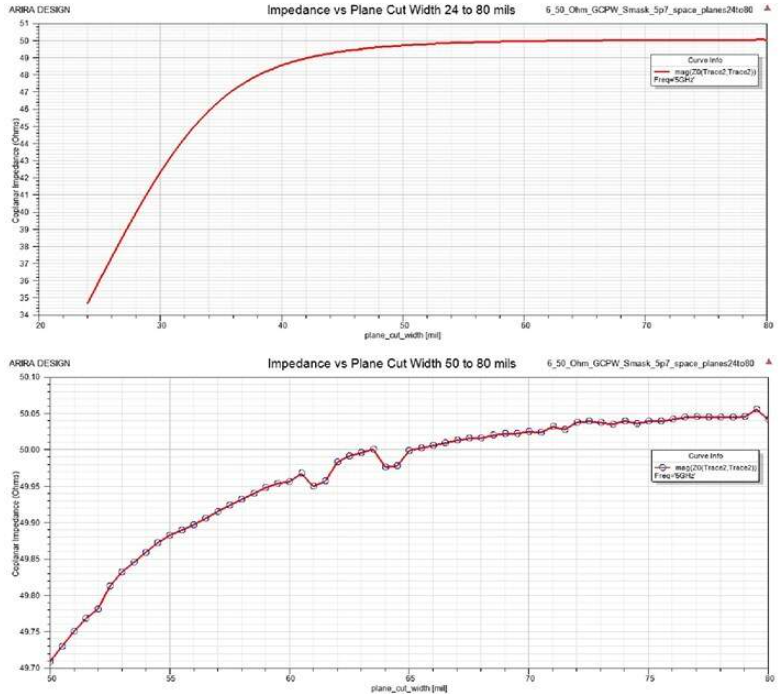

步骤2:在第二个优化步骤中,将共面间隙固定为5.7密耳,将第2层接地平面添加到模型中,并将第2层接地平面上的切口宽度从24密耳扫到80密耳。根据以前的经验,我们知道与第1层总共面间隙(30 mils)相似的第2层平面切口宽度会导致阻抗过低,但是我们想模拟小于预期解决方案范围的宽度,以便了解阻抗与接地宽度的关系。

阻抗与接地切口宽度的两幅图如下所示。第一个图显示了从24到80密耳扫过的接地平面切口宽度,而第二个图则将焦点缩小到50到80密耳范围内的接地切口宽度。

阻抗与平面切割宽度的关系,顶部24至80密耳,底部50至80密耳(来源:Arira Design)

从这些图中可以看出,当不存在第2层接地层时,阻抗将收敛到在优化过程的第一步中计算出的50.07欧姆值。从这些图中可以看到,第二层接地平面切口宽度大于58密耳并不会显着移动阻抗,因此,这就是为新PCB设计选择的接地平面切口的大小。所得阻抗为49.9欧姆。

电场图

下面显示了不同接地平面切口宽度以及原始PCB设计的仿真电场图。这些电场图用于确认结构是否正确设计并发现任何问题区域。例如,在以较小宽度的第2层接地平面切口为特色的仿真中,可以看到共面走线的电场与第2层接地平面牢固耦合,从而降低了走线的阻抗。

对于每种配置,将显示两个图。电场强度图显示电介质(FR4,阻焊层和走线上方的空气)中的电场图,并用颜色编码以指示电场强度。矢量图以矢量格式显示电场。这也用颜色编码以反映场强。

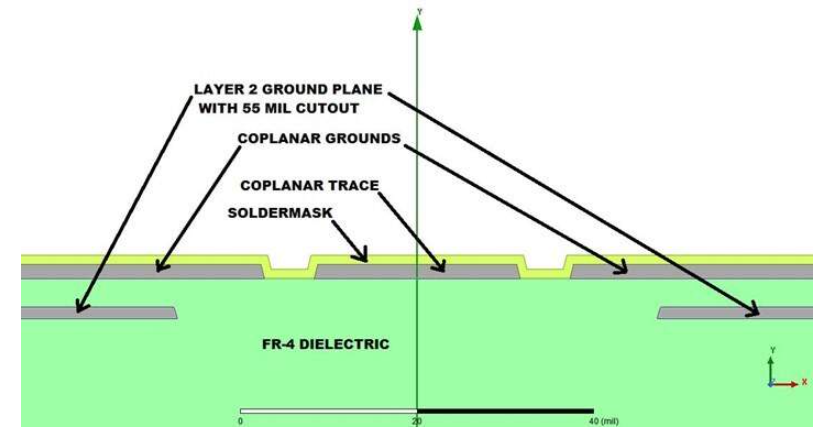

下图显示了在Ansoft Q2D中建模的GCPW,其中标记了组成结构。查看电场图时,可使用此图获取方位。该图或电场图中未显示第3层的返回接地平面。

以Ansoft Q2D建模的GCPW(来源:Arira Design)

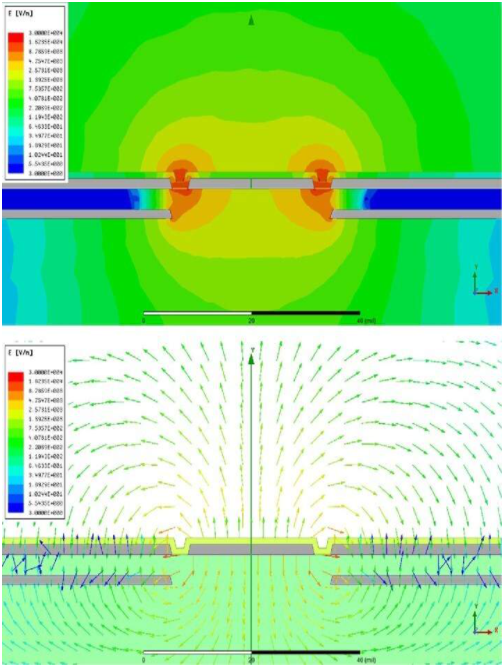

原始设计:3 mil共面间隙,30 mil 2层接地平面间隙:下图显示了具有3 mil共面间隙和2层接地平面中30 mil宽间隙的原始设计的电场。从共面走线到第2层接地层的耦合非常强。这种强耦合以及太小的共面间隙导致模拟的36.5欧姆共面阻抗。

原始设计:3 mil共面间隙,30 mil 2层地平面间隙(来源:Arira Design)

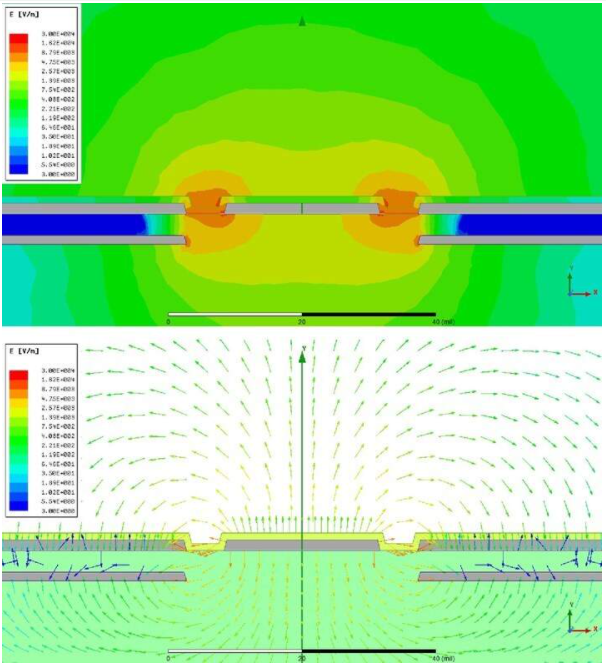

不正确的设计:5.7 mil共面间隙,35 mil第2层接地平面间隙:下图显示了具有阻抗优化的5.7 mil共面间隙但在2层接地平面中有35 mil宽间隙的设计的电场。这说明了(相对常见的)情况,设计人员使用了正确的共面间隙,但错误地将第2层接地间隙实现为与总共面接地间隙相同的宽度(35密耳)。如我们所见,从共面走线到第2层接地层的耦合相当强,这导致模拟的共面阻抗为46.5欧姆。

设计不正确:共面间隙为570万密耳,第2层地平面间隙为3500万密耳(来源:Arira Design)

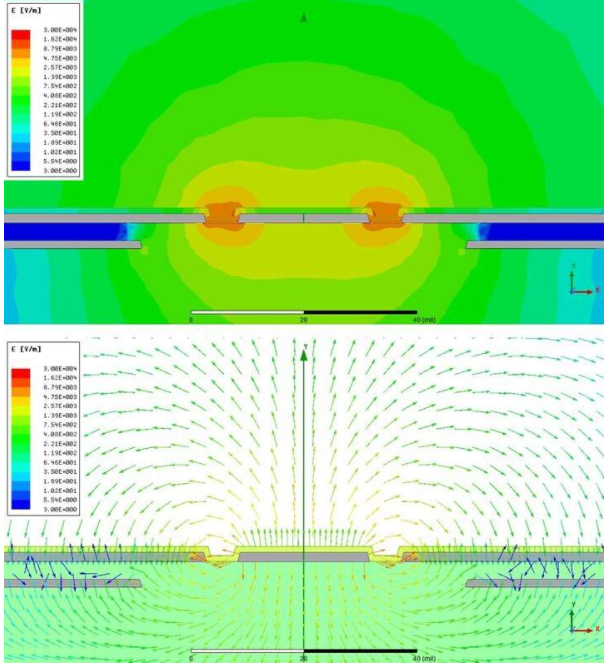

优化设计:共面间隙为570密耳,第2层接地层间隙为58密耳:下图显示了设计的电场,其中第2层接地面阻抗优化了570密耳,共面间隙为58密耳。L2接地平面间隙优化扫描显示,第2层接地平面中的间隙大于58 mils不会显着影响阻抗。因此,接地平面切口设置为58密耳。

在这种配置中,与第2层接地层的耦合很小,模拟阻抗为49.9欧姆。

优化设计:共面间隙为570万密耳,第2层地平面间隙为5800万密耳(来源:Arira Design)

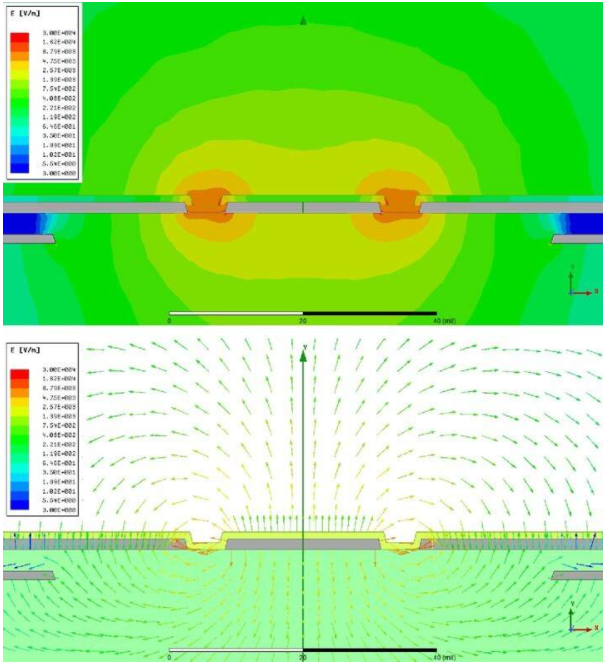

大接地平面切口:570万共面间隙,第7层第2层接地间隙:下图显示了设计中的电场,其中阻抗优化了5.7密共面间隙,第2层中有75 mil宽间隙地平面。该图表明,如果将第2层接地平面的间隙扩大到58密耳以上,则L2接地平面的耦合不会显着降低。但是,较大的接地平面间隙可能会干扰PCB上的其他布线。

在这种配置中,与第2层接地层的耦合非常低,模拟阻抗为50.0欧姆。

较大的接地平面切口:共面间隙为570万,第二层接地间隙为7500万(资料来源:Arira Design)

结论

免费软件阻抗计算工具通常功能有限。它们可能允许也可能不允许您为回蚀或阻焊膜建模,并且它们通常不适合模拟多层几何中各层之间的现场相互作用。

对于多层堆叠上的某些接地共面配置,共面接地参考平面可能是共面走线下方的两个或更多PCB层。这需要在接地平面参考层上方的那些层上的共面走线下方设置铜保留区域。试图直观地估计该铜保留区域的最佳尺寸是非常困难的。低估保留区的大小可能会导致无法预料的EM场相互作用,而高估保留区的大小可能会导致PCB设计上不必要的宝贵布线面积损失。

一些设计人员使用众多可用的传输线工具之一来“足够接近”地获取走线的阻抗,然后他们依靠自己的晶圆厂使用商用阻抗计算器(例如Polar)来计算正确的几何形状和拨号方式。蚀刻电路板时的阻抗。不幸的是,这种方法无法解决PCB结构之间意外耦合的问题,因为晶圆厂在电路板制造过程中并未使用PCB上的实际走线来测量阻抗。取而代之的是,晶圆厂使用测试蚀刻片,上面刻有设计者的迹线几何形状。这些测试试样不会将无意的耦合复制到PCB设计上发生的附近结构上。因此,晶圆厂

如果您要在板上设计接地共面波导,那么您将希望在第一时间就将其正确设置。即使天线馈线存在严重的失配,大多数Wi-Fi和Bluetooth设计在板载过程中似乎都可以正常工作。但是,糟糕的设计几乎总是会在您宣布胜利后在范围测试或数据完整性测试中广为人知。

编辑:hfy

-

优化PCB设计中的射频馈线2024-01-16 1219

-

共面波导传输线特性分析及工程应用2023-01-30 6820

-

高频PCB设计:影响射频信号性能的因素2021-05-14 7074

-

射频PCB的共面波导设计2020-10-26 11656

-

普通微带线和共面波导结构有哪些优缺点2020-10-10 7819

-

微带线和共面波导的界限是什么?2019-12-18 7884

-

怎么设计微带与共面波导CPWG?2019-08-21 8131

-

一种DC-40GHz带状线到共面波导过渡设计2019-02-04 9573

-

PCB材料对微带线和接地共面波导电路有着怎样的影响2019-01-08 2614

-

由共面波导馈电的单极子双频天线设计与特点介绍2018-12-26 13075

-

射频/微波PCB的信号注入设计与优化2018-09-17 1926

-

基于共面波导的NVNA相位参考设计及应用_徐清华2017-01-19 842

-

射频/微波PCB的信号注入与优化方法2016-08-13 2784

-

ADS仿真共面波导问题2013-11-05 9025

全部0条评论

快来发表一下你的评论吧 !