一文解析并行通信源同步技术

电子说

描述

我们都知道源同步方式的典型代表是DDRx信号,下面就来介绍源同步方式是怎样改善系统同步的先天不足的。

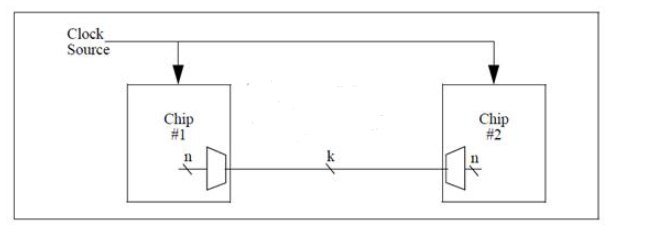

源同步要解决的第一个问题是减少在芯片之间传输数据所需的I/O引脚数量。这通过将芯片#1的输出处的n位数据复用到k位互连(k 《n),然后将芯片#2的输入上的互连的k位解复用到n位内部数据路径上来实现,如下图所示。所得到的系统只需要每个芯片上的k个I/O引脚,而不需要先前的n个引脚。

当然,虽然引脚数量要求已经通过k:n的比率降低,但是参考时钟的所需频率已经增加了这个比率的倒数。由于噪声,电磁干扰(EMI)和功耗问题,系统设计人员通常不喜欢在系统内分配高速参考时钟。通常,分配较低频率的时钟,并且使用芯片中的PLL将该参考时钟乘以可用频率,但所产生的时钟相位的变化以及数据传输的频率越高,往往会加剧并行数据总线的时序问题。

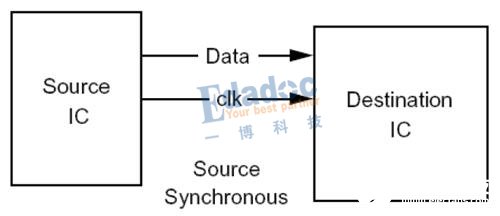

源同步的第二个法宝就是在两个芯片之间的数据通路中增加了一个高速时钟,如下图所示。假设该时钟源提供的时钟频率略低于在芯片互连上对数据进行触发的时钟频率,每个芯片都使用PLL来产生这个频率倍数的时钟,所得到的时钟用于启动和捕获相应芯片中的数据。芯片#1中用于从该芯片启动数据的PLL的输出时钟也是该芯片的输出,芯片#2使用该时钟来捕获数据,这种方法称为时钟转发。

时钟转发的优点是用于在芯片#1上启动数据的高速时钟可用于芯片#2作为捕获数据的参考。这样之前通过时钟分配网络驱动两个芯片的延迟的变化在时序分析中就不需要考虑了,只有时钟路径和数据位之间的延迟变化是相关的。 虽然制程,电压和温度导致的这些路径之间的变化在一定程度上相互影响,但接口的时序分析需要的余量较少,因此建立和保持时间更容易满足。

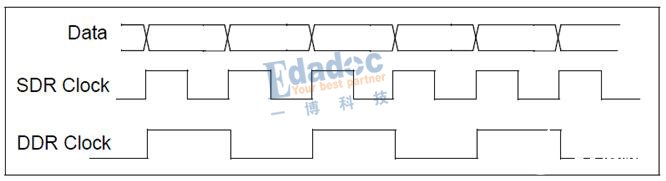

我们还是来看看典型的例子吧,图中所示的时钟可以是单数据速率(SDR)或双倍数据速率(DDR)的时钟,如下图所示。SDR就是接收芯片在SDR时钟的每个上升沿(或每个下降沿)捕获数据; 而DDR则是接收芯片捕获DDR时钟的每个边沿(上升沿和下降沿)的数据。

无论时钟是SDR还是DDR时钟,接收芯片都使用该时钟直接捕获数据。 该芯片还使用参考时钟以相同的频率生成内部系统时钟,这些时钟是中间同步的。 虽然频率相同(鉴于它们共享共同的频率参考),但是时钟之间的相位关系是未知的,并且可能由于PVT变化而变化。 因此,接收芯片通常将接收到的数据从接口时钟域重新定时到内部芯片时钟的时钟域。 FIFO用于执行此重定时功能, 期望最小化由接口时钟计时的触发器的数量,以便最小化时钟分配网络中的延迟,否则时钟问题将会加剧。

编辑:hfy

-

labview和三菱FXPLC编程口通信源码2013-12-17 26606

-

并行通信源的同步方式2019-07-23 936

-

wifi通信源码,可以和电脑或者手机通信2020-06-02 911

-

一种delphi串行通信源码教程2021-07-01 1887

-

单片机串口通信与同步异步通信的相关资料分享2021-12-08 848

-

一文搞懂ARM的串行通信与并行通信2022-04-27 6188

-

一种并行帧同步设计方案的提出、设计与应用2010-07-05 894

-

通信原理_模拟信号数字化与信源压缩编码2016-06-23 942

-

串口通信源程序2016-11-05 676

-

信源及信源熵2017-11-24 970

-

一文读懂UART/RS232协议学习_串行和并行通信介绍2018-05-22 7261

-

一文弄懂信源编码是什么2018-11-15 23780

-

基于STM32+LoRa的点对点通信源代码2021-09-09 2002

-

AN4666_运用GPIO和DMA实现并行同步通信2022-11-21 679

-

一文详解串行、并行、同步、异步2023-03-15 14371

全部0条评论

快来发表一下你的评论吧 !