浅谈高速串行信号的自同步通信方式

描述

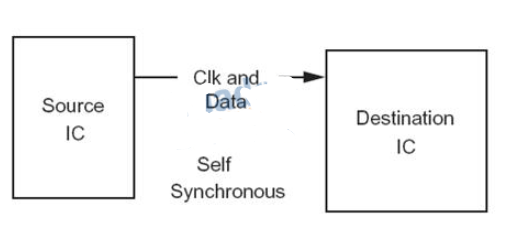

高速串行信号与并行信号相比,最主要的就是通信方式的改进,这种通信方式又叫自同步方式,也即两块芯片之间通信,其中发送芯片产生的数据流同时包括数据和时钟信息,如下图所示。

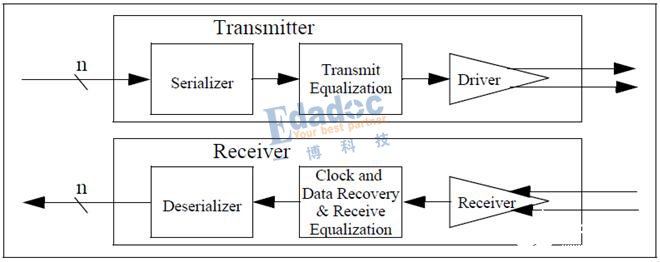

要实现上图所示的通信,在芯片内部还有更加详细的一些要求及模块来操作,具体实现可以参考下图所示模块框图。

这些最主要的模块包括串行器(也有叫串化器)、时钟数据恢复(CDR)、解串器以及均衡器等。这样的设备与源同步接口不同,因为接收机设备包含时钟和数据恢复(CDR)电路,其基于信号的跳变沿来动态地确定数据信号的最佳采样点。 换句话说,从数据中直接提取时钟信息,而不是依赖于单独的时钟。本篇我们主要来简单介绍前面三种必要的模块,均衡器会在后续的内容中介绍。

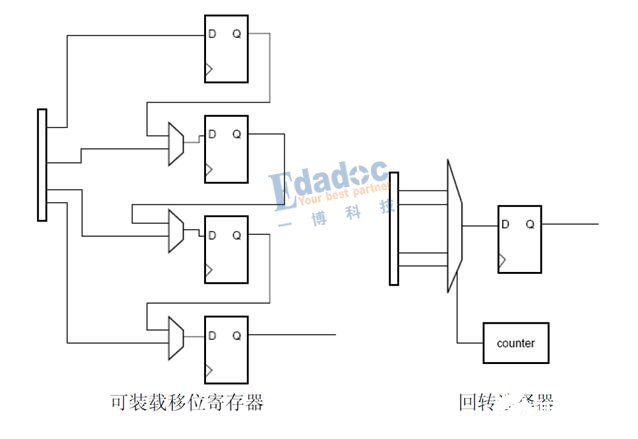

串行器要实现的功能就是并串转换,简单来说就是将原本并行的数据转换成串行的数据。目前有两种主要的并串转换方式——可装载移位寄存器和回转选择器。这些方法的简单逻辑如下图所示。

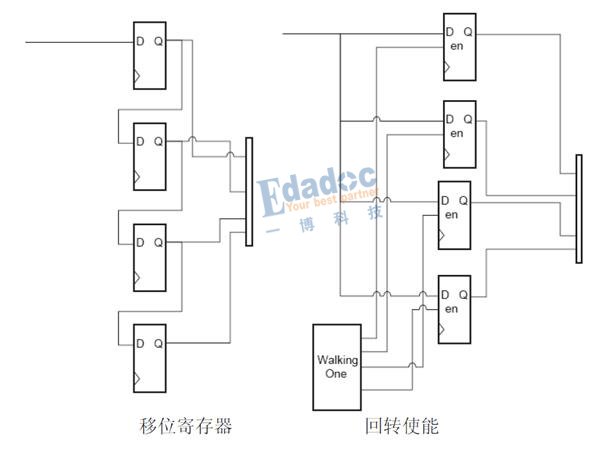

解串器的功能正好和串行器的功能及步骤相反,那就是将串行的信号又重新转换成并行信号,又叫串并转换,下面是简单的逻辑图。

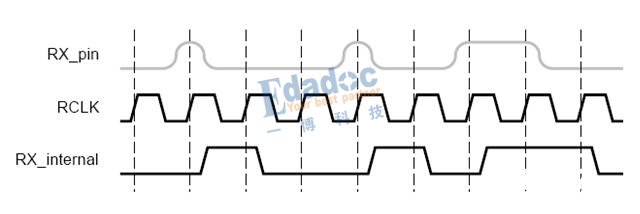

时钟数据恢复(CDR)顾名思义就是将数据流里面的数据和时钟在接收端恢复出来,说起来感觉很简单的样子,但实际上如下图所示时钟恢复过程无法产生一个共用时钟或者同数据一起发送的时钟。作为替代,由锁相环(PLL)合成出一个与输入串行信号的时钟频率一致的时钟,也即PLL能根据参考时钟和输入信号来产生锁定于输入信号的新时钟,所以PLL对于Serdes的接收也是至关重要的。

这就是我们的串行信号,呈现出来的确实是比较简单,无非就是几对差分线路,但内部的操作却非常复杂。虽然简化了PCB设计,但对芯片的设计挑战巨大,因为有更多的模块集成在芯片内部了,这个对于我们PCB这块来说是看不到的,相当于一个黑盒子,典型的少林寺扫地高僧,简直深藏不露啊。

编辑:hfy

-

单片机中的串口通讯串行同步通信与串行异步通信2026-01-15 262

-

并行与串行的基本通信方式2025-11-24 332

-

串行通信和并行通信的区别是什么2025-07-22 3219

-

高速串行通信协议详解2024-05-16 2294

-

串行通信调幅和调频方式2023-06-29 2428

-

同步通信与异步通信的方式解析2022-02-17 924

-

同步通信方式与异步通信方式2021-12-20 1359

-

浅析高速串行自同步方式2019-07-23 1165

-

如何利用SPI模块进行双DSP同步串行通信设计2019-02-06 9630

-

基于MSP430F2的SPI串行同步通信2017-09-21 932

-

高速串行自同步方式介绍及原理技术2017-09-18 987

-

自驱动方式是最简单的同步整流2010-10-16 10003

-

同步通信,同步通信原理是什么2010-03-17 6546

-

串行同步通信的应用2009-10-17 2643

全部0条评论

快来发表一下你的评论吧 !