空间级开关稳压器选择无源器件的技巧分享

描述

随着航天航空电子设备中越来越多地使用低压,高电流负载(例如FPGA),工程师越来越需要设计开关模式调节器来生成电源轨。之前,我描述了降压拓扑如何执行dc-dc转换,以及从供应商选择空间级设备时要考虑的标准。大多数合格部件都集成了开关和低端FET,但需要一个外部电感器以及输入和输出电容器。这些无源器件的选择非常重要,因为它们决定了转换的质量,即输入和输出纹波,负载调节以及对单事件效应(SEE)的响应。

电源设计从其本质上讲就充满了折衷和折衷,例如成本,尺寸,性能和可靠性。但是,还存在优化和减小储能无源元件的尺寸和质量的范围。

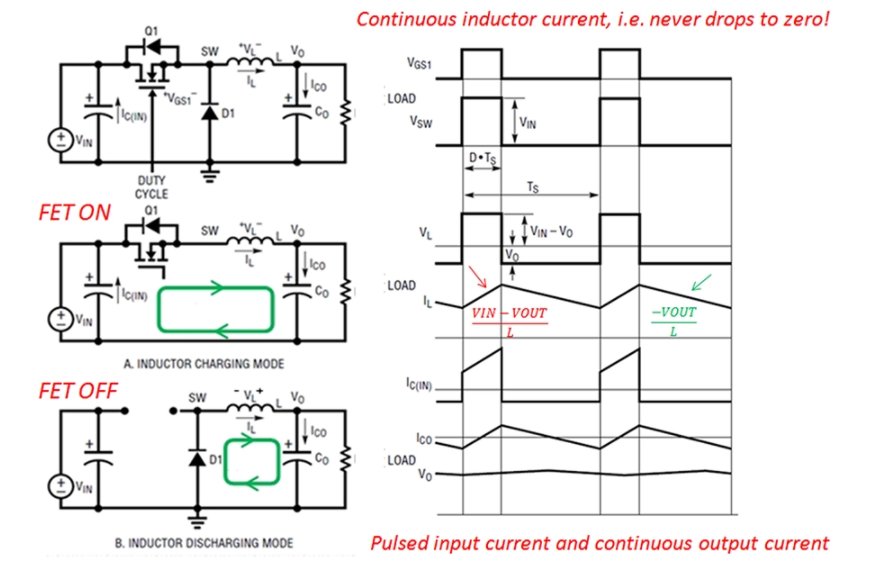

开关DC-DC通过控制通态和关态的占空比,基于流入和流出DC-DC的能量来调节输出电压。当开关导通时,能量从输入源流入转换器,在降压的情况下,其中一些以磁能(0.5 * LI 2)的形式存储在电感器中,而另一些则直接传递到输出中(正向)拓扑)。类似地,在关闭间隔期间,能量从转换器传递到负载。为了降压,它来自电感器,该电感器先前在FET导通时存储在该电感器中。

在导通时间内添加到电感的能量始终等于开关断开时传递到负载的能量,即,电感在每个周期结束时的电流和能量与开始时完全相同。稳态的定义!

图1该图显示了降压调节器的开关周期。

例如,假设开关频率为500 kHz,输入为+ 5.5V,负载电压为+ 0.95V,负载电流为18 A,转换效率为90%,则得到的输入和输出功率为19和17.1W。在每个开关周期内汲取的源能量为38 µJ,FET关断时的能量输出为34.2 µJ。在500 kHz的频率下,调节器处理的总能量为17.1 J / s或按定义为17.1W。

当我们向电感器添加能量时,流经电感器的电流会线性上升。当我们去除能量时,电流会下降,从而导致观察到交流电流纹波。以类似的方式,当我们向电容器添加能量时,电容器两端的电压线性上升。当我们除去能量时,电压下降,从而导致观察到交流电压纹波。开关动作不断地增加和消除能量,从而产生流经电感器的电流纹波和电容器两端的电压纹波。对于这两者,都有相对于其直流电平的最大可容忍交流变化量的准则。

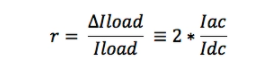

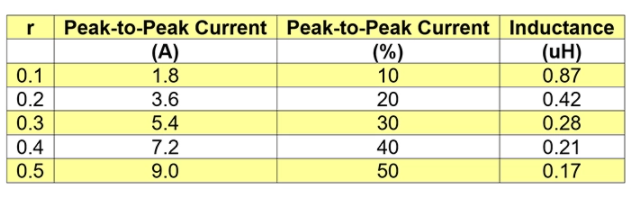

对于降压稳压器,当开关FET导通时,电感器将输入能量存储在其磁场中,而当高端晶体管关断时,电感器将其传递到负载。电感值的选择基于要传递给负载的电流纹波的大小,由几何比r定义:

其中Iload是平均电感器电流,ΔIload是电流摆幅,Iac和Idc分别是电感器电流的ac和dc值。亨利中与r相关的最终电感可以通过以下公式计算:

其中fsw是赫兹的开关频率。

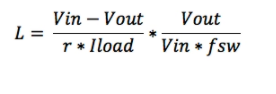

例如,要在18 A电流下产生+ 0.95V电压轨,下表列出了以安培为单位的绝对峰峰值电感电流纹波和Iload的百分比,以及作为r的函数得出的电感:

表1电感纹波和电感的计算

电感的值与负载电流和开关频率成反比,而其物理尺寸和质量与Iload成正比。

完全集成的空间级降压稳压器可提供总体上较小的外形尺寸,并且易于设计,同时还必须添加外部磁和无源元件,从而使设计人员可以更好地控制电流纹波的电平,从而控制电压变化传递给负载。

图2比较完全集成和非集成的空间级开关稳压器。

大电感会产生较小的电流纹波,从而降低负载中的电压波动。较大的电感(由于其自然会抵抗电流变化的趋势)会减慢调节器的瞬态响应,并由于较大的固有dc电阻而增加功率损耗。较小的电感可提高调节速度,但会增加输出纹波量,并有将电感驱动至饱和的风险。重要的是,不要超过电感的均方根电流和饱和电流额定值,后者要大于计算出的峰值。磁体的物理尺寸必须与其能量处理能力相匹配,并且需要更大的磁芯来处理更高的功率。另请检查电感的容差,对于某些供应商,其容差可能会高达30%,

电感器电流纹波表现为输出电压的变化,输出电容的功能之一是减少负载看到的纹波量。电容器ESR和ESL是确定与电感器电流相关的输出电压纹波的重要参数。

电容器自然可以抵抗交流电的变化。电压,一旦充电,就有保持电压的趋势,尤其是在直流电之上存在纹波的情况下。如果电容器尺寸适当,将太慢而无法跟上由于纹波引起的电压波动,因此它们会被滤除。

当FET关断时,输入与输出断开,但是,负载始终需要连续的能量流。在这段时间内,输出电容还必须存储足够的电荷以为负载提供输出:当开关断开时,电感电流在为负载供电时会减小,而输出电容则可以缓冲这种电流变化,因此负载的电压几乎恒定。

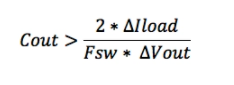

输出电容还决定了调节器如何响应负载电流的大变化。它的大小必须适当以在DC-DC无法且直到DC-DC的反馈控制回路能够响应之前提供负载。下面的公式指定了完成此操作所需的最小输出电容:

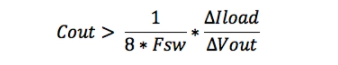

而以下公式可计算满足目标输出电压纹波要求的最小输出电容:

由电感器和输出电容形成的LC滤波器去除了开关波形的ac分量,以输出平均(dc)电压。对于降压稳压器,输出电容通过以负载电压为中心的纹波反复充电和放电。图1中的迹线Ico绘制了流入输出电容的连续电流。

通常,并联使用各种不同的电容器,以最小化等效串联电阻(ESR)和等效串联电感(ESL)对输出纹波和均流的影响,以确保可靠的工作。根据零件的额定纹波电流,工作电压和寄生虫来选择零件。

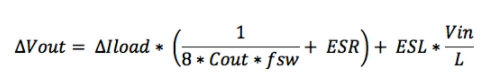

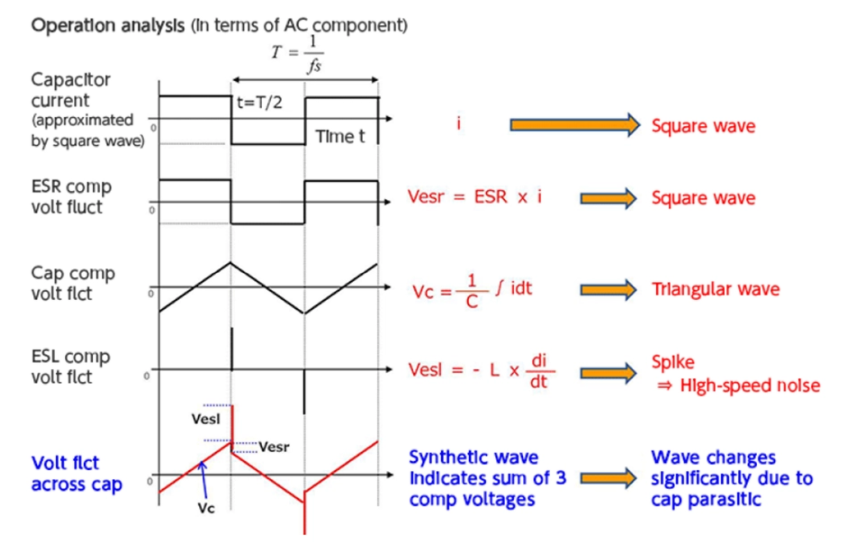

图3绘制了由ESR,ESL和电容产生的纹波电压贡献。ESR的贡献是电阻*电流,电容分量是电流和时间的积分,产生三角波,ESL分量可以表示为导数,在每个开关瞬间都会产生瞬时尖峰,从而产生高频脉冲-像噪音。电容器两端的总电压波动包括以下三个成分的总和:

在输出端看到的峰峰值电压纹波与电容和开关频率成反比,但与负载电流,ESR和ESL成正比。

图3此操作分析显示了ESR,ESL和电容对纹波电压的影响。

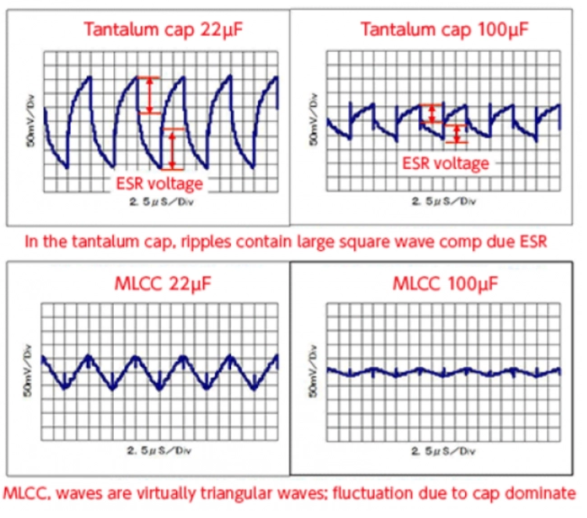

图4比较了从钽电容和多层陶瓷电容器(MLCC)测得的纹波电压。MLCC具有较低的固有ESR,并且增加电容量可进一步降低纹波。

图4这些图显示了电容器类型和电容对纹波电压的影响。

输入电容可将在DC-DC开关处看到的源纹波电压降低到大容量电容器可以处理的水平,而不会影响大容量电容器的ESR耗散。对于降压稳压器,当FET导通并导通时,其输入电流的ac部分由电容提供。当高端开关断开时,输入电容充电,图1中的迹线Ic(IN)绘制出具有高di / dt和峰峰值幅度的不连续梯形波形。该源无法产生如此迅速变化的脉动电流。

大容量输入电容用于最小化电源电压偏差,以确保负载瞬变期间的稳定输出。电容越高,扰动越小,它与负载电流的变化成正比。

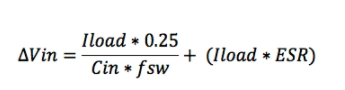

确定输入电容量的一个很好的起点是指定峰峰值电压纹波的目标电平,该目标电平与电容和开关频率成反比,但与负载电流和ESR成正比:

对于降压稳压器,输入电容器的均方根电流要比输出电容器中的均方根电流高得多,前者是由其应力要求决定的,而在输出端,仅是最大允许负载纹波决定了电容的大小。电容器的最大允许均方根电流可以根据其最大功耗(由其外壳尺寸,ESR和可承受的温升得出)来计算。

通常,并联使用各种不同的电容器以最小化ESR和ESL对输入纹波以及电流共享的贡献,以确保可靠的工作。根据零件的额定纹波电流,工作电压,自发热,ESR和ESL选择零件,并使用多层陶瓷,因为它们的寄生系数低。因此,观察到的纹波几乎完全归因于实际电容,因此必须注意热和直流偏置对电容器值的影响。对温度不太敏感的电介质通常用于最小化电容的变化。温度越高,包括寿命在内的可靠性越低。

设计降压稳压器时,需要权衡很多:较高的开关频率可降低输入和输出电容器中的纹波电压电平,并减少DC-DC所需的电容量。但是,减小后者会增加电压纹波的幅度,而以更快的速率进行切换则会增加交流损耗,从而影响效率。还存在优化的机会,例如,对于给定的电压纹波目标,如果增加开关频率以使用较小的能量存储组件,则可以减小电容。

较小的电感具有较低的DCR,可改善瞬态响应,并且对于给定的瞬态性能,所需的输出电容也较小。较大的电感导致较低的纹波电流,因此等效输出纹波所需的电容较小。

如果超过电感的饱和电流,其电感将下降,从而增加纹波电流:电感下降30%将使纹波电流增加40%以上,并使磁芯饱和。屏蔽电感器可降低EMI和潜在干扰,但由于制造成本增加,价格稍贵。屏蔽会降低饱和电流,从而降低最大允许均方根电流。Lsat也随温度而变化!

直到下个月,第一个告诉我0603和0805尺寸MLCC的最大功率消耗的人将赢得“火箭科学家世界巡回赛T恤”课程。恭喜来自加拿大多伦多的戴夫(Dave),第一个回答我上一篇文章中的谜语的人。

Rajan Bedi博士是Spacechips的首席执行官和创始人,该公司设计和制造了一系列先进的L至Ku频段,超高通量板载处理器和应答器,用于电信,地球观测,导航,互联网和M2M / IoT卫星。

编辑:hfy

-

开关稳压器的工作原理和元件选择准则2023-11-15 404

-

什么是开关稳压器?开关稳压器的控制方式2023-09-25 2034

-

DN48-无设计开关稳压器5V,5A降压(降压)稳压器2021-05-08 1090

-

单片式开关稳压器具备额外的 EMI 优势2020-10-05 2689

-

无设计开关稳压器5V 5A降压稳压器2019-08-01 1361

-

无设计开关稳压器5V降压 - 升压(正至负)稳压器2019-07-26 1440

-

线性稳压器还是开关稳压器,你的工业传感器供电选择哪个2019-03-11 2086

-

线性和开关式稳压器 ,究竟是如何工作?2019-02-18 2339

-

怎么选择线性稳压器与开关稳压器2018-10-24 3873

-

工业传感器供电采用线性稳压器还是开关稳压器?2018-10-10 2525

-

线性稳压器与开关稳压器的联系和区别2018-10-09 3679

-

线性稳压器与开关稳压器有什么不同2018-09-29 4678

-

集成电感转换器模块和线性稳压器的选择2018-08-30 1776

-

线性稳压器与开关稳压器的比较2011-07-09 3766

全部0条评论

快来发表一下你的评论吧 !