高级封装技术:创建接近单片互连性能的封装上互连

描述

在过去的几年中,已经发布了许多涉及用于半导体器件的高级封装体系结构的公告。这些架构为产品设计人员提供了极大的灵活性,使其能够异构集成在封装上不同硅工艺上优化的不同IP,从而显着提高性能。

对高级封装的最近兴趣是由对增加封装上带宽的需求,对来自多个代工厂的各种IP进行集成的需求以及对提高产量弹性的需求所驱动的。有机封装是出色的异构集成主流平台,可在紧凑的外形尺寸中实现空间转换,并在物理上实现了封装上的互连(电源效率高,带宽高)(图1)。

图1英特尔Agilex FPGA提供了一个封装上异构集成的示例。资料来源:英特尔

先进封装的目标之一是开发越来越密集的横向和纵向互连,以使用这些互连创建的管芯到管芯链接具有最小的功率损耗和延迟,同时又能确保信号完整性。本质上,重点是创建接近单片互连性能的封装上互连,并且在封装上创建的复合设备的行为就像一个虚拟的单片实体。

2D和3D架构

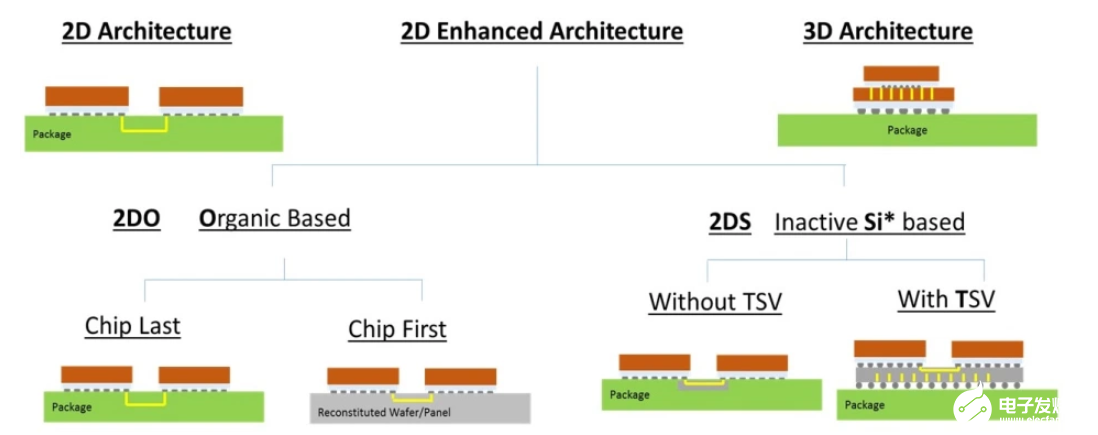

封装上互连以及具有这些互连的更广泛的封装体系结构可以在封装的xy平面中分为2D和3D(图2)。

图2 2D和3D架构的互连术语。资料来源:电子封装协会,IEEE

2D架构定义为两个或更多有源硅器件并排放置在封装上并在封装上互连的架构。如果互连是“增强型的”(互连密度比主流有机封装更高,并且可以使用有机介质完成),则该体系结构还可以进一步细分为2D有机(2DO)体系结构。同样,如果增强型体系结构使用无机介质(硅,玻璃或陶瓷中介层或桥接器),则该体系结构进一步细分为2DS体系结构。

3D架构被定义为两个或更多有源硅器件在没有封装代理的情况下堆叠并互连的架构。在此定义中,短语“在没有封装代理的情况下互连”仅表示有源硅片之间的互连不通过封装,因此它们的设计和性能不直接取决于封装体系结构。

互连密度

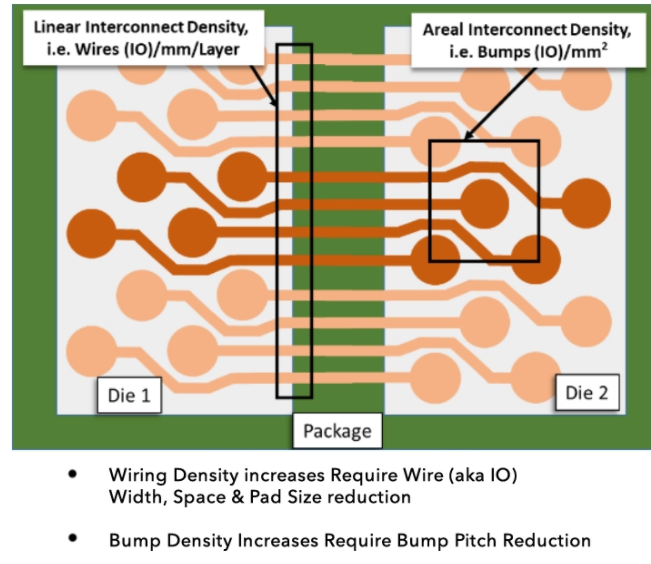

物理互连密度可以通过两个关键指标来捕获(图3)。线密度表示从芯片边缘向外逃逸的导线数量,以进行侧向的芯片到芯片互连,而面密度表示用于形成垂直连接的凸块数量。

图3可以通过这两个关键指标来捕获线性和区域互连密度。资料来源:英特尔

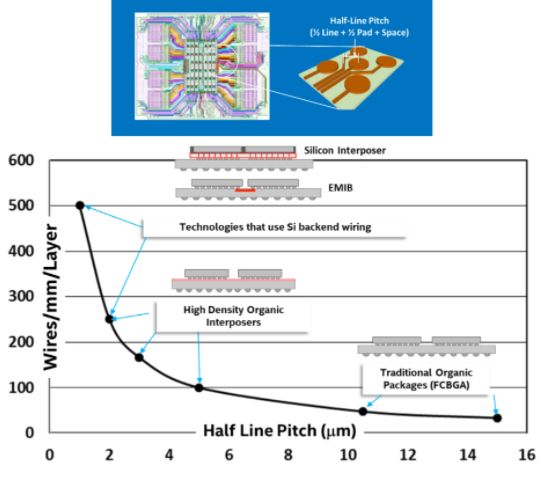

图4和图5描述了不同包装技术的线性和平面密度的包络线。如两个图所示,使用不同的互连体系结构,可以实现广泛的互连密度。通常,使用硅后端布线的技术具有最高的布线密度,因为它们提供了更细,间距更紧密的布线(图4)。

图4该图显示了不同高级封装体系结构的线性互连密度包络。资料来源:英特尔

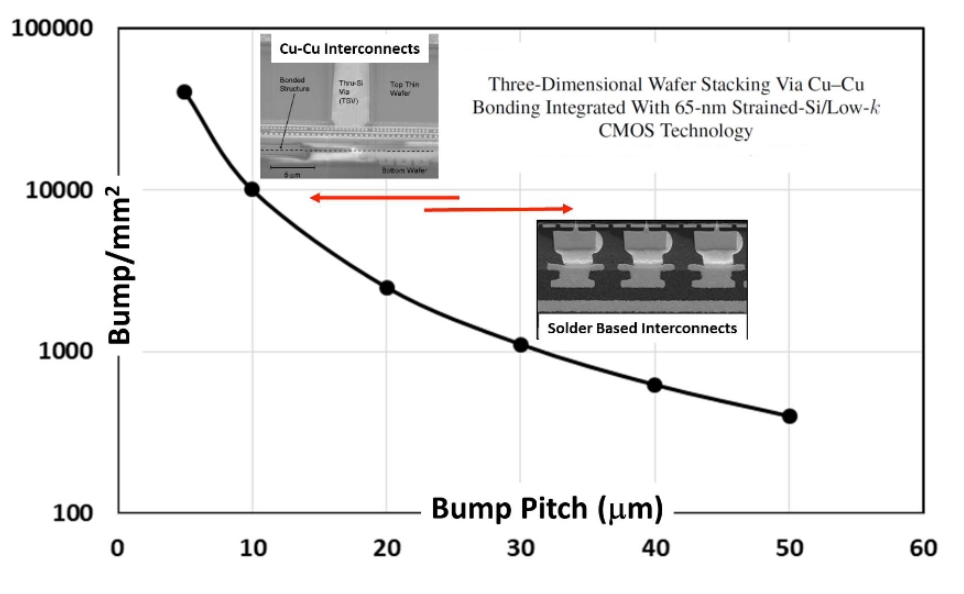

这些技术可以实现并行,宽且缓慢的芯片到芯片链接,并且需要特别注意链接设计,以解决布线密度增加带来的信号完整性问题。随着凸点间距的缩小,平面的凸点密度与凸点间距的平方的倒数成正比(图5)。

图5该图显示了面积互连密度与凸块间距和架构的关系。资料来源:英特尔

如今,大多数面积的芯片到芯片和芯片到封装的互连都使用焊料来形成接头。随着凸点间距的缩小,从焊料到使用Cu-Cu互连(约20-25μm)将有过渡,以实现持续的互连密度缩放。因此,工业上的重点是增加Cu-Cu互连的技术范围。

互连密度缩放的一个常见的根本原因是需要增加封装上裸片到裸片链路的带宽。带宽缩放速率可用于定义互连缩放路线图。根据《异构集成路线图2019年版》,互连技术扩展路线图可实现链路带宽的世代加倍。

图6显示了用于异构集成的高级包装体系结构的一些示例。

图6一些先进的软件包体系结构在所有三个维度上提供了更多的分区机会和规模扩展。资料来源:英特尔

软件包与系统设计师之间的协作

随着高级包装技术的发展,它们将通过异构集成提供更高的包装性能,从而使性能越来越高的系统成为可能。通过加强包装和系统设计人员之间的协作伙伴关系,可以更好地实现此系统性能。

下面列出了一些合作伙伴关系将如何帮助最大化系统性能的示例:

系统板的功能,材料和设计必须不断发展以支持更高的速度和更高的带宽信令。封装和系统协同设计方法可创建功耗最大化,成本优化的系统链接,从而最大程度地提高带宽,从而有助于最大化系统性能。

可以预见,除了电气链路之外,将来还将需要光子学和无线链路以最大程度地扩大覆盖范围和带宽。开发和扩散这些不同的信令技术将需要协作以实现标准化的模块化可扩展性。

将需要专注于开发有效的系统电源传输网络。

符合系统尺寸和可靠性要求的整体系统冷却方法将确保系统冷却能力不会限制系统性能。

模块化和可伸缩性将需要在系统级别使用的各种连接器技术中构建。

总之,当今有许多先进的包装技术可用来提高包装上异构集成IP的性能。这些技术着重于扩展互连密度,以帮助扩展封装上芯片对芯片链接之间的带宽并提高性能。软件包与系统设计人员之间的紧密合作,以优化软件包系统集成,将有助于最大化系统性能。

RAVI MAHAJAN,英特尔研究员,是技术发展的组装和测试未来技术的英特尔共同主任。

编辑:hfy

-

半导体封装革新之路:互连工艺的升级与变革2025-02-10 2142

-

芯片和封装级互连技术的最新进展2024-10-28 2251

-

互连在先进封装中的重要性2023-11-23 1568

-

一文详解封装互连技术2023-04-03 8408

-

一文详解半导体封装的封装互连技术2023-02-20 2653

-

Telechips在高级汽车应用中选用Arteris FlexNoC互连技术2022-12-14 1208

-

封装工艺流程--芯片互连技术2022-12-05 2488

-

IGBT功率模块封装中先进互连技术研究进展2022-05-06 1016

-

可穿戴设备推动封装与互连技术的超越发展2016-08-09 2321

-

光互连技术2016-01-29 2844

-

芯片封装键合技术各种微互连方式简介教程2012-01-13 39104

-

电子封装微互连中的电迁移2011-10-26 1038

全部0条评论

快来发表一下你的评论吧 !