关于一个一个等时不等长的DDR设计

电子说

描述

关于DDR的设计,经历过无数项目历练的攻城狮们,肯定是很得心应手的。对于信号质量方面的改善,相信大家应该已经有自己的独门技巧了。同组同层,容性负载补偿,加上拉电阻等等,总有一款适合你的DDR。但是对于时序方面的控制,理论上只有一个办法——绕等长,速率越高的DDR,等长控制越严格,从±100mil,到±50mil,甚至±10mil。

本来我们的layout工程师也是在这样一条路上稳步前进。但是最近有个DDR4的项目,绕好了等长,如下图所示,一切都安排的明明白白之后,给SI工程师仿真,只等仿真结果一出来就gerber out,根本不用怀疑,信号质量肯定妥妥的,没问题。

结果,SI工程师没有同意投板,却提出了不合常理的时序要求,如下图所示:

等长要求CS,CKE,ODT这些信号比其余CMD信号每段长120mil,按照这样来算的话,到U1这个位置,长度差就到了600mil。这和设计指导不一样。

瞬间感觉自己很委屈,这样的等长到时候地址控制线之间的延时会相差100ps左右,这样时序的margin就会变小,甚至可能跑不到要求的2400Mbps,于是硬气的提出了自己的质疑。

SI工程师也知道这种情况下,应该和设计人员普及一下关于时序方面的知识,不然后续遇到类似的DDR,不做仿真的话,可能会需要降频运行。于是将U1的仿真结果给设计人员看,蓝色的是CS,ODT,CKE等信号,绿色是其他的CMD信号,从时间上来看,蓝色的比绿色的信号快90ps左右。

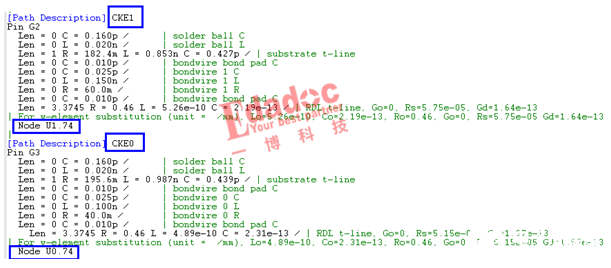

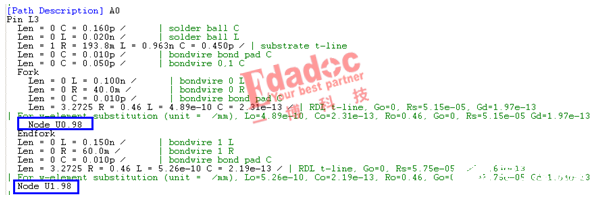

这种情况的原因不是因为设计人员的误操作,或者不同层的时序不一致,也不是像上次文章中提到的层叠中的DK设置不一样,而是因为DDR颗粒的选型导致的,如下面图片所示:

这款SDRAM的CS,CKE,ODT为单DIE结构,但是其他的信号却是双DIE结构,在封装中做T型拓扑,这样意味着双DIE的信号的容性更大一些,那么相应的上升沿会更缓一些,这个是比较好的影响,这样的话,信号质量会比较好,从图中的结果也可以看出来,绿色信号的振铃比较小。另一个影响是容性更大,意味着时延会更慢一些,所以相同等长的情况下,由于颗粒内部拓扑的影响,导致CMD信号会传输的更慢一些,体现在仿真结果中,自然是双DIE信号和单DIE信号会有不一样的上升沿和一定的延时差。

layout工程师恍然大悟,这是因为颗粒内部的结构和常规设计不一样导致,自然不能沿用常规的设计指导,以后遇到这种双DIE的DDR还是需要仿真之后再调整等长,不然可能会出问题。于是很愉快的按照上面的时序意见修改了版本,结果如下,后期客户反馈,DDR2400跑的飞起,一版成功。

编辑:hfy

-

AD设计DDR3时等长设计技巧2025-07-28 689

-

串口接收不等长的数据如何处理的呢?2024-05-15 416

-

使用Swift语言一个一个地闪烁RGB LED2022-11-10 802

-

关于DDR4的绕等长,您想知道的这本书上都有2022-09-19 1683

-

速率越高的DDR4,等长控制越严格?2022-09-13 2095

-

【驱动】一种中断接收的不等长不规则uart数据机制2021-11-16 576

-

一个allergo自带的绕等长AiDT功能2020-06-23 6299

-

cc2541一个主机能一个一个的连接从机?2020-03-19 1550

-

一个等时不等长的DDR2019-06-20 1315

-

DDR怎么学习,从仿真开始2018-09-15 6934

-

关于Altium Designer使用等长布线问题2018-05-22 19951

-

DDR等长线与过孔的问题2015-06-18 13869

-

关于ddr3等长控制的8个问题2015-01-06 14702

-

关于单形体积的一些不等式2008-11-20 720

全部0条评论

快来发表一下你的评论吧 !