超过100MHz的高频电源纹波超标是否会影响高速信号产生干扰

描述

高速先生经常被问到这样的问题:信号速率早已达到了Gbps的量级,为何电源仿真报告里的PDN阻抗(如下图示红色曲线,横坐标的单位是MHz)大部分还只看到100MHz?超过100MHz的高频电源纹波超标肿么办?不会对高速信号产生干扰吗?

先回答最后一个问题,高频段的电源纹波超标当然会对高速信号产生干扰,不过,大多数时候只关注百兆赫兹内PDN阻抗的做法也是没问题的,是不是有点晕?

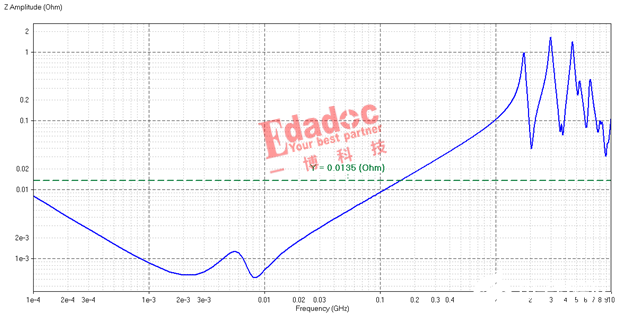

其实,仿真攻城狮只让你看到100MHz也是为了你好,因为根据板级电容配置的阻抗特点,高频段的PDN阻抗(如下图蓝色阻抗线,注意,横坐标的单位是GHz)在你看不到的频段里(高于100MHz)放飞了自我,远远超出了目标阻抗(如下图绿色虚线0.0135ohm)的要求,怕你看到会上火。

如果你坚持要看更高的频段,你会看到这样的景象:板级电容的PDN阻抗随着频率增加而一路飘高,阻抗曲线在高频段的抖动比你此刻的心电图还厉害。我猜你会怒不可遏的揪住仿真攻城狮的领子咆哮:老子按芯片手册加的电容,怎么会跑成这个鬼样子?!

电容数量没错,容值没问题,封装大小也没毛病,跟Layout攻城狮说了很多好话,他加的也很辛苦,大家都了解,可是板级电容的PDN阻抗随频率增加的变化趋势就是这样的,因为高频段的电源去耦不归你加的这些电容管。

结论确实很残酷,让你出离了愤怒,你可能需要时间接受。但是,如果高速先生告诉你,PDN在高频段的实际阻抗并没有你看到的那么糟,因为PDN系统级的去耦除了板级电容,还要考虑封装内电容去耦(OPD,On-Package Decap)和片上电容(ODC,On-Die Caps),看到这里,你会不会先松了一口气,继而又觉得很茫然?

在解决你的困惑之前,让我们先回到最基本的问题,搞懂电源去耦设计中的目标阻抗是怎么回事?所谓目标阻抗(Ztarget),即在满足负载最大瞬态电流需求、且电压变化不超过最大允许波动范围(Allowed ripple)的情况下,电源分配网络(PDN)自身阻抗的最大值。简单来说,就是通过合理的电容配置,在尽量宽的频段内保持PDN的阻抗低于目标阻抗,从而使电源的纹波满足要求。计算公式如下:

芯片手册推荐的电容配置通常会把电容的数量、容值、封装、品牌甚至Layout指导都给你安排的明明白白的。

综合考虑板上不同容值的电容在不同频段的去耦作用,板级电容整体的PDN阻抗通常长成下图红色曲线的样子。

重点来了,前文一直聊的是板级的PDN阻抗,而系统级的PDN阻抗,除了板级,还包括芯片封装内的部分。问题的关键就在于板级电容和芯片内的去耦频段各有侧重。

具体说来就是,直流至百KHz左右的频段主要依赖电源输出模块(VRM)的稳定性;百KHz到百MHz的频段靠板级电容(PCB Caps,包括Bulk caps及Local caps)进行去耦,虽然不同容值的电容负责不同的频段,但整体由于安装电感的影响,板级电容的去耦频段一般局限在百MHz以内;更高频段的电源去耦则通常在芯片内部完成,主要依靠封装内的电容及片上电容,而这两个电容参数涉及芯片内部的构造,一般需要芯片厂商提供。

困惑你的两个问题终于有了答案:第一个问题,大部分的电源仿真报告里的PDN阻抗只看到100MHz,是因为你所提供的板级电容配置只能在百MHz之内的频段起作用,部分芯片由于封装内的电容去耦比较给力,甚至只要求封装外的板上电容只负责20MHz以内的频段(具体要参考芯片手册);第二个问题,高频段的电源噪声肿么办?主要依靠封装内的电容去耦和片上电容的作用。比如,下图所示的某芯片电源在考虑厂商提供的OPD和ODC前后的PDN阻抗曲线对比。可以看到,考虑了芯片内的电容参数之后,红色的PDN阻抗曲线在高频段被控制在合理的范围之内并一路走低,形势可喜,令人欣慰。

编辑:‘hfy’

-

如何通过日常数据判断电源纹波是否超标?2025-09-23 1423

-

你的电源纹波超标了吗?3步精准测量法+避坑技巧2025-02-26 2595

-

如何判断电路是否为高频电路2025-01-20 1704

-

TPA6139A2内部电源是否用开关升压电路?这样是否对88MHz--239.2MHz会产生干扰?2024-10-23 490

-

想把1V(100MHz)的信号放大成100V(100MHz)的信号,请问应该选什么型号的芯片?2023-11-24 737

-

音频信号如何与AD9910的DRG工作模式产生1.5MHz~100MHz的调频信号?2023-11-17 627

-

电源噪声怎么产生的 电源噪声和电源纹波的区别2023-08-03 1353

-

转贴,揭秘!百兆赫兹的电源去耦如何hold住Gbps的高速信号2020-03-18 1432

-

怎么在PS中产生100Mhz的时钟信号在外部被PL接收2019-02-22 2971

-

高速电路的抗干扰设计2018-09-12 2607

-

关于3.3V电源线上100Mhz空间辐射超标问题2016-04-26 25531

-

100MHz触发时钟2014-12-09 2259

-

开关电源纹波的产生与抑制2012-11-04 18859

-

100MHZ混频器电路2008-06-12 2614

全部0条评论

快来发表一下你的评论吧 !