基于CPLD控制的直流固态功控系统的研究与设计

描述

1、引言

随着电子技术和计算机技术的迅猛发展,国内开展先进飞机配电系统研究的技术手段已比国外八十年代好得多, 对固态功控系统研究,就是基于目前飞机配电系统的发展应运而生的,目前市场上的均为单开关结构,最近多开关的 SSPC 组已经处于研发之中,SSPC 组共享大规模控制芯片,可进一步提高功率密度和扩展功能。现在国外对进行研究的公司有美国的印和立奇等,国内对的研究处于工程样机阶段。

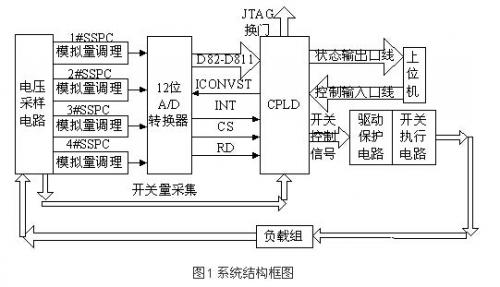

2、系统总体结构框图

如图 1 所示,每路 SSPC 取样电阻上的电压经过调理电路和低通滤波器以后,送到 4 通道 A/D 转换器的一个模拟输入端,A/D 转换器的数据输出端、状态信号和控制信号分别接到 CPLD 的 I/O 引脚,便于程序控制 A/D 转换器的动作。CPLD 另外的 I/O 口可以配置为 MOSFET 的开关命令输出口线、SSPC 的状态输出口线和与上位机相连的控制命令输入口线;CPLD 自身提供的 JTAG BST 电路,可以方便的测试系统内部器件之间的连接和检验器件的操作。

3、硬件设计

3.1 逻辑控制器件

根据设计要求,需要集成多个 SSPC 在一块电路板上,如果完全用分离元件来实现,数字电路的体积相当庞大,因此我们采用复杂可编程逻辑器件 -CPLD。ALTERA 公司的可编程逻辑器件在工业界是最快和最大的,该公司的 PLD 器件不仅具有 PLD 的一般优点,而且还有如下一些优势:高性能、高集成度、价格合理、开发周期较短和利于编程。

根据软件所需要的资源,逻辑主控芯片采用 ALTERA 公司的 MAX3000A 系列芯片中的 EPM3256ATC144-10,相对于 MAX7000 系列,MAX3000A 系列的 I/O 电压为+3.3V,而 MAX7000 系列的 I/O 电压为+5V,一般来说,对于控制信号的输出,+5V 电压可靠性高些,但是低电压、低功耗是以后的发展趋势,并且也利于以后的换代产品的设计,而对于可靠性的考虑可以通过加强外围电路的设计来达到系统设计的要求。

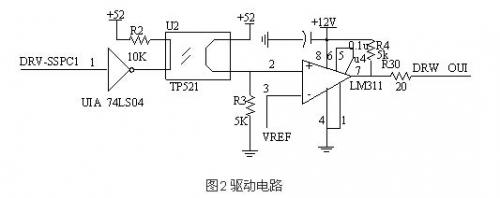

3.2 电力 MOSFET 的驱动电路

控制命令经过光耦隔离输出后,接到比较器 LM311 的正相输入端,比较器的反相输入端输入的是参考电平 Vref,取 Vref=3V。当 DRV_SSPC1=1 时,光耦输出高电平,比较器正相输入端电压大于反相输入端电压,比较器输出 DRC_OUT 为高电平:当 DRV_SSPC1=0 时,光耦输出低电平,比较器正相输入端电压小于反相输入端电压,比较器输出 DRC_OUT 为低电平;比较器的输出端接低值电阻 R30,目的是与电力 MOSFET 的 G 极和 D 极间寄生电容构成一定时间的阻容延时,保证 MOS 管的导通时间不至于太快或太慢,减小寄生振荡,该电阻值应随被驱动器件额定电流值的增大而减小。

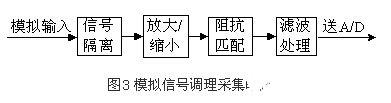

3.3 信号采集电路

1、模拟量采集电路。信号采样!调理的方块图如图 3 所示。模拟信号经过隔离电路,得到取样电压,经过一定比例的放大,通过跟随器进行阻抗匹配,最后经过滤波处理,滤去信号中的交流分量,得到的信号就可以送到 A/D 转换器的模拟输入端。

需要模数转换的模拟电压信号为直流电压信号,范围大概在 0V-7V 之间,由于 SSPC 在电路中是用来作为负载的一个开关保护措施, 因此,要求其动作时间尽可能的快,细化到电路的每一个环节,就要求 A/D 转换器的转换时间尽量小,在 A/D 的转换精度和转换时间之间权衡,得出一个折中的方案。经过对比,采用 AD 公司的 12 位的 A/D 转换器 AD7874,这是一款 4 通道同时采样,12 位快速低功耗的 A/D 转换器,内部包括一个 12 位高速模数转换器、片上时钟和四个采样 / 保持器。这样,避免了四个输入通道共享一个采样 / 保持器所带来的问题一通道间采样出现相位差。

2、开关量采集电路。开关量主要有两个:表示负载状态的 STA_LOAD 和表示电力 MOSFET 状态的 STA_SSPC。规定:当负载的电流大于 SSPC 额定电流的 15%时,表示负载状态的开关量 STA_LOAD 为低(0);当 MOSFET 处于导通状态时,表示 MOSFET 开通关断状态的开关量 STA_SSPC=1。通过对 CPLD 采集到的 A/D 通道的数据进行判断:当 i_load 大于负载电流的 15%时,表明负载导通,置 STA_LOAD0;当 i_load 小于负载电流的 15%时,表明负载不工作,置 STA_LOAD 为 1。STA_LOAD 通过 CPLD 的 I/O 口输出。

3、I/O 驱动与隔离电路设计。CPLD 与外围器件接口时,应考虑驱动能力,在中间添加驱动器和隔离器件,以保护 CPLD 不受损害。因为比较器是 12V 供电,所以出来的状态量信号为 12V 信号,而逻辑判断模块的 CPLD 是 3.3V I/O 供电和 2.5 V 内核供电,因此对 SSPC 状态信号的采集和控制信号的输出都需要经过电平转换和电气隔离,具体采用光耦隔离的方式,既实现了电气隔离,又实现了电平转换。当控制信号从 CPLD 输出时,因光耦的驱动电流相对较大(20mA 左右),如果直接从 CPLD 输出来驱动,就会使 CPLD 因电流太小而无法驱动,因此实际中采用六通道反相器 74HC04 来做光耦前一级的驱动。而对输入 CPLD 的信号,因为是从光耦输出来的,电流一般不大(Ic《5mA ),所以可以不用反相器来驱动。

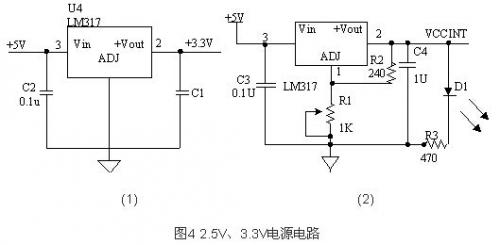

3.4 电源电路

在目前的实验系统中,SSPC 的供电由市电经变换得来。它所使用得电源种类较多,包括 2.5V, 3.3V, +5V,-5V, 12V 等。其中,2.5 V 为 CPLD 核心所使用的电源,CPLD 的 I/O 引脚需要使用 3.3V 的电源,+5 V 电源用于一些外设器件和参考标准,12V 电源主要用于运算放大器和比较器。3.3V 和 2.5V 电源都是由 5V 电源变换得到的。5V 和 12V 则采用了 ANSJ 公司生产的 AC/DC 电源模快得到,这类电源使用简单,具备高功率、高效率、宽输入范围、低噪声、可靠及应用简易等优点,且结构紧密,具有优良的输出编程和低待机损耗等特性,具备输出过压保护及过温关机功能。图 4 是 5V 转 2.5V 和 3.3V 的电源电路,采用了输出电压连续可调的器件 LM317。它可以提供高达 1.5A 电流,而且电压调整方便,非常适合 CPLD 的供电要求。如图 4 中的 2 图所示,输出电压 VCCINT=1.25(1+R1/R2)+IADJR2。

4、可编程逻辑区设计

1、A/D 数据采集模块。利用状态机的概念,一个步骤对应一个状态,每个状态赋予 CPLD 特定的功能。将 AD7874 的工作大致分为 10 个步骤区间。AD7874 转换的量化噪声与输出位数和量化步长有关,输出位数越多,量化步长越小,则量化噪声越小。实际 A/D 转换器多为定点制,动态范围为±1,输出最大值为 1。如果只考虑量化噪声,则输入信号信噪比为

如果 AD7874 为 12 位,则 SNR=70dB 左右,在应用中一般已经足够,字长过长并不是非常必要,因为输入模拟信号本身有一定的信噪比,A/D 转换器的量化噪声比模拟信号的噪声电平更低是没有意义的。

2、开关量采集模块。上位机下传的控制信号,由于存在各种干扰,使得开关量在实验中经常出现抖动,另一方面,电路中经过比较器得到的开关量(如 STA _SSPC),由于主电路中的电流不稳定,偶尔出现电流过冲,使得送到 CPLD 的开关量信号也会出现抖动;这些都会导致 SSPC 经常误动作,为此,需要设计一个专门的开关量去抖动电路,降低 SSPC 误动作的概率。实际中采用的是延迟电路后级加上 R-S 触发器,具体的工作原理如下所述:先将输入信号先引至输入端,经过两级的 D 触发器延迟后,然后再通过 RS 触发器作处理。

3、整个数据分析过程包括以下几部分:

(1) 当电流在额定范围内,SSPC 正常工作;

(2) 电流大于额定电压,小于额定电压的 800%时,SSPC 进入反时限保护;

(3) 当电流大于额定电流的 800%时,SSPC 立刻跳闸。

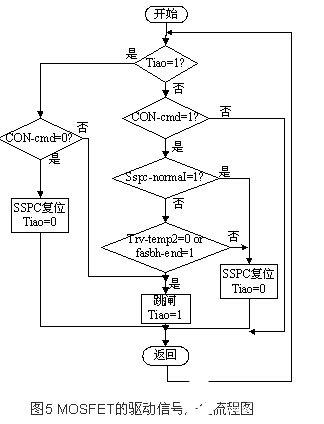

4、逻辑判断模块。逻辑判断模块将采集到的电流信号、接收到的控制命令和内部状态,经过逻辑判断后,综合得出电力 MOSFET 的导通 / 关断指令,作为驱动电路的输入信号。程序流程如图 5 所示。在对 SSPC 的控制中,最容易出现的问题就是误动作,为此,采用了较为复杂的控制逻辑,以此降低 SSPC 误动作的概率。SSPC 的控制是通过“相邻两位、多条指令”两个步骤来完成的,只有几个条件同时满足才能使 SSPC 动作,缺一不可,这就大大降低了 SSPC 误动作的概率。

本文作者创新点

本文基于 CPLD 控制的直流固态功控系统的研究与设计。完成了 SSPC 外围硬件电路设计,包括主控芯片和 A/D 转换芯片 MOSFET 主电路及缓冲保护电路的连接,模拟量采集电路,开关量采集电路,电源电路等;完成了 CPLD 上可编程逻辑部分的 VHDL 实现,包括 A/D 转换器的控制,电流的分段保护,SSPC 动作命令判断逻辑的生成等。

-

基于CPLD的SPI控制器的研究与实现2013-04-27 2632

-

交直流固态继电器使用注意2014-02-13 4007

-

直流固态继电器的问题,求指点2014-05-12 4790

-

如何利用CPLD实现直流固态功率控制器的设计2021-04-30 1574

-

求一种直流固态功控系统的设计方案2021-05-06 1241

-

怎么实现基于DSP芯片和CPLD的刹车控制系统设计?2021-05-12 1351

-

基于CPLD的频率键控系统设计的研究2009-06-19 495

-

一种多开关结构的固态功控系统的开发2009-07-30 465

-

一种多开关结构的固态功控系统的设计开发2009-12-30 663

-

异步电动机控制系统开发平台设计研究2011-12-12 743

-

CPLD在固态高功放控制检测单元中的应用2016-01-04 503

-

基于DSP的直流无刷电机控制系统研究2016-05-05 703

-

PC机与CPLD通信问题的研究2017-01-19 784

-

直流电机CPLD 控制程序设计2021-09-16 1093

-

固态继电器直流控交流原理是什么2024-06-21 4622

全部0条评论

快来发表一下你的评论吧 !