PCB设计应用:电容的作用

描述

对于模拟电路没学好的工程师来说,电阻只知道用来端接;电感只知道用来隔离;至于电容嘛,估计你们只知道滤波,更不用说它们的组合产生的作用了。不信?估计以下这个电容的用法,你也只能说滤波了吧……

上周我们雷工,哦不是,是我们姜工的文章向大家介绍了DDR的时钟里面并联电容的用处,让大家惊奇的发现了原来电容也可以用来端接,可能已经让一大把粉丝获得了一波知识的源泉。那么本期高速先生还继续玩这个DDR的时钟,去深挖它还有什么槽点。

我们先把上周所讲到的这个DDR时钟的拓扑再一次拉出来,没错!就是下面这个图啦。其中上周让雷工尴尬不已的这个电容就是下面红色圈圈的那位了。把电容并联到差分对间,能够很好的对发送的信号进行端接,目标是使得电容的电抗值和传输线接近,从而起到源端端接的效果,减小时钟的反射。

恩,这个是上篇文章的精华哈。那么我们这期的文章继续研究这个拓扑,大家有没有发现上面的拓扑其实不止一个电容,看看上图蓝色圈圈的位置,其实还有一个电容哦!它一般是放在最后两个端接电阻之间,然后下拉到地(也可以上拉到DDR电源)。这个电容到底有什么用呢?根据高速先生对你们的认识,都接到地了,肯定又是用来滤波啦?

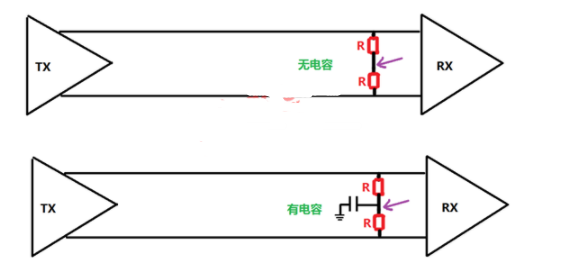

高速先生对此也研究了一番,我们用一个简单的点对点的时钟拓扑进行验证哈。

如果这对差分线是理想的走线,所谓理想就是差分线的P和N长度一致,阻抗相同,分成对称的情况下。有无电容的结果是下面这样的。

是的,如果我们的PCB加工出来就像原理图设计一样是理想的情况,那这个电容的确起不了什么作用。但是我们PCB最精彩的地方就在于它的设计和加工的误差哈。我们知道,对于一对差分线来说,对间P和N的对称性是最为重要的事情,不然的话它们就是产生共模的噪声。基本上来说,只要破坏了差分线理想状态,这对差分线都会或多或少产生共模的噪声。那么我们在有共模噪声的情况下再去进行对比验证,结果就会变得不一样了。

可以看到,没有了这个电容之后,接收端的波形变得扭曲,甚至是产生了非单调的结果。那么大家也许会问了,那你们怎么知道是不是共模噪声的影响呢?怎么看呢?

我们可以看下图紫色箭头位置的波形,也就是它们产生的共模噪声的位置了。

我们可以看到,当差分线有共模噪声的时候,这个电容其实可以为我们抑制很大部分的噪声,因此能最大限度的还原接收端信号的完整性。

当然如果旁边的走线离这对时钟很近的话,有了这个电容,自然也能使得共模噪声串扰到旁边走线的能量削弱啦,也就是起到减小串扰的效果。

编辑:hfy

-

PCB设计为什么电容要就近摆放?2023-10-20 2430

-

去耦电容PCB设计和布局详解2023-07-05 2436

-

PCB设计时电容如何摆放?2023-05-29 8853

-

高速PCB设计电容的应用.zip2022-12-30 571

-

PCB设计中的Grid布局的作用2022-11-29 1937

-

PCB设计 PCB设计用什么软件2021-07-21 7325

-

PCB设计电容中必须要知道的知识点2020-08-12 8431

-

PCB设计之电容2019-08-13 3749

-

PCB设计中滤波电容布线的技巧和方法2019-04-29 12780

-

高速PCB设计电容的应用 5页 0.3M2016-12-16 543

-

高速PCB设计电容的应用2014-10-24 2745

-

电容在高速PCB设计的应用2012-08-14 2739

-

电容在高速PCB设计中的应用2009-08-16 796

全部0条评论

快来发表一下你的评论吧 !