设计同步整流电路时SR的连续导通模式解析

描述

作者:Zhihong Yu,Walter Yeh

近年来,为了进一步改善全球节能,全球监管机构提出了新的效率标准。随着美国能源部(DOE)出台的一系列新要求,制造商必须提高现有独立电源产品的效率以达到DOE VI级标准,才能在美国市场销售。此外,制造商还需要设计符合其它能源规格的产品,例如欧盟CoC V5Tier2规格。

为了提高交流转直流适配器的效率,将输出续流肖特基二极管换成基于MOSFET的同步整流控制器(SR)时通常可提升2〜3%或者更高的效率。还有发现使用SR有助于节省二极管散热片成本和人工组装的成本,设计人员还可以使用更便宜的初级MOSFET或者更细的输出线缆来节省成本,且依然能达到目标效率。

因篇幅所限,本文无法涉及SR设计的全部细节,而精选了几个在工程师设计同步整流电路时一些实际的话题用以讨论。

SR的连续导通模式(CCM)

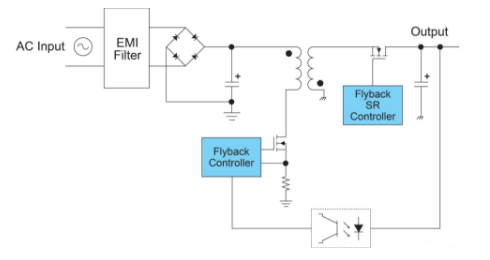

在图1中,反激式SR控制器用于驱动AC / DC适配器中的次级MOSFET开关。这里,反激控制器可以在临界导通模式(CrM),连续导通模式(CCM)或断续导通模式(DCM)下运行。

图1:快速充电器中使用的反激式电源的典型框图

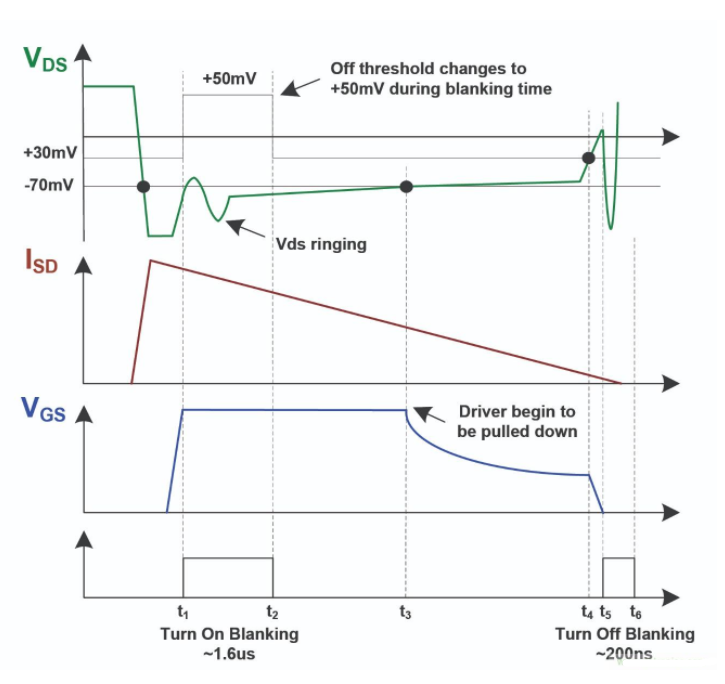

适配器在启动或满载的状态下是以CCM模式运行,在主开关试图导通时,SR开关中的电流被设置不能降至零。因此,需要防止初级侧到次级侧的击穿而导致高压尖刺和潜在损坏,而因此需要快速地关闭SR。MPS的解决方案是调整SR开关VG电压来保持MOSFET的VDS恒定。随着在CCM模式期间电流的下降,驱动器的VG电压也随之下降,直到MOSFET运行在线性工作区(见图3)。因此,当电压最终反向时,驱动器会基于很低的VG电压来快速关断,以此来确保在CCM模式下安全运行。因为它不受线路的输入条件的影响,因此这是一种稳定的控制方法。此外,通过最大化SR MOSFET的导通时间和最小化体二极管导通时间,可确保最佳的效率。MPS的SR控制器不仅可以支持CCM模式,还可以支持DCM和CrM模式。

图2:CCM模式下初级和次级电流波形

有关MPS的CCM兼容模式下的SR设计和操作的详细说明,请参阅AN077应用笔记。1.

在CCM模式下和CrM模式下MOSFET封装电感的影响

次级电流切换时总会有一些开关上升/下降时间(如图2所示),由输入/输出,变压器匝数比和电感来决定。MOSFET封装电感也会影响次级电流的关断。

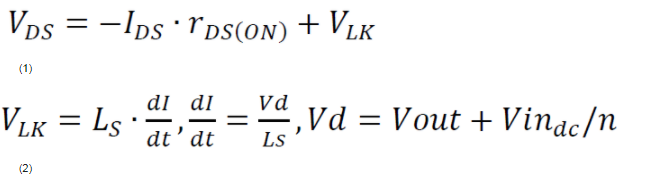

随着次级电流开始改变极性并关断(图4中的t1),MOSFET封装电感(Ls)会在检测到的Vds上产生瞬时电压,如公式(1)和公式(2)所示:

其中,dc是DC平均输入, n 是变压器匝数比,Ls 是漏感。

图3:MPS SR控制器操作原理

对于采用TO220封装的MOSFET,封装电感在100kHz频率时可高达6.4nH,而Vlk可以高达几百mV,达到SR控制器的关断阈值,使SR控制器关断门极( 从t1开始)。由于t1关断时间相对较早,因此稍高的封装电感有助于防止击穿,特别是在深CCM条件下。

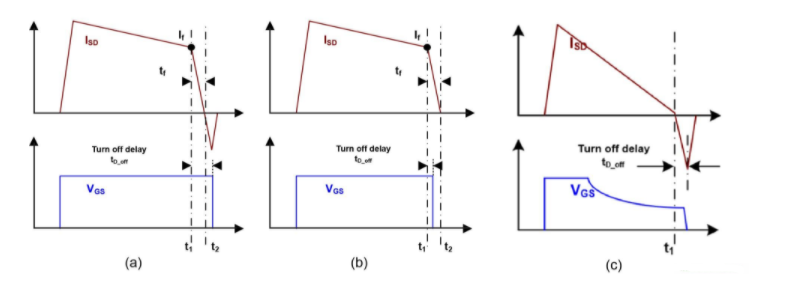

对于各种电路设计,我们可能会在CCM模式中看到不同的关断波形(参见图4a和图4b)。如图4a,电流降至零,但SR并未完全关闭。因此,交叉传导可能发生并会反映在反向电流中。而相对最佳的设计是SR能够在次级电流变为零(t2)之前关闭,如图4b。更值得关注的是,如图4c中所示,在CrM模式中,当副边电流几乎为零时,SR控制器随之关断,这意味着总是存在一个反向电流dI / dt * Toff。

当MOSFET的封装电感非常小时(例如QFN或SOIC封装),SR门极相对关断会更延迟。即使在Vds调节控制下降低Vg,反向电流仍然大于具有较高封装电感的MOSFET。这与主题1中介绍的Vds控制无关。

● 选择Qg非常低的SR MOSFET(以加速关断)。

在SR MOSFET上增加一个RC snubber 吸收电路(以吸收反向电压尖峰)。使用具有高关断电流的SR控制器。增加变压器漏感以减慢关断时的次级电流dI / dt(但会导致更高的初级MOSFET电压尖峰)减缓初级MOSFET导通时的上升斜率(损失效率)。使用具有较高Vds控制电压的SR控制器(图2中使用MPS的MP6902为70mV)。在较高的Vds控制电压情况下,MOSFET可以进入更深的线性区,在开关关断之前Vg就达到很低的水平,从而快速关闭。

振铃—优点与缺点

当MOSFET导通和关断时,PCB布局和系统中产生的离散电感与元器件中的寄生电容会导致一些振铃。如果不能适应振铃造成的影响,轻则可能会使效率降低,重则会导致一些致命的问题。

振铃引起的问题如图4所示。当次级电流下降到零时,初级开关电压Vds在变压器的主电感和MOSFET Cds之间会产生谐振,这个谐振电压会折射到次级侧。通常,这个谐振谷值不应该会接触到地平面,但有时谐振谷值可能会下降到SR的导通阈值。这可能是因为诸如原边RCD缓冲器中二极管的反向恢复等因素引起的。

由于Vds电压谐振的斜率总是远低于实际开关关断的斜率(得益于较大感量的主电感),因此MPS的MP6908使用独特的可调斜率引脚来帮助确定何时副边MOS真正关断,以及何时是正常的Vds电压谐振(如图4所示)。

图4:在消磁振铃期间潜在错误开启的SR波形

根据实际需要更换肖特基二极管

虽然SR的优势已经被广泛接受,但将肖特基二极管的设计改为使用SR驱动器和MOSFET的设计方案,仍然需要在BOM中增加许多元器件,并需要重新认证等工作。

另一种解决方案是将SR MOSFET集成到SR驱动器IC内部,创建紧凑的封装来替换肖特基二极管,而不需要对变压器进行任何更改,这个全新的设计使BOM变化最小(见图5)。这种解决方案被称为理想二极管方案。

MPS新型理想二极管的优点如下:

● 最小的BOM和电路板空间。

● 在高侧或低侧无需辅助绕组即可直接更换肖特基二极管。

● 优化的集成门极驱动器。

● 针对不同的功率等级和额定电压优化MOSFET。

● 灵活的SMT和通孔封装选项。

为什么MPS MP6908是适用于实际SR控制设计的选择?

MP6908是MPS最新的SR控制IC,而且未来将有一系列基于MP6908控制器创建的理想二极管方案。该控制器IC的一些主要功能包括:

● 不需要用于高侧或低侧整流的辅助绕组。

● 支持DCM,准谐振和CCM运行模式。

支持低至0V的宽输出范围(即使输出短路时,SR保持供电,短路电流也不会通过MOSFET的体二极管流通)。振铃检测可以防止错误导通。超高速15ns传播延迟和30ns关断延迟。

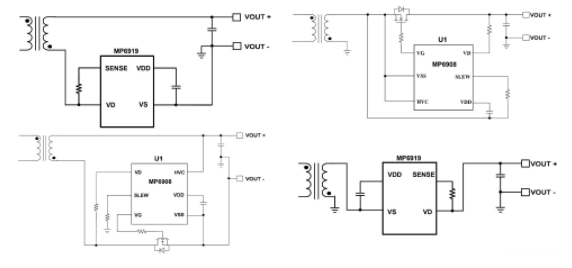

图5: MP6908控制器和低侧和高侧的理想二极管应用电路

总结

本文介绍了与实际工程情况相关的同步整流器(SR)设计。通过更多地了解终端应用,MPS能够定义和创建更好的SR控制IC。

1 MPS MP6902 Application note: http://www.monolithicpower.com/pub/media/document/AN077_r1.0.pdf?utm_source=mps&utm_medium=article&utm_campaign=content

2 https://www.fairchildsemi.com/application-notes/AN/AN-4147.pdf

编辑:hfy

-

飞虹MOS管FHP140N08V在同步整流电路中的应用2025-07-24 1181

-

同步整流电路带负载能力差的原因2024-07-22 2486

-

同步整流和非同步整流到底有什么差别呢?2023-10-31 2645

-

同步整流电路分析2023-10-08 659

-

开关电源同步整流控制的优势2022-10-12 28994

-

FAN6204—反激和正激续流整流的同步整流控制器2021-06-16 1352

-

全波整流电路与半波整流电路解析资料下载2021-04-12 1520

-

精密整流电路解析2021-01-14 3645

-

MPS flyback Top同步整流方案MP69082019-09-23 8403

-

【电路精选】整流电路2019-07-17 2998

-

同步整流驱动控制器NCP4305简介2019-06-17 5836

-

基于同步整流技术的DC-DC模块电源设计2018-11-28 2207

-

LLC单路/多路输出同步整流电路2011-11-30 6614

-

同步整流电路的逆流现象之研究2011-03-10 1059

全部0条评论

快来发表一下你的评论吧 !